CPU缓存设计的原则及工作原理

描述

本文将研究 CPU 缓存设计的原则,包括局部性、逻辑组织和启发式管理。

1980 年代 CPU 性能有了显着提高,尽管这受到板载内存访问速度增长缓慢的阻碍。随着这种差异的加剧,工程师们发现了一种通过新的设计技术——缓存来缓解这个问题的方法。

本文将帮助您了解更多关于缓存是什么、它是如何工作的以及如何设计 CPU 缓存的信息。

什么是 CPU 硬件缓存?

CPU 硬件缓存是一个较小的内存,位于更靠近处理器的位置,用于存储最近引用的数据或指令,以便在需要时可以快速检索它们。通过减少访问速度较慢的主内存的代价高昂的读取和写入,缓存对 CPU 的性能产生了巨大的影响。几乎所有现代处理器都采用某种形式的缓存。

第一个缓存在芯片外或外部。这些很快被通常由 SRAM 制成的片上高速缓存存储器所取代。为了进一步提高性能,这些片上缓存被分成指令和数据分区。

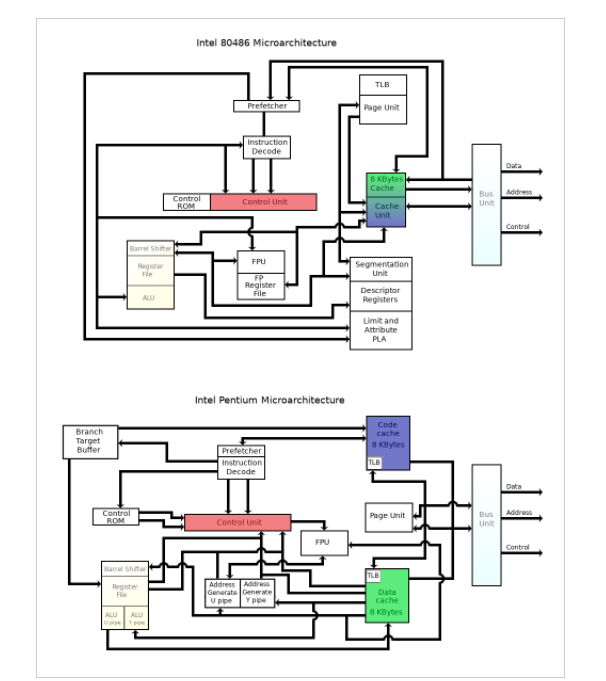

图 1 显示了一个分区示例。

图 1. Intel 80486 使用通用高速缓存,而其后继 Pentium P5 具有分区高速缓存(总线宽度已省略)

高速缓存分区导致了多级高速缓存层次结构的诞生,其中处理器内核将拥有自己的小型私有高速缓存 (L1),位于较大的共享高速缓存 (L2) 之上,一些处理器包括第三级高速缓存 (L3) 和偶尔是第四个(L4)。

局部性(又名缓存如何工作?)

为什么缓存有效?缓存通过引用的局部性原则工作。引用位置是指处理器在运行应用程序时访问相同内存位置的趋势。因为这些内存访问是可预测的,所以可以通过缓存来利用它们。

局部性通常分为两个子集——时间局部性和空间局部性——有时还有第三个子集,称为算法局部性。

时间局部性

时间局部性是指在短时间内重复使用特定数据项。这依赖于这样一个事实,即在处理器上运行的程序倾向于在短时间内使用相同的变量和数据结构。在从主内存中获取一个项目并将其存储在缓存中之后,对该数据的任何后续调用都可以更快地完成。

空间局部性

空间局部性是指将很快需要的数据项驻留在现在需要的项附近或相邻的内存位置中的趋势。这可能是程序员或编译器对内存中的项目进行聚类的结果。

例如,使用数组(一种数据结构)的应用程序会将数组的元素存储在相邻的内存位置。通过缓存当前正在使用的数据项旁边的数据项,处理器可以在必要时快速访问那些相邻的项。

算法局部性

一种较少讨论的局部性类型是算法局部性。算法局部性是应用程序对相关数据项执行操作的趋势,尽管不是在任何短时间内,并且尽管这些项目在内存中并不彼此靠近。

使用链表(另一种类型的数据结构)的应用程序可能会出现这种行为。这种类型的局部性可能出现在图形处理或迭代模拟中。

逻辑缓存组织

缓存存储和检索数据的方式和位置取决于缓存的组织方式。这称为缓存的逻辑组织。确定存储的内容由缓存中内置的管理启发式方法控制,但它也受到逻辑组织的严重影响。因此,缓存的布局方式对其性能起着重要作用。

有三种主要的方式来组织缓存:

完全关联

直接映射

设置关联

缓存块

当 CPU 需要访问主存中的某个项目时,它会使用一个地址来定位该项目。CPU 硬件缓存通常透明地工作,这意味着程序员无需以任何方式确认缓存。因此,用于访问内存的地址首先由缓存处理。该地址用于识别数据项是否位于缓存中。

术语“缓存命中”表示在缓存中找到了数据项,“缓存未命中”表示未在缓存中找到。

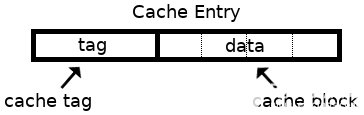

缓存被组织成称为缓存块的数据组。每个地址都被划分为多个位域,以便可以识别正确的高速缓存块。这些字段是缓存标记、集合编号和字节偏移量。图 2 显示了一个地址拆分为缓存可以解释的字段。

图 2. 寻址缓存块

当给 CPU 缓存一个地址时,它会将这个地址分成必要的字段并开始检查它的缓存条目。一个缓存条目由一个缓存标签(这里是标签标签)和一个缓存块(标签数据)组成。

缓存标签是一个标识符,它表示正在引用哪个缓存块。

缓存块是存储在该标签上的实际数据,代表主内存中的一个项目块。为了获取该块中的单个单词,使用了偏移量。

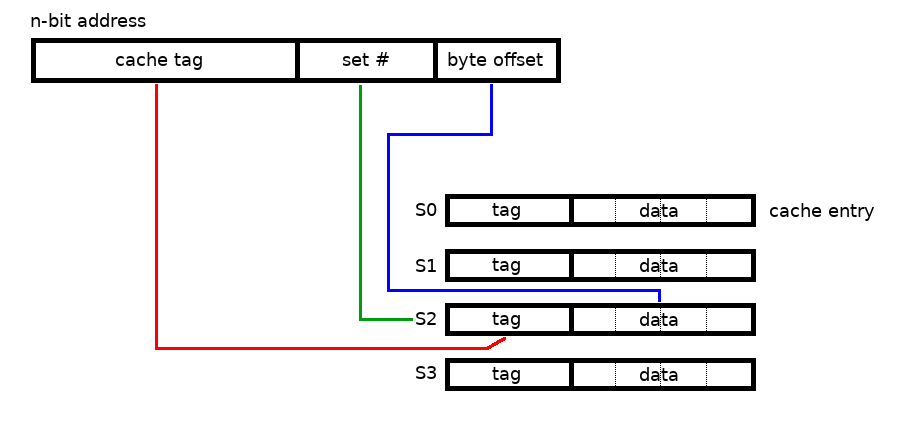

直接映射

在直接映射缓存中,缓存条目被组织成多个集合。地址中的集合编号用于索引每组条目。一旦识别出该集合,就比较缓存标签。如果它们匹配,则这是缓存命中并输出指定的数据。

理解直接映射缓存的关键是每个集合只有一个缓存条目。这使得直接映射缓存非常快,同时消耗最少的功率。

图 3。直接映射缓存

由于每组只能包含一个条目,因此直接映射缓存确实具有更高的争用率,这意味着多个数据项将希望存储在同一位置。这会导致缓存未命中。解决此问题的一种方法是使用完全关联的缓存。

完全关联

全关联缓存与直接映射缓存相反。与包含单个条目的多个集合不同,完全关联缓存具有多个缓存条目,它们都包含在一个集合中。因此,集合编号不再提供任何信息并且不被使用。相反,当缓存处理内存地址时,会检查每个缓存条目是否有匹配的标记。如果找到,则使用字节偏移量输出缓存块内的正确数据。

检查每个缓存条目使得完全关联缓存比直接映射缓存消耗更多的功率。通过使用一组关联高速缓存来在功耗和更高的争用率之间找到平衡点。

图 4. 全关联缓存

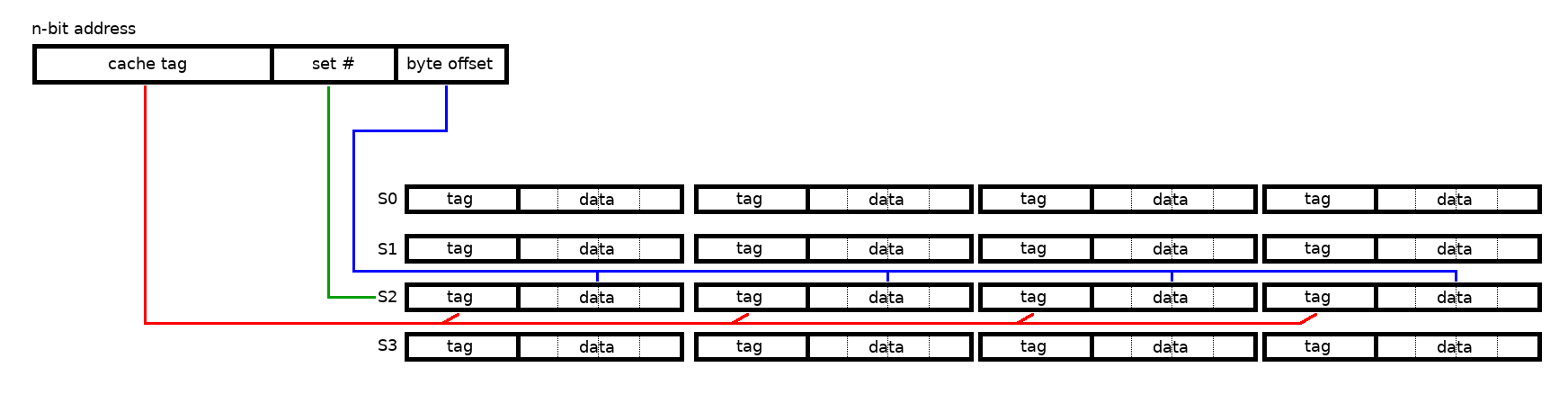

设置关联

一组关联缓存提供了两全其美的优势。它由多个集合组成,每个集合具有多个缓存条目。它是如何工作的?首先,集合编号允许缓存跳转到适当的条目集合。接下来,在每组条目中搜索匹配的标签。如果找到,则使用字节偏移量输出请求的数据。这种方法允许缓存提供功耗和争用率的优化平衡。

图 5 显示了一个 4 路组关联缓存。之所以称为 4-way,是因为每组最多可以包含四个缓存条目。如果每个集合只能保存两个缓存条目,那么它将是 2-way。因此,直接映射缓存实际上只是一个单路组关联缓存,而完全关联缓存是一个单组多路组关联缓存,其中 m 是缓存条目的数量。

图 5. 设置关联缓存

管理启发式

一旦确定了缓存的逻辑组织,就需要确定一组管理启发式方法。启发式管理只是一组确定缓存如何执行其职责的规则。这些通常在位于缓存上方的缓存控制器中实现,并充当它与 CPU 之间的接口。缓存管理启发式可以分为两个不同的类别:内容管理和一致性管理。

内容管理

内容管理启发式正是它们听起来的样子。它们是一组规则,用于确定缓存的时间和内容。这些启发式方法识别已从内存请求的重要项目,并将这些项目复制到缓存中。内容启发式的两个示例是预取被认为重要或即将使用的数据项,以及决定在缓存集已满或接近容量时替换哪些项目的替换策略。

一致性管理

一致性管理启发式方法都是关于保持缓存与其他内存同步。这可能意味着主内存、层次结构中的其他缓存级别,甚至缓存本身。例如,缓存不应该在其缓存块中包含相同数据的多个副本。此外,如果高速缓存和主存储器具有应该是相同数据的不同副本,则应用程序可能会收到过时或陈旧的数据项。这在多核系统中尤其可能。因此,一致性管理启发式可能会定期使用更新版本的缓存数据更新主内存。

CPU 硬件缓存基础知识回顾

本文介绍了 CPU 硬件缓存的一些基本原理。CPU 缓存的工作原理是参考局部性,即处理器倾向于在短时间内或在相邻的内存位置对内存进行可预测的读取和写入。讨论的其他设计原则是如何在逻辑上组织缓存以及需要定义以管理该缓存的规则。几乎所有 CPU 中都可以找到缓存,并且缓存设计技术已扩展到软件缓存和基于 Web 的缓存,用于存储浏览器数据或 Web 文档。我希望这篇文章能帮助您更好地理解和欣赏这项重要的技术。

-

什么是CPU缓存?它有哪些作用?2024-08-22 9420

-

cpu缓存的作用及原理是什么2023-08-21 4983

-

关于CPU缓存的作用2022-03-30 5495

-

高速缓存(cache)的工作原理是什么?高速缓存可分为哪几类2021-12-23 2633

-

CPU缓存的作用及原理有哪些2021-08-27 12765

-

缓存如何工作,如何设计CPU缓存2020-11-19 3532

-

光纤的概念、工作原理、设计原则和分类2020-11-04 9734

-

各级别CPU缓存的工作原理2020-10-30 5283

-

CPU缓存是什么意思_CPU缓存有什么作用2020-05-19 8659

-

CPU缓存对性能的影响2010-11-13 3134

-

什么是CPU工作电压/高级转移缓存?2010-02-04 1414

-

CPU一级缓存2009-12-24 600

-

cpu的工作原理2008-01-15 17936

全部0条评论

快来发表一下你的评论吧 !