用于为ADAS应用开发的电源系统的功能安全开发工具和方法

描述

汽车原始设备制造商 (OEM) 一直处于移动出行(Mobility)和高级驾驶辅助系统 (ADAS) 的前沿,在这个快速发展的领域争夺领导地位。随着这些系统的进步,车辆中半导体元件的数量也随之增加,以应对不断增加的新功能。

面对车用半导体市场如此快速的增长, 瑞萨电子开发了许多车用产品,这其中包括微控制器(MCU),高度集成的片上系统 (SoC) 处理器,存储器以及电源管理系统(PMIC)。

然而,随着行业的发展,问题仍然存在:“我们如何才能在整个行业中标准化这些元件的开发和设计,以便我们能够应对风险并自信地声称该部件在功能上是安全的?”

因此,在 ISO 26262 的第一版中,汽车行业尝试了开发的标准化,以便将如下所列出的大型系统元件开发时的风险降至最低:

因某些相关关系的遗漏,或不完整的分析所导致的系统性风险

设备故障所导致的随机硬件失效。

在过去大约十年的时间里,汽车 OEM 一直依靠该标准的第 5 部分(part 5)

来帮助他们解决硬件故障,以实现业界公认的“安全”设计。瑞萨电子在产品开发中也采用了类似的标准,通过使用失效模式影响诊断分析 (FMEDA) 以及相关失效分析 (DFA) 对我们的产品进行分析,并提出解决设计中随机硬件失效的策略。

在该标准第 5 部分的基础上,为了应对汽车系统的复杂性,ISO 26262 扩大了其覆盖范围,包括进了专门针对半导体元件的第 11 部分(part 11)。

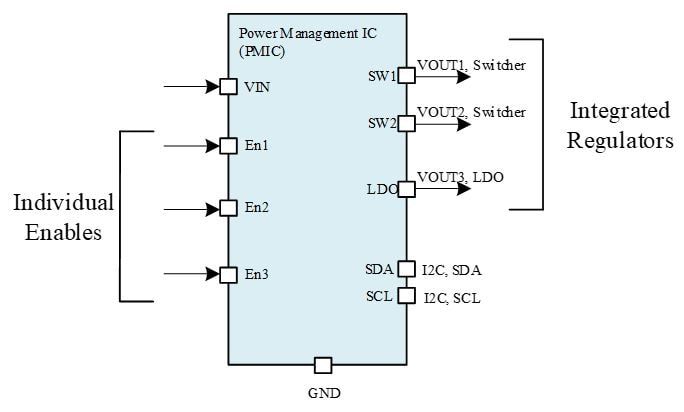

为了满足提高功能安全的同时降低成本的这一新需求,除了我们的 R-Car 片上系统处理器之外,瑞萨还为汽车系统设计人员提供多轨、高功率的电源管理系统 (PMIC)。这不仅能够减少元件数量,还能够提供系统开发所需的高性能。

图像

图 1:具有 3 个输出的基本 PMIC

为帮助汽车设计师了解在购买 PMIC 时需要注意哪些事项,我们将对功能安全设计时所需要的分析进行说明。为了解决在元件层面和系统层面上的相关失效及随机硬件失效问题,瑞萨电子的所有电源产品均采用了类似的架构。这样下次当您发现我们的 R-Car 套件搭载了瑞萨的 PMIC 时,您就会对自己的选择充满信心。

1. ISO 26262 分析方法(ISO 26262 Analysis Tools)

在通读 ISO 26262 后,我们总结了该规格推荐的3种用于开发符合功能安全的产品的分析方法,具体如下:

框图;

失效模式,影响及其诊断分析(FMEDA: Failure Modes Effects and Diagnostics Analysis);

相关失效分析 (DFA: Dependent Failure Analysis)。

这些方法之所以会被推荐,是因为它们能够降低复杂性的同时完成功能安全的设计。瑞萨电子为了解决随机硬件失效的问题,在设计每一款PMIC产品时都采用了这些分析方法。

1.1 框图(The Block Diagram)

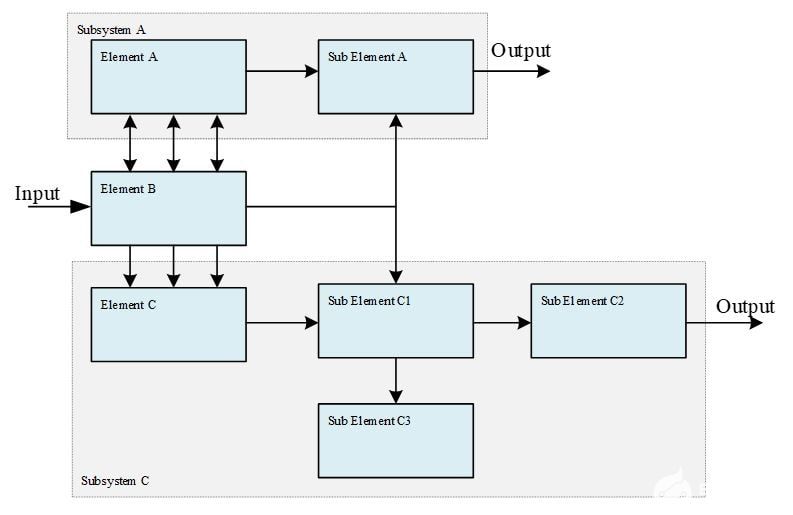

通读 ISO 26262 的规格,可以明显感觉到规格制定者重视的一件事:避免不必要的复杂性。并且,该规格给出了一套制作框图的标准:

对设计进行抽象化,以确保每个区块都有专门的功能,消除不必要的(往往会引起混乱的)混合功能。

使用概念安全分析(conceptual safety analysis )对运作流程简化,并对具体功能的执行位置进行最优化。。

图 2 显示了此类框图的一个简单示例。

图像

图 2:系统框图示例

1.2 失效分析方法 (Failure Analysis Tools)

在开始分析之前,我们需要确认规格希望我们在分析中使用的方法。这些方法可帮助我们确认安全机制和其保护对象的相关性(Dependent Failure)以及鲁棒性设计(Robust Design)所允许的故障模式。

DFA:此分析方法有助于我们对相关失效进行识别。例如,当我们想要找出安全机制和其保护对象的元件之间相关失效时,可以使用此方法。

下面给出几种利用该分析方法进行识别的常见案例:

VCC:为安全机制供电的电路发生漂移、噪声或故障时,可能会对供电设备产生不利影响。

温度:温度的升高或降低可能会影响监测精度的同时,降低其控制某些对象的能力。

DFA 通过识别并减轻相关关系(Dependencies)的方法,使这些影响得到减轻。

FMEDA:该分析方法在考虑了例如电阻串损坏和漂移等普遍被接受的故障模式的前提下,对功能所受的影响进行分析。同时还可用作失效性模拟器,对 ASIL 评级的安全范围是否合理的进行确认。

DFA 需要识别各个功能之间的相关性,而 FMEDA则是一种更为直接的方法。FMEDA 的目标是调查功能的层次结构并将预想的故障模式应用于每个元素。此处涵盖的故障最初在 ISO 26262 的第 5 部分中引入,然后在第二版的第 11 部分中进行了扩展。其中包括:

电阻器故障和元漂移

内存中的软错误率,以及数字逻辑电路中的固定型故障

数据传输失败

在概念设计阶段,将这些故障应用于设计,创建机制来解决故障模式,然后分配覆盖范围。

2. 瑞萨 PMIC 架构介绍(Introducing Renesas PMIC Architecture)

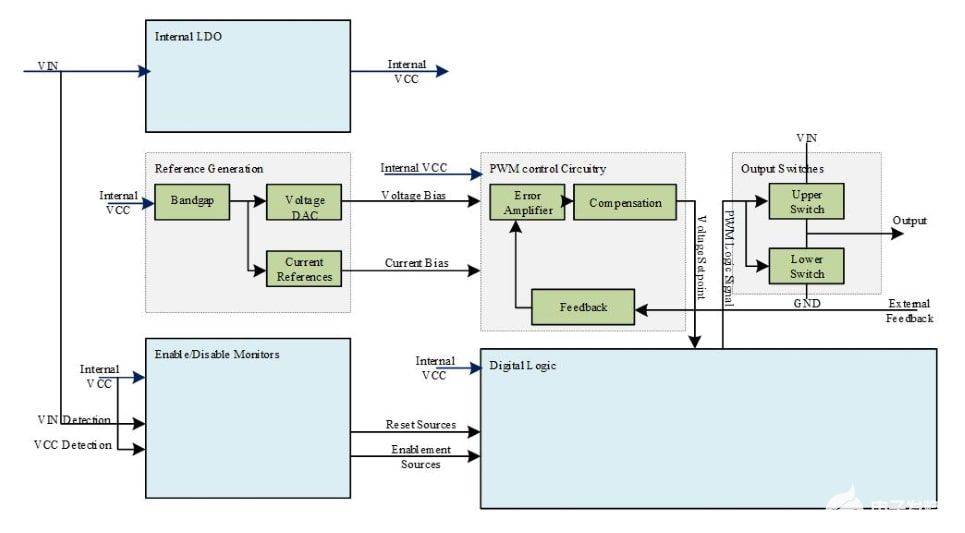

瑞萨电子基于这些分析的结果,定义了产品的主要元素。

基准电压的生成:这通常包括分配带隙和偏置电压的电路。

内部电源的生成:为设备的内部元件提供电源的内部电源域。

开关:这包括提供输入电压切换的预驱动器和驱动器电路。

PWM 控制电路:这包括整个控制回路。

调节器使能:启用或禁用调节器。

数字核心:控制上述要素的构成使其可用于不同的应用。

通常,这些系统就是PMIC(电源管理系统)的基本构成要素,如图 3 所示。

图像

图 3:基本监管架构

结合 DFA 和 FMEDA,我们可以从概念上分析我们的架构,并考虑追加必要的功能和安全机制,以提高对硬件失效方面的鲁棒性。虽然此分析并非详尽,但它将为我们的数据资料提供一些背景信息。

2.1.1 内部轨和偏置生成(Internal Rail and Bias Generation)

瑞萨电子在设计产品时,首先会明确各个要素间的偏置关系。例如,为设备周围的电路提供抽头电压的DAC。

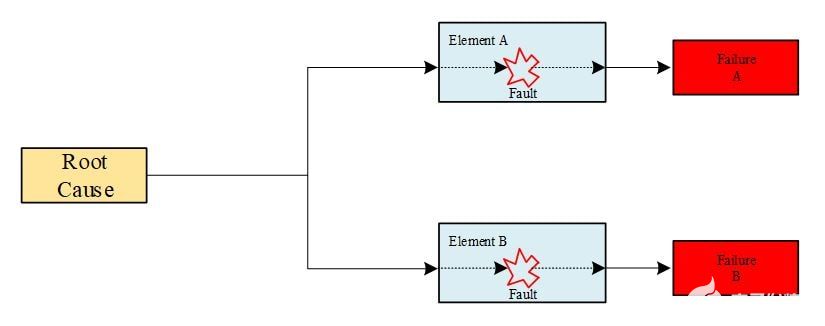

我们根据DFA 定义了故障模型并总结为以下内容。

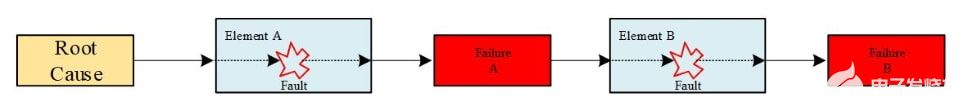

共因失效 (CCF: Common Cause Failure):单个故障导致两个独立元件各自发生故障。

图像

图 4:共因失效模型

级联失效(Cascading Failure):一个元件出现的故障导致另一个元件出现故障。

图像

图 5:级联失效模型

将这两种失效模型与图 3 结合来看,偏置和 VCC使用了同一个生成源,如果出现故障,将会影响电压调节和监测机制。

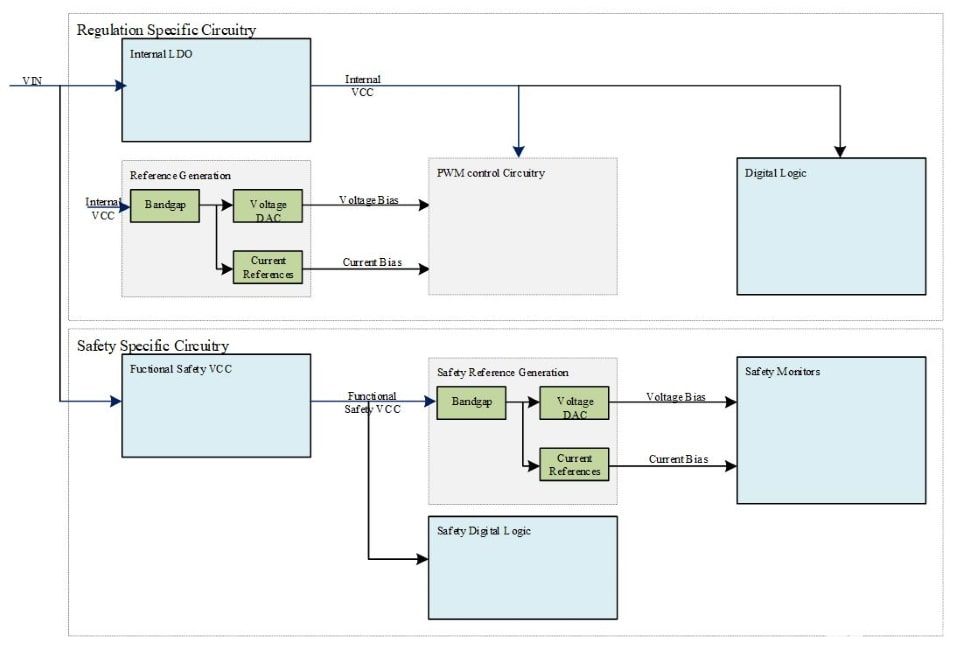

为了解决这个问题,原始架构被更改的更加独立。

图像

图 6:改进的偏置结构,具有单独的电力供给

图 6 给出了处理这种相关关系时的一种方法,其中有单独的偏置电路(带隙)和电压 DAC 来创建各自独立的偏置点。这减少了电路之间的相关性,这也是为什么您会在我们的许多数据表中找到独立的带隙、带隙监测器和 VCC 监测器的原因。安全要求越严格,解决方案就越复杂。

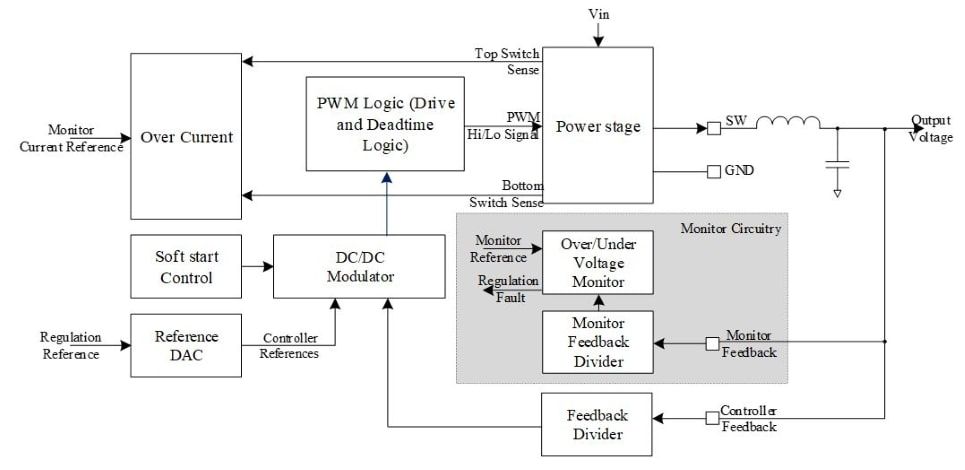

2.1.2 PWM 控制电路和输出开关及驱动器(PWM Control Circuit & Output Switches and Drivers)

在设计反馈回路时,不同的架构决定了不同的性能以及必要的安全机构,因此反馈回路的设计对PMIC尤为重要。具体的失效模式分析示例如下:

由于被固定在高电平或低电平而导致输出切换的故障:这将导致由于直通短路或将输出直接连接到地或 VIN 而导致切换出现无规则性的问题。

为防止负载变化期间相对于设定值出现的过度变化的控制回路补偿:这里的潜在故障是,控制器的带宽急剧变化可能导致过压或振荡现象的发生。

由于许多故障会导致输出电压偏离其设定值或输出电流超过设备或其负载的安全额定值,因此PMIC需要具有监控输出电流和输出电压的安全机制。这些安全机制通常由比较器或板载模数 (A/D) 转换器来实现。

接下来,我们将用 DFA 来分析反馈节点。在反馈路径中,通常有一个电阻分压器网络将输出电压转换为内部参考电平。若该电阻器出现故障,目标设定值会变得不正确,并且影响监测机制的监测能力。

因此我们得出了以下标准:

设备需要设置两个独立的反馈源,以解决反馈节点与板上另一个引脚或另一个电压短路的相关故障。

这种独立的反馈源需要一个冗余电阻分压器来解决电阻反馈网络任何部分的短路故障模式。

出于这个原因,您经常会在我们的产品中看到除了反馈引脚之外还有另一个用于监控的引脚。如果是内置反馈电阻,则大多情况下会为了冗余性而设立其他不同的路径。

图像

图 7:基本 DC/DC 调制器

对于最后的两节中,我们的焦点将由控制回路转向监测机制。

2.1.3 监视器和控制(Monitors and Controls)

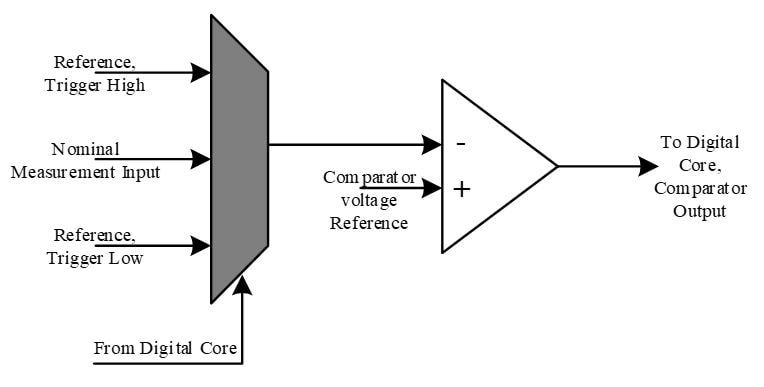

监视器和使能控制可以说是设备中最重要的电路之一,因为它们对于确保系统功能安全的安全机制的实施至关重要。它们由以下一系列比较器电路组成:

过流监测。

上电复位监测。

输出电压(过压和欠压)监测。

内部时钟监测。

在进行 FMEDA分析 时,我们假设比较器输出出现了固定型故障(固定在高位和低位)。在这两个故障中,固定在低位的影响更大,因为在正常操作中会漏掉发生的故障,成为潜在故障。为了提高设备检测出这些低位固定型故障的能力,瑞萨 PMIC 设置了自检功能 (ABIST)。

该过程由图8所示:

图像

图 8:比较器 BIST 架构示例

数字控制器将输入切换至比较器以生成强制触发,正常运作得到确定后,输入控制再次变为正常模式。

2.1.4 数字内核(Digital Core)

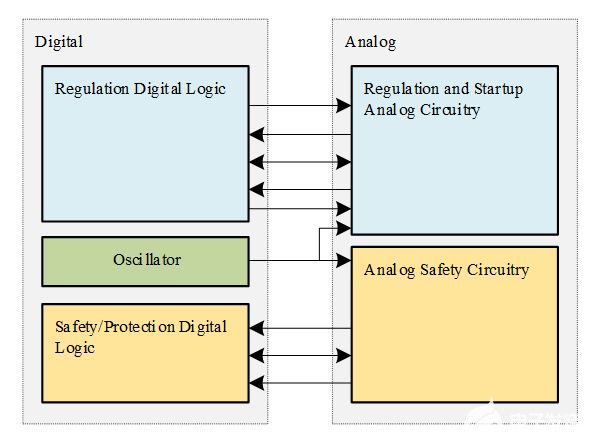

如图 9 所示,数字内核位于模拟部分附近,并且通常分为负责功能安全相关控制的部分和负责稳压器启动和控制的部分。

这种架构通常更适合用于减少 DFA 分析所发现的相关关系。为了更好地理解数字内核的结构,请参见图 9,其中主要功能包括:

通常由寄存器和一次性可编程 (OTP) 熔丝构成;

功能安全相关控制,通常由状态机实现。

通信,通常搭载I2C 或 SPI 控制器。

图像

图 9:模拟和数字分区

在这里,针对一次性可编程 (OTP) 熔丝阵列和配置寄存器进行数据损坏(Bit Corruption)相关的FMEDA分析后,能够预想到在启动或者运行时将会出现芯片配置错误的故障。为了防止出现此问题,在启动时和设备配置中定期执行循环冗余计算 (CRC)。并且将此方法扩展到通信接口。

实现数字部分的安全机制的方法还有很多,除了 CRC 之外,还有以下列出的安全机制:

必要的冗余逻辑;

时钟监测;

逻辑 BIST (LBIST),与 ABIST 一样,检查数字逻辑是否存在固定型故障。

3. 结论

每个新产品的开发,都会由设计团队和安全团队对功能安全机制进行探讨研究,然后由营销团队将这些新产品的特点进行推广和普及。本文中介绍的概念性分析旨在为读者提供一些捷径,以便于了解瑞萨电子是如何设计 ASIL 级电源管理产品,以及为何我们会在硬件数据表中列出各种“安全”相关功能的原因。

审核编辑:郭婷

-

Microchip开发工具2011-03-08 0

-

ADAS功能开发的经验和技术难点2017-02-21 0

-

STM32 VR开发工具2017-02-17 965

-

ADI新能源汽车BMS电源管理系统开发工具2017-03-24 1035

-

ARM开发工具解读2017-10-18 1093

-

web前端开发工具排行:8款html开发工具推荐下载2018-02-01 85241

-

电子功能安全开发及汽车EPS电机控制设计2018-08-14 4940

-

Microchip推出首款汽车安全开发工具包,提供全方位的汽车安全保障2018-08-11 4781

-

Zynq-7000 All Programmable SoC的开发工具概述2018-11-26 3338

-

微软宣布新的开发工具_用于增强应用程序的通话和短信功能2020-09-28 2087

-

DSP的开发工具及开发环境的详细资料说明2020-10-15 1503

-

6个高效的前端开发工具2021-01-05 4590

-

Windows 10/11应用开发工具的安装方法2021-08-04 683

-

什么是SEooC?SEooC和正常功能安全开发有什么不同?2023-04-27 9473

-

常用的上位机开发工具2023-05-09 1309

全部0条评论

快来发表一下你的评论吧 !