适用于ADAS和自动驾驶系统的高可靠性和高性能深度学习加速器

描述

下一代 ADAS 和自动驾驶 (AD) 系统部署到市场后,将需要准确、高速的识别、判断和操作。卷积神经网络 (CNN) 需要大量计算来进行模式识别。随着安装的传感器数量的增加,需要更高的 CNN 性能。然而,随着功耗与性能成正比增加,需要一个笨重且昂贵的水冷系统。需要同时实现高深度学习性能和低功耗,以实现轻量级且具有成本效益的空气冷却系统。从实际的角度来看,实现 60TOPS 的 CNN 性能和 10TOPS/W 的效率是每个 LSI 设备的最佳目标。

具有高性能和高能效的 CNN 加速器

CNN 加速器 (CNNA) 的性能/效率目标是实现 60TOPS 性能和 10TOPS/W 效率。从实现的角度来看,它是用三个相同的加速器而不是一个加速器来实现的。一个CNNA包含13,824个MAC算术单元,工作频率为800MHz。三个CNNA的理论最大性能为66TOPS。此外,每个 CNNA 通过一个 512 位互连模块连接 2MB 专用暂存器 (SPM)。这提高了CNNA的执行效率,将CNNA与外部存储器(DRAM)之间传输的数据量减少了约90%,并节省了DRAM接口和互连所消耗的功率。从测试芯片的实测来看,VGG16的性能为32TOPS,效率为6.1TOPS/W,CNNA优化网络(Network-A)的性能为60.6TOPS,效率为13。

ASIL D 任务的安全机制

下一代 ADAS 和 AD 系统需要实现 ASIL D 的功能安全,这是 ISO 26262 中最严格的安全级别。双核锁步 (DCLS) 是可以满足 ASIL D 指标的方法之一。可以通过在两个冗余硬件上执行相同的过程并比较它们各自的输出来检测。

CNNA 还需要硬件冗余来满足 ASIL D 指标,但简单地应用 DCLS 需要大型 MAC 计算单元来实现冗余。这是不实用的,因为面积和功耗显着增加。为了在不添加冗余硬件的情况下实现 ASIL D 指标,两个 CNNA(CNNA1 和 CNNA2)由软件动态配置,以在需要安全的处理过程中执行锁步操作。

CNNA 用于从相机输入的图像识别处理 (ASIL B) 和从每个传感器输入的结果 (ASIL D) 对周围环境进行建模。但大部分执行时间是以前的 ASIL B 图像识别处理。因此,通过仅在周围环境建模处理期间将 CNNA1 和 CNNA2 切换为锁步操作,可以在不显着影响性能或功率效率的情况下实现 ASIL D 任务。

下面是CNNA使用锁步DMAC(LDMAC)的锁步操作。

1) LDMAC 将相同的数据从 DRAM 加载到 SPM1 和 SPM2。

2)CNNA1和CNNA2执行相同的网络处理。

3) LDMAC 从 SPM1 和 SPM2 读取执行结果并进行比较。如果它们不匹配,则判断为错误。只有CNNA1的结果存储在DRAM中。

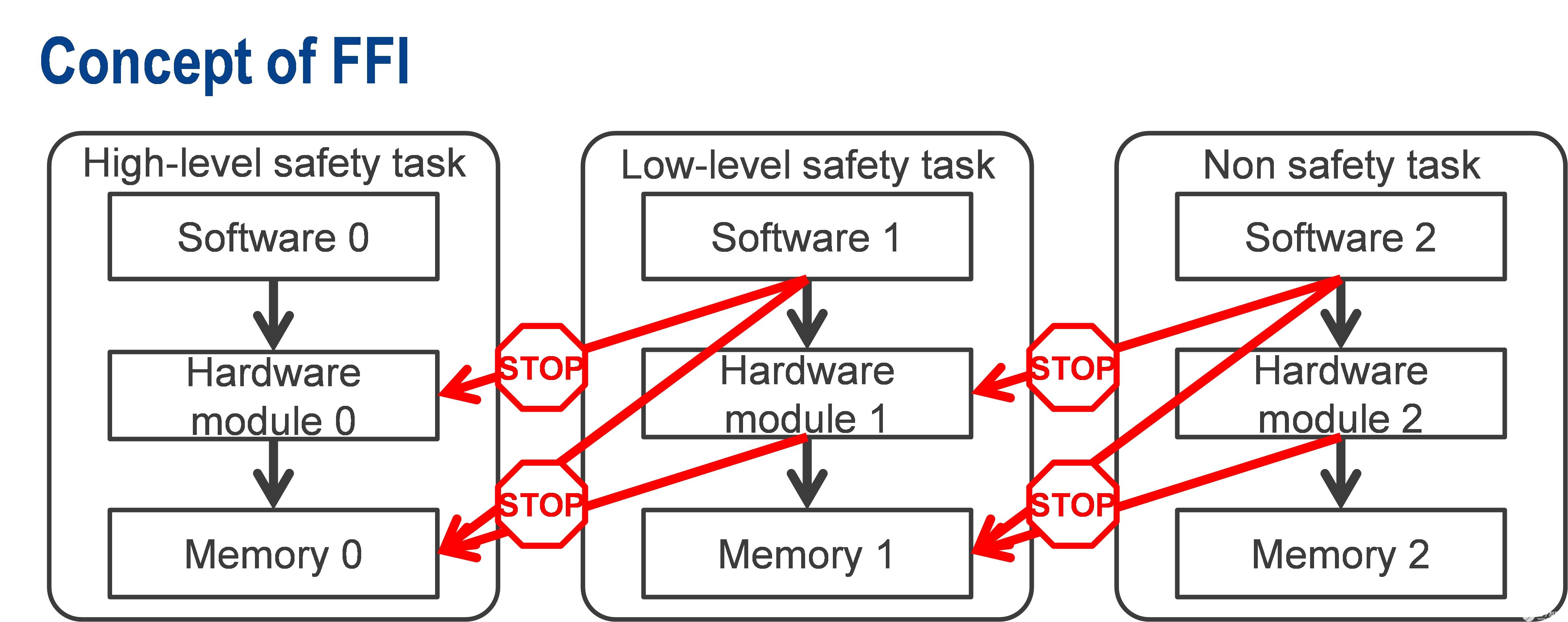

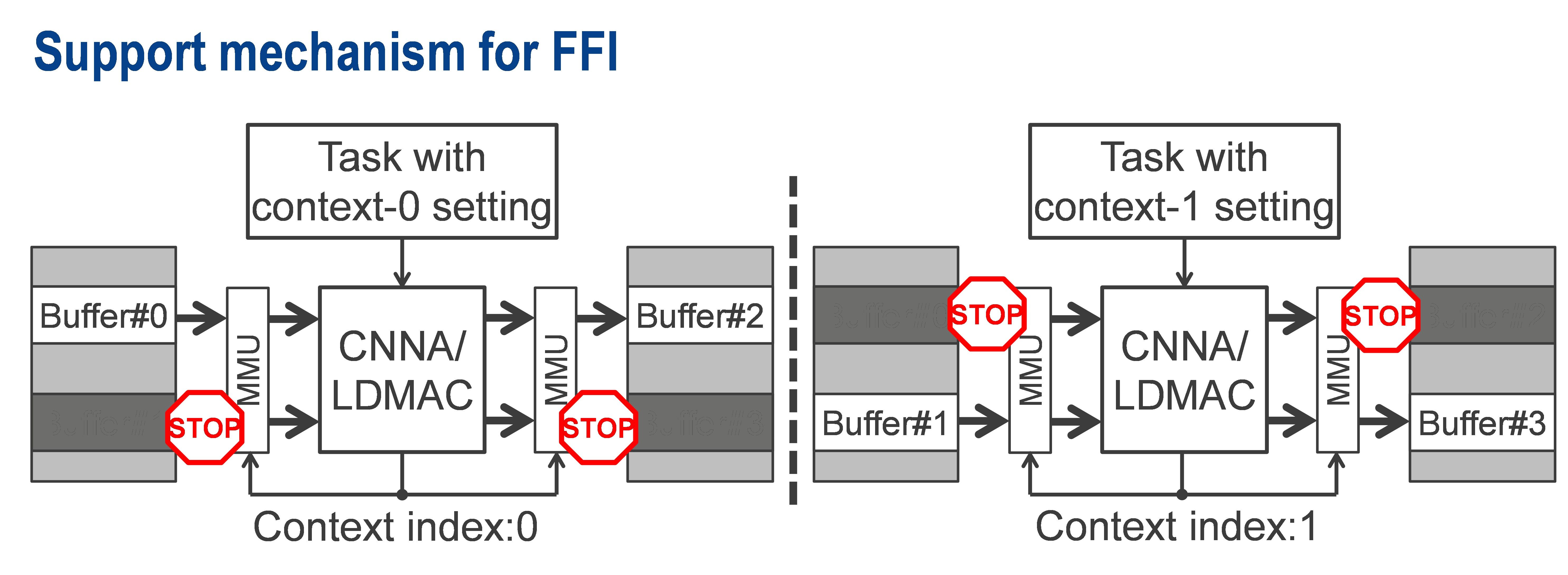

实现 ASIL D 的另一个重要因素是免于干扰 (FFI)。系统中混合了具有不同 ASIL 的任务。他们不得干扰更高级别的 ASIL 任务。前面说过,CNNA是被不同ASIL级别的任务访问的,所以每个任务使用的内存空间必须是独立的。

内存空间隔离机制在CNNA、LDMAC和内存管理单元(MMU)的内存保护表中实现。当前运行任务的上下文索引被赋予来自CNNA和LDMAC的事务输出。MMU 接收它并在逐个事务的基础上切换上下文。

审核编辑:郭婷

-

FPGA在自动驾驶领域有哪些应用?2024-07-29 8324

-

通过深度学习提高和发展车辆感知2022-11-10 940

-

用于ADAS系统和自动驾驶车辆中雷达的毫米波传感器2022-11-09 1131

-

存储如何提升自动驾驶汽车的可靠性看了就知道2021-03-10 3061

-

英国推出可应用于ADAS和自动驾驶的神经网络加速器2020-11-16 2832

-

【PCB】什么是高可靠性?2020-07-03 11991

-

ADAS视觉传感技术,为朝向自动驾驶趋势发展做好准备2020-06-02 2695

-

高性能高可靠性隔离式电源解决方案2019-05-29 1399

-

ADI与Momenta强强联手,加速自动驾驶高精度地图产业化2019-01-04 1845

-

用于ADAS和自动驾驶的FPGA的案例2019-01-03 4821

-

可扩展图像传感器平台用于先进驾驶辅助系统和自动驾驶2018-10-11 3083

-

神经网络解决方案让自动驾驶成为现实2017-12-21 8861

-

细说关于自动驾驶那些事儿2017-05-15 7157

全部0条评论

快来发表一下你的评论吧 !