用于宽带通信ASIC的ADC

描述

无线系统基础设施的增长和部署的无线设备数量逐年增长。我们对按需数据和信息的无限渴望——无论何时何地——继续挑战系统要求。5G 的发展正在迅速发生,为实现这一切而计划的卫星数量也在增加。

为了向最终用户提供更快的访问、有保证的连接性和更长寿命的电池,这些射频通信系统的开发变得越来越复杂。

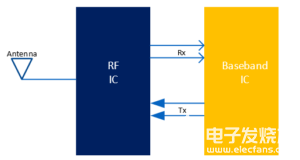

尽管对这些通信系统提出了新的要求,但在最高层次上,这些系统并没有随着时间的推移而发生太大变化。有一根天线将无线电波与收发器射频芯片连接起来。在接收路径中,信号经过滤波和放大,以将所需的射频信号与天线拾取的其他信号分离,然后将信号下变频到基带频率。上变频后,发射路径中的信号也经过滤波和放大以驱动天线。通常,基带芯片中的数据转换器充当射频芯片上的模拟信号和数字数据处理之间的接口。

图 1:射频通信收发器

在之前的博客中,我们研究了各种 ADC 架构,但宽带通信 ADC 设计还有其他考虑因素。它们是什么,它们如何转化为定制的 ASIC?

在考虑宽带通信时,我们正在研究具有每秒千兆样本 (GSps) 采样率的 ADC。之前讨论的架构,如逐次逼近寄存器 (SAR) ADC 和 SAR 辅助流水线 ADC,通常无法达到这些速率。然而,通过将 SAR 辅助流水线 ADC 内核与时间交错架构相结合,可以将采样率扩展到 GSps,同时实现稳健、低功耗和高效的解决方案。

时间交错 ADC,以 Fs 采样(频率采样)通过 M 个子 ADC 内核实现,每个子 ADC 内核以 Fs/M 顺序采样。每个子 ADC 以低 M 倍的频率运行,这随后放宽了设计要求并使其更容易实现高频。但是,每个子ADC必须匹配好,采样时间没有延迟,这是很难做到的。有许多错误来源都可能导致整体动态性能下降。因此,校准用于消除这些错误并提高性能。

使用时间交错 ADC 转换宽带信号时,只有通过优化和稳健的校准才能实现准确高效的转换。性能、成本和功耗都取决于此校准的质量。

Dialog 设计人员在宽带通信领域开发了许多定制 ASIC。第一个是用于固定无线接入 (FWA) 应用的 ASIC。FWA 通过无线电链路在固定位置之间提供宽带通信,而不是传统的光纤或铜线安装。ASIC 提供基带接口 IC 功能,连接射频收发器 IC 和基带处理器 IC。它包括正交电流转向数模转换器 (DAC) 和正交 SAR 辅助流水线 ADC。这种 ADC 架构非常适合最大限度地降低系统复杂性和成本。

第二个 ASIC 用于 G.Fast 通信。G.Fast 是一种超高速宽带技术,可以在使用现有铜线基础设施的同时实现超过 100Mb/s 的下载速度。我们为此应用开发的 ASIC 解决方案是一个由多个组件组成的模拟前端 (AFE)。其功能的核心是时间交错 ADC 和电流控制 DAC。数据转换器以 424MSps 的速度对信号进行采样,性能为 52dB MTPR(多音功率比)。

无论用于提供无线或有线宽带的介质如何,目标都是增加覆盖范围和容量,实现这些目标需要更高采样率的数据转换器。时间交错 ADC 和 SAR 辅助流水线 ADC 提供满足这些要求所需的数据速率。随着未来对 5G 的需求需要超过 1Gb/s 的数据速率,Dialog 将继续走在最前沿,开发支持您的设计或由我们集成到定制 ASIC 所需的数据转换器。

审核编辑:郭婷

-

信号基站、宽带通信的 “最佳拍档”#芯片 #国产芯片 #半导体芯佰微电子 2025-02-10

-

JESD204B有专用于ADC/DAC和FPGA或ASIC的接口吗?2025-02-08 576

-

基于连续时间、∆-Σ高速ADC的宽带模拟前端技术分析2023-01-09 2095

-

用于Asic BM1387的PCB2022-07-07 1899

-

AN-1408:使用AD8376VGA驱动适用于高中频交流耦合应用的宽带ADC2021-05-16 705

-

Dialog针对宽带通信ASIC的ADC2020-12-26 862

-

超宽带通信有什么特点?2019-10-24 2508

-

如何利用3G移动通信中脉冲成形FIR滤波器实现ASIC?2019-08-02 1190

-

采用AD8376和AD9445的宽带ADC接口示例2019-06-14 2238

-

探究宽带GSPS ADC中的DDC(第1部分)2018-10-26 3400

-

探究宽带GSPS模数转换器(ADC)2018-08-06 2252

-

用于宽带无线通信系统的SAR ADC研究与实现2018-02-02 727

-

超宽带无线通信,超宽带无线通信是什么意思2010-03-13 1623

-

用于多种移动通信系统的超宽带共面天线2009-10-24 499

全部0条评论

快来发表一下你的评论吧 !