比较和对比PCIe和以太网时钟抖动规范

描述

PCI SIG 于 2017 年 9 月批准了 PCIe Gen4 规范的 1.0 版。PCIe Gen5 规范于 2018 年 4 月底移至 0.7 版,并计划在 2018 年 9 月发布 0.9 版。Gen5 规范的发展速度要快得多比他们为 Gen4 所做的。如今,大多数新设计活动都集中在 PCIe Gen3 或 Gen4 上,现在深入研究 PCIe Gen5 设计还为时过早,因此我们暂时将重点放在 PCIe Gen3 和 Gen4 上。

在我们深入研究之前,我想指出 PCIe Gen4 的一个有益特性是时钟抖动的计算与 Gen3 相同。唯一的区别是 PCIe Gen4 抖动限制为 500fs rms,而不是 Gen3 的 1ps rms。这意味着,如果您使用 PCIe Gen3 计算来计算时钟抖动并且您的结果小于 500fs rms,那么您可以将时钟用于 PCIe Gen4。

PCI Express 时钟的相位噪声测量技术与用于网络时钟的技术有很大不同。本博文的其余部分对两者进行了比较和对比。

让我们从常用的 12kHz – 20MHz 砖墙滤波器开始,该滤波器通常与相位噪声分析仪 (PNA) 一起用于测量网络时钟,参见图 1。线性垂直刻度以 dBc/Hz 为单位(每个频率下相对于载波的分贝)和对数水平刻度以赫兹为单位。对于 PCIe 时序,载波是 100MHz 时钟。以太网时钟通常使用 156.25MHz。

简单检查表明,在 12kHz 和 20MHz 之间的“通带”没有衰减,如 0dBc 处的水平线所示。12kHz 和 20MHz 处的垂直线完全衰减了通带外的频率。我们将这些垂直线称为“砖墙”过滤器。这意味着抖动计算包括通带区域内的所有噪声并排除通带外的所有噪声。该滤波器对通带中的所有噪声内容同样敏感。

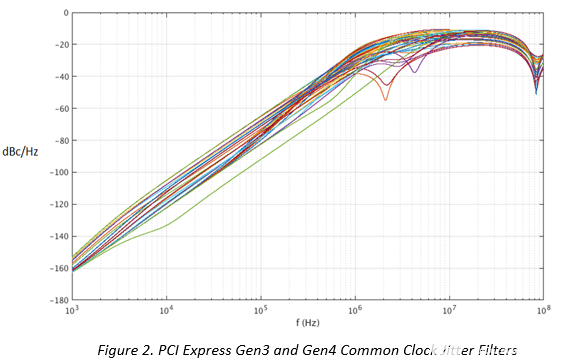

图 2 说明了在计算抖动之前应用于 PCIe 时钟抖动的滤波器组合。PCIe Gen3 和 Gen4 时钟抖动是应用 64 个滤波器组合后获得的最差值。这个最差值必须小于规范限制。

检查图 2 可以看出与图 1 的 12kHz – 20MHz 滤波器的显着差异。最明显的差异是没有砖墙。相反,在 1MHz 以下有 20dB/decade 的衰减。(注意:十年是对数刻度上的 10 的幂 [104 到 105、105 到 106])。这种衰减适用于常见的时钟系统,因为我们假设低频噪声很常见,并且我们指定所有 PLL(时钟 PLL 和 TX/RX PLL)来跟踪它。这意味着 PCIe Gen3 和 Gen4 通用时钟系统对低频时钟抖动的敏感度低于网络系统。这也是为什么用于普通时钟系统的非常好的 PCIe 时钟通常具有相对较高的 12kHz – 20MHz 相位抖动数。这也是为什么为通用时钟系统指定的时钟不一定在单独的时钟系统中使用的原因。

下一个要注意的事项是滤波器通过了 1MHz 以上的大部分噪声,实际上滤波器在 1MHz 以上相当平坦。这意味着 PCIe Gen3 和 Gen4 通用时钟时序对 1MHz 以上的抖动最为敏感。

PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历史上看,PNA 一直无法使用正在扩频的时钟。

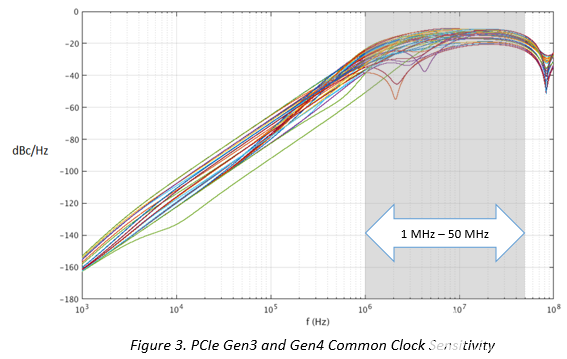

根据 Nyquist,对信号进行采样的行为将所有信息混叠到 f/2。对于 100MHz PCIe 时钟,这意味着从 DSO 获得的文件包含高达 50MHz 的有用信息。这也意味着基于 DSO 数据的 PCIe 时钟抖动计算一直计算到 50MHz!尽管滤波器在 1MHz 以上大约 -20dBc,但 PCIe Gen3 和 Gen4 通用时钟抖动在 1MHz 到 50MHz 的范围内最为敏感,如图 3 所示。

审核编辑:郭婷

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

PCIe真的在同以太网竞争并能胜出吗?2021-05-24 2321

-

1.8V千兆以太网收发器低抖动时钟电路2010-06-11 820

-

工业以太网的时钟同步协议对比研究2011-08-09 957

-

万兆以太网规范2012-03-27 5967

-

同步以太网规范兼容的联合测试展示加速高速以太网设计上市时间2018-05-23 1554

-

汽车以太网与工业以太网物理层对比2019-03-22 16171

-

以太网技术联盟发布了800千兆位以太网的规范2020-05-18 4345

-

信而泰汽车以太网测试方案助力国内汽车以太网建设2020-06-11 4283

-

如何快速分辨以太网与千兆以太网2022-05-06 6378

-

以太网、工业以太网和Profinet三者有何关联?2023-05-23 3437

-

以太网交换机的升级版:PCIe交换机2023-07-17 4250

-

万兆以太网规范解读2024-01-15 6074

-

AD9574以太网 千兆以太网时钟发生器技术手册2025-04-10 1256

-

解析AD9571:以太网时钟发生器的卓越之选2026-03-23 123

全部0条评论

快来发表一下你的评论吧 !