5nm及更先进节点上FinFET的未来

电子说

描述

虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得更具挑战。

泛林集团在与比利时微电子研究中心 (imec) 的合作中,使用了SEMulator3D®虚拟制造技术来探索端到端的解决方案,运用电路模拟更好地了解工艺变化的影响。我们首次开发了一种将SEMulator3D与BSIM紧凑型模型相耦合的方法,以评估工艺变化对电路性能的影响。

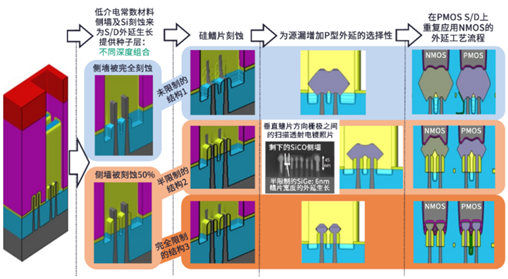

这项研究的目的是优化先进节点FinFET设计的源漏尺寸和侧墙厚度,以提高速度和降低功耗。为此,我们比较了具有三种不同外延 (epi) 生长形状和源漏Si刻蚀深度的FinFET反向器结构(图1),研究低介电常数材料侧墙厚度变化的影响,并确定了实现最佳性能的FinFET侧墙厚度和源漏外延形状组合。

图1. 三种结构的关键工艺步骤比较

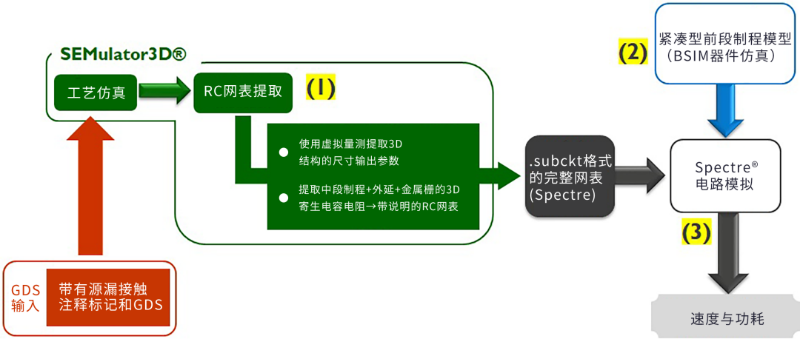

图2对本研究方法进行了图解。我们在建模中使用三种软件:SEMulator3D、BSIM紧凑型建模和Spectre®电路模拟。首先将一个GDS输入文件导入SEMulator3D,以便进行工艺模拟和RC网表提取。然后从SEMulator3D中提取各种数据,包括几何和寄生数据,以创建带说明的RC网表。该网表随后与BSIM紧凑型前段制程 (FEOL) 器件模型相耦合,并被输入到Spectre电路模拟模型。该Spectre模型随后用于模拟正在评估的三种不同反向器的速度和功耗。

图2. 本研究方法的流程图

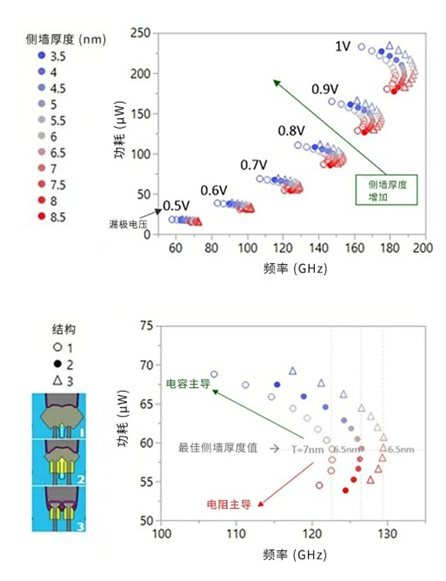

图3显示了三种结构(在不同的漏极间电压和侧墙厚度下)的功耗与频率的函数关系。我们注意到在不同漏极间电压下,所有外延形状几何都呈类似的功耗-速度趋势:侧墙厚度增加导致功耗降低。每个外延尺寸都有一个可产生最大速度和最佳Reff×Ceff值(有效电阻值x有效电容值)的最佳侧墙厚度。在各种侧墙厚度下,有一个特定的外延形状也提供了最高的整体性能。我们还研究了NMOS和PMOS结构最佳侧墙厚度下三种结构的源漏接入电阻(S/D-R)和栅极到源漏(GT-S/D)的电容,以便更好地了解图3中报告的结果。

图3.三个反向器在漏极电压为0.5V到1V时的功耗-速度比较(a)和放大后的漏极电压等于0.7V时的功耗-速度比较(b)

这种建模方法为FinFET工艺变化对5nm以下器件和电路性能的影响提供了有价值的指导。我们通过RC网表提取将SEMulator3D与BSIM紧凑型建模和Spectre电路模拟相耦合,成功评估和比较了三种不同反向器几何(使用不同侧墙厚度)工艺流程变化的效果,以实现最佳晶体管性能,还探讨了漏极间电压和低介电常数材料侧墙变化对速度和功耗性能的影响。

近期会议

2022年5月24日,由ACT雅时国际商讯主办,《半导体芯科技》&CHIP China晶芯研讨会将在苏州·金鸡湖国际会议中心隆重举行!届时业内专家将齐聚苏州,与您共探半导体制造业,如何促进先进制造与封装技术的协同发展。大会现已启动预约登记,报名链接http://w.lwc.cn/s/ZFRfA3

关于我们

《半导体芯科技》(Silicon Semiconductor China, SiSC)是面向中国半导体行业的专业媒体,已获得全球知名杂志《Silicon Semiconductor》的独家授权;本刊针对中国半导体市场特点遴选相关优秀文章翻译,并汇集编辑征稿、国内外半导体行业新闻、深度分析和权威评论、产品聚焦等多方面内容。由雅时国际商讯(ACT International)以简体中文出版、双月刊发行一年6期。每期纸质书12,235册,电子书发行15,749,内容覆盖半导体制造工艺技术、封装、设备、材料、测试、MEMS、IC设计、制造等。每年主办线上/线下 CHIP China晶芯研讨会,搭建业界技术的有效交流平台。

审核编辑:汤梓红

-

第1集|彻底绕过光刻机,“雕版印刷术”也能搞定5nm芯片? #芯片 #5nm工艺 #硬声创作季Hello,World! 2022-10-05

-

全包围栅极结构将取代FinFET2022-08-01 2118

-

5nm及更先进节点上FinFET的未来:使用工艺和电路仿真来预测2022-05-27 910

-

5nm及更先进节点上FinFET的未来:使用工艺和电路仿真来预测下一代半导体的性能2022-05-07 8722

-

被淘汰的FinFET 5nm之后的芯片该如何制造2021-08-25 5548

-

被淘汰的FinFET,5nm之后的芯片该如何制造?2021-08-19 6298

-

从7nm到5nm,半导体制程 精选资料分享2021-07-29 8368

-

5nm手机芯片功耗过高?2021-02-04 5433

-

造时工艺不成熟5nm 芯片集体 “翻车”,从 7nm 到 5nm 的尴尬2021-01-20 42853

-

全球进入5nm时代2020-03-09 3639

-

5nm节点上为什么STTMRAM比SRAM更好?2019-10-18 2084

-

台积电5nm架构设计试产2019-04-24 4143

-

三星使用EUV成功完成5nm FinFET工艺开发2019-04-18 7504

-

Platform 中的多项工具已通过TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证2018-05-17 4693

全部0条评论

快来发表一下你的评论吧 !