SiC共源共栅在困难条件下的性能解析

描述

本文探讨了SiC共源共栅在困难条件下(包括雪崩模式和发散振荡)的性能,并研究了它们在利用零电压开关的电路中的性能。

碳化硅(SiC)共源共栅具有主要特性,如芯片面积的归一化导通电阻(RDSA)、器件电容和易于栅极驱动。然而,设计师们非常谨慎,他们明白头条新闻并不总是故事的全部。我们很自然地对改变几十年来被证明很强大的技术持谨慎态度,例如IGBT,但这些设备在电压应力和外部故障的真实动态条件下的作用是一个特别值得关注的领域。

超越雪崩

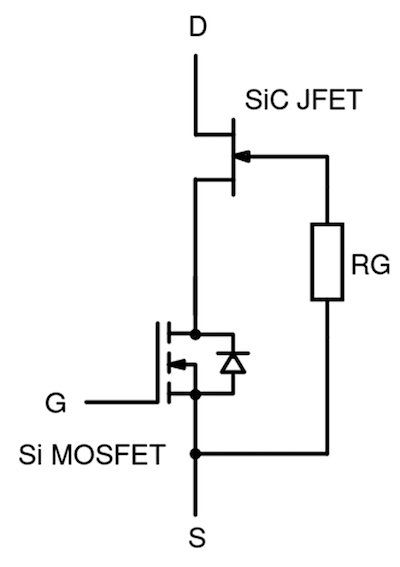

级联共源共栅的优点在于使用了低压Si-MOSFET,它与常开SiCJFET结合使用,使器件具有整体低导通电阻、快速体二极管和易于栅极驱动(图1)。

图1.SiC级联

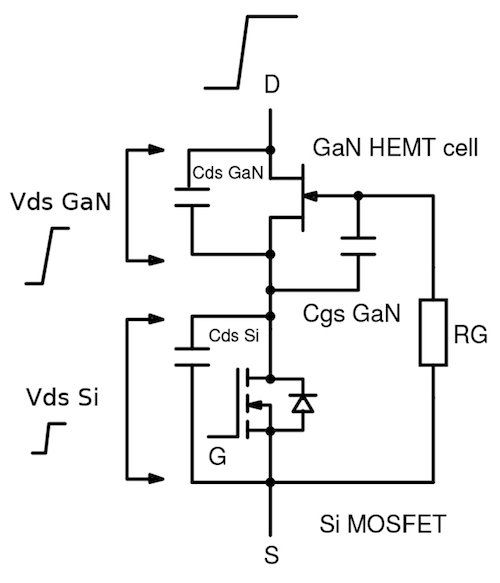

有些人可能会担心,MOSFET可能会动态地看到高漏极电压,并在被驱动关闭时在正常运行中进入雪崩模式。这会导致额外的损失甚至设备故障吗?在由横向结构的GaNHEMT单元形成的级联中,这是一种真正的可能性,因为GaN器件的有限漏源电容CDS与Si-MOSFET的CDS形成“下降”,并且可以动态地留下高压在MOSFET漏极上(图2)。然而,SiC共源共栅中的SiCJFET不同,由于它们的垂直“沟槽”结构,SiC-JFETCDS值非常小,因此Si-MOSFET几乎不会看到来自下拉效应的高压。

图2.SiMOSFET和GaNHEMT单元的级联排列,电压动态“下降”,在Si-MOSFET漏极上留下高电压

拥抱雪崩

但在某些情况下,雪崩是可取的,以保护设备免受感性负载产生的瞬态影响。GaN共源共栅没有雪崩额定值,只会因过压而失效,而SiC共源共栅JFET的栅漏二极管发生击穿,使电流通过RG,降低电压以打开JFET。Si-MOSFET现在会发生雪崩,但如果雪崩二极管内置在每个单元中,则以受控方式进行。为了消除对这种蓄意雪崩效应可能造成破坏的担忧,UnitedSiC等制造商通过在150°C下偏向雪崩的部件证明了这一点,该部件可以运行1000小时。作为一项额外的置信度测量,所有UnitedSiC部件在最终测试中都受到100%雪崩的影响。

SiC共源共栅保持零电压开关

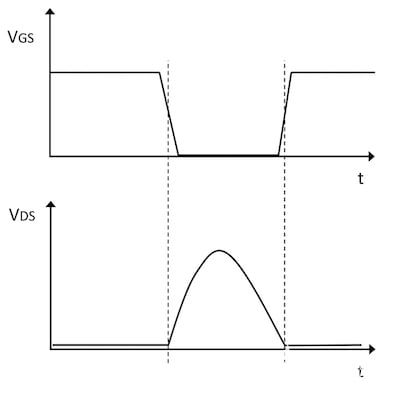

另一种情况是SiC共源共栅分数的低CDS出现在使用零电压开关(ZVS)的电路中;仅当负载电压以共振方式降至零伏时,才允许电源开关改变状态,从而实现无损转换(图3)。

图3.电压下降时的过渡产生零电压开关

如果共源共栅中高压开关的CDS值较高,则存在通过它的感应电流可以将其栅源电容与Si-MOSFET漏源电容一起放电的危险,从而使高压开关过早导通在漏极电压变为零之前。在这种情况下,ZVS丢失,功率耗散。SiC-CascodeJFET中没有CDS意味着该效应不会发生。

发散振荡

当级联第一次与用于高压和低压开关的分立器件组装时,发现了一种称为发散振荡的类似效应。不同封装中的不同技术设备通常来自不同的制造商,它们自然具有很高的杂散电容和连接电感,它们也有自己的容差。

X.Huang、FredLee和其他人[1]的工作表明,在大电流下关断时,高压开关的有限CDS值可能与封装电感发生共振,从而导致电流注入共源共栅中点。电流可能会部分打开高压开关,从而降低有效谐振电容,从而增加电路特性阻抗。这具有增加谐振摆动幅度的效果。

结果是失控或“发散”振荡,可能导致耗散和设备故障(图4)。该论文提出在中点使用耗散RC缓冲器是一种解决方案,但实际上发现只有一个电容器是有效的。不过,这必须是几个纳法拉,并且确实会导致一些额外的损失,尤其是在高频下。具有接近零CDS的SiC共源共栅完全避免了该问题,并且高低压开关的共同封装将封装电感降低到较低值,同时允许利用共源共栅的全部高频能力。

图4.发散振荡

碳化硅级联是稳健的

当Si-MOSFET是为应用定制设计并与JFET共同封装时,SiC共源共栅会发挥最佳性能。以这种方式实现时,MOSFET不会承受电压应力并提供快速体二极管。JFET有效地控制了器件的导通电阻和耐压特性,而这种组合提供了一定程度的鲁棒性,可抵御意外雪崩和其他技术(如超结MOSFET和GaNHEMT单元)所见的高CDS值的各种损耗诱导效应。

全部0条评论

快来发表一下你的评论吧 !