RISC-V处理器的优势是什么

描述

本文探讨了RISC-V的开源硬件模型背后的好处,讨论了它的寿命、可移植性和可靠性。

RISC-V用于嵌入式应用程序的势头是不可否认的。如今,RISC-V基金会拥有超过100家公司支持免费和开放的RISC-V指令集架构(ISA),随着越来越多的工具、软件、硬件和操作系统供应商加入,其成员数量也在迅速增长。凭借其不断扩大的生态系统,RISC-V为软件和硬件设计人员提供了一个令人信服的替代现有嵌入式处理器的替代方案,随着采用率的增长,在嵌入式设计中开启了处理器创新的新时代。

RISC-V开启新时代的原因归结为三个关键因素:寿命、便携性和可靠性。这三个原因都与RISC-V特别引人注目的原因有关。与通常在每一代都添加指令的已经建立的处理器架构不同,设计人员可以依靠带有RISC-V的固定ISA,确保他们的软件投资的寿命。这种寿命对于功能安全、认证和长产品生命周期很重要的嵌入式应用程序特别有利。

冻结的ISA

为了实现RISC-V的广泛使用并让市场决定处理器架构,RISC-V背后的加州大学伯克利分校工程团队在2014年第25届热芯片研讨会上介绍该技术前不久冻结了ISA。随着2015年,非营利性RISC-V基金会成员的任务是指导HW/SW规范和生态系统的未来发展,以及推动ISA的采用。随着基本ISA的确定和可选扩展的可用,设计人员可以实施针对其特定工作负载量身定制的处理器,而不必围绕标准的、现成的处理器设计进行工作,这种设计几乎没有任何定制空间。

许多RTOS和完整的操作系统现在都支持RISC-V。由于Linux操作系统的使用越来越多,RISC-V对嵌入式应用程序特别有吸引力。这使设计人员能够迅速采用ISA作为直接本地硬件实现的新开放标准架构。然而,即使不使用Linux,ISA所提供的冻结架构、寿命、可移植性和可靠性也是需要考虑的关键因素。

RISC-V扩展

冻结的ISA意味着软件可以开发一次并在任何支持正在使用的扩展(如果有)的RISC-V设备上无限期运行。扩展是添加新指令的唯一方法。目前,有五个扩展名,也已被冻结。这些扩展包括:

M表示整数乘除。

A原子指令

F表示单精度浮点

D表示双精度浮点

C用于压缩指令

RISC-V处理器优势

这种可预测性和简单性对处理器设计和软件开发有很多好处。让我们一一来看看。

长寿

RISC-VISA提供了一个稳定、干净的设计平台,在用户和特权模式之间有清晰和安全的分离,因为ISA是固定的并且包含少于50条指令。如果全部实现多个标准扩展,总数仍不足200个。不是引入新版本的ISA,而是通过扩展对标准指令集进行添加,便于未来设计增加稳定性。更少的指令意味着可以创建更简单的架构,从而提高处理器实施的成本效益和功率效率。对于软件开发人员来说,这意味着保留投资。一次编写软件并在任何RISC-V内核上永久运行。这对于必须支持数十年的产品寿命长的产品通常至关重要,

可移植性

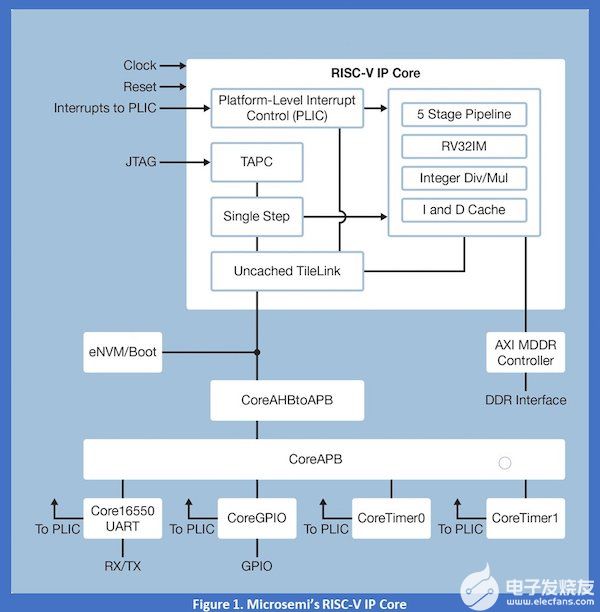

RISC-V使设计更容易扩大到大批量。例如,设计可以在运行软RISC-V内核的FPGA中开始发货(图1)。由于该软件将在任何具有RISC-V内核的设备上完全可移植,因此设计人员拥有本质上是“免版税”的处理器子系统RTL代码,可以在硬件中实现。设计人员可以修改、调整和迁移他们的设计到最适合他们产品的平台。如果选定的FPGA需要更换为下一代器件,则无需重新编写软件代码。现有的源RTL只需重新定位到另一个FPGA。此外,如果数量达到足够高的水平,则可以将相同的RTL源重新定位到ASIC,而无需支付任何特许权使用费。

图2.RISC-VIP内核图表。

可靠性和安全性

RISC-V的灵活性实现了独特的解决方案,特别是对于需要功能安全的嵌入式设计。例如,在具有多个功能等效内核的系统中,这些内核自主设计以实现终极冗余。一个这样的内核可能是MicrosemiMi-VRV32IM,另一个内核可能是功能相同但完全不同的内部设计。RISC-V还允许在微架构上完全灵活;因此一个内核可以为数据和指令高速缓存提供单事件翻转(SEU)保护措施。可以使用许多其他安全预防技术,因为RISC-V允许访问RTL。

虽然Intelx86和ARM处理器架构的成熟变体不太可能很快消失,但鉴于设计人员必须自由定制,RISC-V处理器生态系统已准备好在嵌入式市场快速增长。处理器架构的设计本质上是灵活的,因此实现可以在硬件中加速某些操作,或者,例如,专门针对低功耗进行优化。设计人员还可以灵活地连接他们想要的任何总线接口,而不是仅仅依赖于成熟的处理器供应商提供的总线。由于ISA的固定性质,RISC-V微体系结构的任何变化都是可以接受的。

RISC-V资源

要为您的下一个设计了解更多关于RISC-V的信息,可以从几个地方开始。

有关RISC-V及其成员的背景信息,请访问RISC-V基金会网站。如果您想直接投入并开始为RISC-V内核编写C代码,请访问Microsemi的Github站点并查看IGLOO2创意开发板RISC-V项目。Microsemi是第一家提供开放架构RISC-VIP内核和综合软件IDE解决方案的FPGA供应商。设计人员可以在多个基于闪存的FPGA中部署RISC-VIP内核,包括PolarFireFPGA、IGLOO2和RTG4设备。Mi-VCreative板(图2)包含一个IGLOO2FPGA,预编程了一个RISC-V内核,可以开箱即用地运行“helloworld”。

对于软件代码开发,托管在Linux或Windows平台上的基于Eclipse的软控制台集成开发环境(IDE)提供了完整的开发支持,包括C或C++编译器和调试器功能。MicrosemiRISC-VIP内核、LiberoSoC开发软件和软控制台IDE都可以从MicrosemiGithub站点免费下载。

凭借其冻结的ISA、简单性、可移植性和可靠性,RISC-V为设计人员提供了一种全新的处理器范例,以超越既定处理器现状的限制并突破创新的界限。

-

浅析RISC-V领先ARM的优势2024-06-27 1344

-

fpga和risc-v处理器的区别2024-03-27 2859

-

基于形式的高效 RISC-V 处理器验证方法2023-07-10 1812

-

香山处理器 RISC-V的典范2023-04-14 775

-

RISC-V和开源处理器之间是什么关系?2023-03-09 835

-

从零开始写RISC-V处理器2022-03-17 3282

-

RISC-V系列处理器的相关资料推荐2022-02-28 1384

-

RISC-V开源处理器核介绍2021-07-23 2414

-

基于RISC-V指令集Egret系列处理器的性能及应用场景2021-06-22 2776

-

RISC-V是什么?如何去设计RISC-V处理器?2021-06-18 2736

-

RISC-V是通用RISC处理器还是可定制的处理器?2020-11-17 4520

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4366

-

关于RISC-V和开源处理器的一些解读2020-06-22 2249

-

晶心科技推出突破性的RISC-V 27系列处理器及向量扩展指令处理器2020-01-03 3704

全部0条评论

快来发表一下你的评论吧 !