FPGA中流水线的原因和方式

描述

本文解释了流水线及其对 FPGA 的影响,即延迟、吞吐量、工作频率的变化和资源利用率。

对FPGA(现场可编程门阵列)进行编程是一个定制其资源以实现特定逻辑功能的过程。这涉及使用 FPGA 的基本构建块(如可配置逻辑块(CLB)、专用多路复用器等)对程序指令进行建模,以满足数字系统的要求。

在设计过程中,要考虑的一个重要标准是系统固有的时序问题,以及用户规定的任何约束。可以帮助设计人员实现这一目标的一种设计机制是流水线。

什么是流水线?

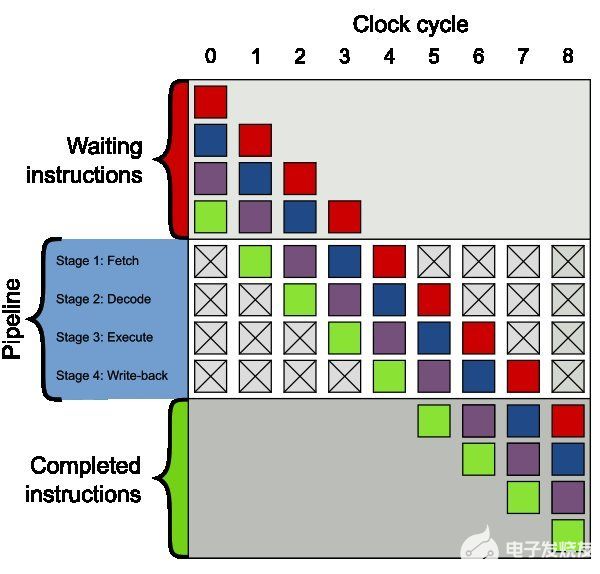

流水线是一种能够并行执行程序指令的过程。您可以在下面看到流水线处理器架构的可视化表示。

图 1.

流水线处理器架构的可视化表示。每个方块对应一条指令。正方形使用不同颜色传达了指令相互独立的事实。图片由

Colin ML Burnett

[

CC-BY-SA-3.0

] 提供。

在 FPGA 中,这是通过以特定方式排列多个数据处理块来实现的。为此,我们首先将整个逻辑电路分成几个小部分,然后使用寄存器(触发器)将它们分开。

让我们通过一个例子来分析一下FPGA设计流水线化的模式。

一个例子

让我们看一下在四个输入数组上进行三个乘法和一个加法的系统。因此,我们的输出y i 将等于 ( a i × b i × c i ) + d i。

非流水线设计

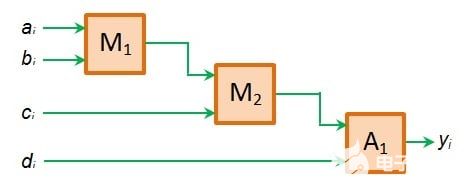

想到创建这样一个系统的第一个设计是乘法器,然后是加法器,如图 2a 所示。

图 2a。

非流水线 FPGA 设计示例。图片由 Sneha HL 创建

在这里,我们期望操作序列是 a i 和 b i 数据乘以乘数 M 1,然后是其乘积与 c i 乘以乘数 M 2 ,最后将结果乘积与 d i 相加加法器 A 1。

然而,当系统设计为同步时,在第一个时钟滴答时,只有乘法器 M1 可以在其输出端产生有效数据 ( a 1 × b 1 )。这是因为,此时,与 M 2 和 A 1不同,只有 M 1在其输入引脚处 具有有效数据(a 1 和 b 1 ) 。

在第二个时钟节拍中,M 1和 M 2的输入引脚上都会有有效数据。但是,现在我们需要确保只有 M 2运行,而 M 1保持其输出不变。这是因为,此时,如果 M 1运行,则其输出线变为 ( a 2 × b 2 ) 而不是其预期值 ( a 1 × b 1 ),从而导致错误的 M 2输出 ( a 2 × b 2 × c 1 ) 而不是 ( a 1 × b 1 × c 1 )。

当时钟第三次滴答作响时,所有三个组件都会有有效输入:M 1、M 2和 A 1。尽管如此,我们只希望加法器能够运行,因为我们期望输出为 y 1 = ( a 1 × b 1 × c 1 + d 1 )。这意味着系统的第一个输出将在第三个时钟滴答之后可用。

接下来,随着第四个时钟滴答的到来,M 1可以对下一组数据进行操作:a 2和b 2。 但此时,M 2和 A 1预计空闲。这之后必须在第五个时钟节拍激活 M 2 -只有 M 2 - 在第六个时钟节拍激活 A 1 -只有A 1。这确保了我们的下一个输出, y 2 = ( a 2 × b 2 × c 2 + d 2)。

当组件遵循类似的激励模式时,我们可以预期下一个输出发生在时钟节拍 9、12、15 等处(图 2b)。

图 2b。

流水线设计

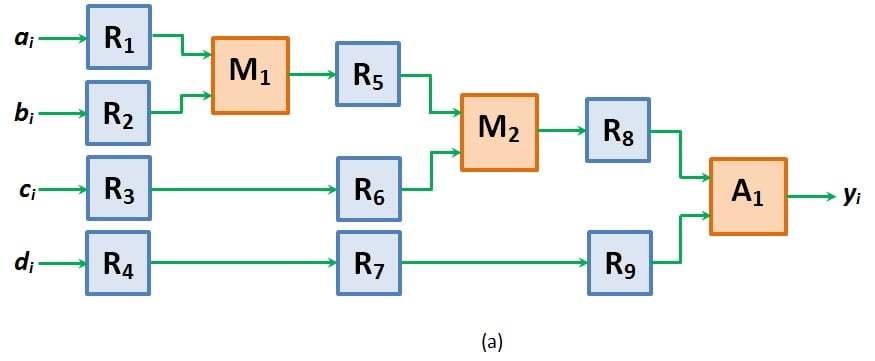

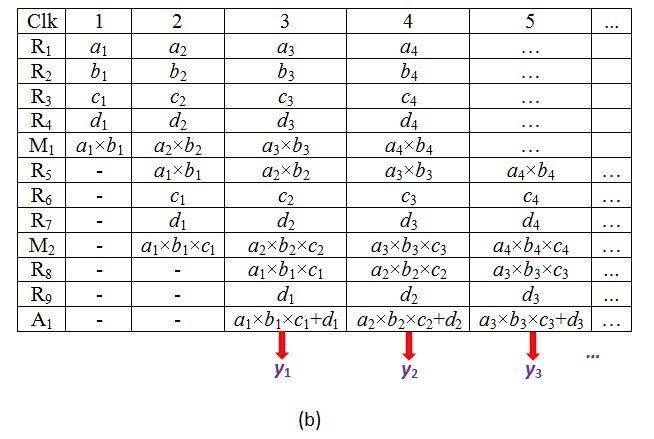

现在,假设我们在输入(R 1到 R 4)、M 1和 M 2之间(分别为 R 5和 R 8)以及沿直接输入路径(R 6、R 7、和 R 9 ),如图 3a 所示。

图 3a。

流水线 FPGA 设计示例。Sneha HL 创建的图像和表格

这里,在第一个时钟滴答声中,有效输入仅出现在寄存器 R 1到 R 4(分别为 a 1、b 1、c 1和d 1)和乘法器 M 1(a 1和b 1)。结果,只有这些才能产生有效的输出。此外,一旦 M 1产生它的输出,它就会被传递到寄存器 R 5并存储在其中。

在第二个时钟滴答声中,存储在寄存器 R 5和 R 6(a 1 × b 1和c 1)中的值显示为 M 2的输入,这使其能够将其输出呈现为a 1 × b 1 × c 1,而R 4 ( d 1 ) 的输出被转移到寄存器R 7。同时,即使是第二组数据(a 2、b 2、c 2和d 2) 进入系统并出现在 R 1到 R 4的输出端。

在这种情况下,允许 M 1对其输入进行操作,以使其输出线从a 1 × b 1变为a 2 × b 2,这与非流水线设计的情况不同。这是因为,在本设计中,M 1输出的任何变化都不会影响 M 2的输出。这是因为确保 M 2正确功能所需的数据在第一个时钟节拍期间已经锁存在寄存器 R 5中(并且即使在第二个时钟节拍时也保持不受干扰)。

这意味着寄存器 R 5的插入使 M 1和 M 2在功能上独立,因此它们都可以同时对不同的数据集进行操作。

接下来,当时钟第三次滴答作响时,寄存器R 8和R 9的输出(( a 1 × b 1 × c 1 )和d 1 )作为输入传递给加法器A 1。结果,我们得到第一个输出y 1 = (( a 1 × b 1 × c 1 ) + d 1 )。尽管如此,在同一时钟滴答声中,M 1和 M 2将可以自由操作 ( a 3 , b 3) 和 ( a 2 , b 2 , c 2 )。这是可行的,因为存在将块M 1与M 2隔离的寄存器R 5和将乘法器M 2与加法器A 1隔离的R 8。

因此,在第三个时钟滴答处,我们甚至可以分别从 M 1和 M 2得到 ( a 3 × b 3 ) 和 ( a 2 × b 2 × c 2 ) ,除了y 1。

现在,当第四个时钟滴答到达时,加法器 A 1 对其输入进行运算以产生第二个输出,y 2 = (( a 2 × b 2 × c 2 ) + d 2 )。此外,M 1的输出从 ( a 3 × b 3 ) 变为 ( a 4 × b 4 ),而 M 2的输出从 ( a 2 × b 2 × c 2 ) 变为 ( a 3 × b3 × c 3 )。

在遵循相同的操作模式时,我们可以预期从那时起每个时钟滴答都会出现一个输出数据(图 3b),这与非流水线设计的情况不同,在非流水线设计的情况下,我们必须等待三个时钟周期才能获得每个输出数据(图 2b)。

流水线的后果

潜伏

在所示示例中,流水线设计显示为从第三个时钟周期开始为每个时钟节拍产生一个输出。这是因为每个输入必须经过三个寄存器(构成流水线深度),同时在到达输出之前进行处理。类似地,如果我们有一个深度为n的管道,那么有效输出仅从第n个时钟滴答开始在每个时钟周期出现一个。

这种与第一个有效输出出现之前丢失的时钟周期数相关的延迟称为延迟。流水线阶段的数量越多,与之相关的延迟就越大。

增加工作时钟频率

图 2a 所示的非流水线设计每三个时钟周期产生一个输出。也就是说,如果我们有一个周期为 1 ns 的时钟,那么输入需要 3 ns (3 × 1 ns) 来处理并显示为输出。

然后这条最长的数据路径将成为关键路径,它决定了我们设计的最小工作时钟频率。换言之,所设计系统的频率必须不大于 (1/3 ns) = 333.33 MHz,以确保令人满意的操作。

在流水线设计中,一旦流水线填满,每个时钟滴答都会产生一个输出。因此我们的工作时钟频率与定义的时钟频率相同(此处为 1/1ns = 1000 MHz)。

这些数字清楚地表明,与非流水线设计相比,流水线设计大大增加了操作频率。

吞吐量增加

流水线设计每个时钟周期产生一个输出(一旦克服延迟),无论设计中包含的流水线级数如何。因此,通过设计流水线系统,我们可以提高 FPGA 的吞吐量。

更好地利用逻辑资源

在流水线中,我们使用寄存器来存储设计各个阶段的结果。这些组件增加了设计使用的逻辑资源,使其在硬件方面非常庞大。

结论

流水线化设计的行为非常详尽。您需要在适当的时刻将整个系统划分为各个阶段,以确保最佳性能。尽管如此,投入其中的辛勤工作与其在设计执行时所呈现的优势相当。

-

什么是流水线 Jenkins的流水线详解2023-05-17 1776

-

流水线寄存器问题2021-11-20 5616

-

嵌入式_流水线2021-10-20 1267

-

如何选择合适的LED生产流水线输送方式2021-08-06 1483

-

各种流水线特点及常见流水线设计方式2021-07-05 10074

-

FPGA中的流水线设计2020-10-26 3263

-

FPGA之流水线练习5:设计思路2019-11-29 3355

-

FPGA之为什么要进行流水线的设计2019-11-28 4412

-

请教verilog中流水线技术的用途?2017-09-26 3922

-

电镀流水线的PLC控制2016-02-17 1321

-

关于fpga流水线的理解2015-08-15 7405

-

流水线中的相关培训教程[1]2010-04-13 1281

-

FPGA重要设计思想及工程应用之流水线设2010-02-09 1114

-

什么是流水线技术2010-02-04 4408

全部0条评论

快来发表一下你的评论吧 !