FPGA如何为以太网和千兆以太网解决低功耗问题

描述

探索新的中档 FPGA 如何为以太网和千兆以太网 (GbE) 链路执行桥接功能,同时解决低功耗问题。

虽然 FPGA 通常用于为以太网和千兆以太网 (GbE) 链路执行桥接功能,但它们通常与低功耗相关联。以下是在以太网需求不断增加和外形尺寸减小的时代,新的中档 FPGA 如何解决这个问题的探索。

在当今日益互联的世界中,各种工业、通信和数据中心应用对以太网和其他千兆以太网 (GbE) 链路的需求不断增长。FPGA 通常用于执行 GbE 接口的桥接功能,因为它们的设计成本低、性能高、上市速度快、可重用性以及快速灵活的现场升级组合。

直到最近,它们才以设计人员需要的低功耗和易用性而闻名,如果他们要使用单个 FPGA 来创建当今包含许多不同 10G 和 1G 接口的混合解决方案。这一切都随着中端 FPGA 的最新迭代而改变,它在单个设备中提供多个 GbE 端口,无需收发器即可实现节能 1G 接口,从而显着降低功耗。

专为高能效 GbE 接口而构建

支持 10 Mbps、100 Mbps、1 Gbps 和 10 Gbps 速度的传统中档 FPGA 有助于推动对单个产品中更多连接的需求。这些具有 1G 接口的高端 FPGA 面临的挑战是需要收发器,从而增加功率和封装尺寸。随着新的中档 FPGA 设备的出现,这种情况已不再存在,这些设备提供了使用通用输入输出 (GPIO) 实现多个 GbE 接口的更具可扩展性的选项。这更加节能,并且还使开发人员能够将收发器的使用保留用于采用 10-Gb/s 以太网、CPRI、JESD204B 和 PCIe 等协议的高速系统实施。

GPIO 在当今的中档 FPGA 设备中很容易使用。它们由每个引脚后面的高度可配置的接收器和驱动器电路支持,并且可以动态调整信号延迟(包括与时钟传动比相关的延迟)。它们实现了每引脚时钟和数据恢复 (CDR) 电路功能,并支持流行的 I/O 标准和终端。

系统实施

如今,通过配置一对差分 GPIO 输出引脚和一对差分 GPIO 输入引脚,可以实现许多关键的 GbE 接口功能。这些功能包括串行器、解串行器和 CDR,以及用于符号对齐的位滑动功能。硬化的 GPIO 电路与物理编码子层 (PCS)、媒体访问控制 (MAC) 和在 FPGA 架构中实现的更高层无缝连接,从而产生高度可配置的 GbE 解决方案。GPIO 支持各种 I/O 标准,额定电压在 1.2 V 至 3.3 V 之间,单端标准速度高达 1.066 Gbps,差分标准速度高达 1.25 Gbps。

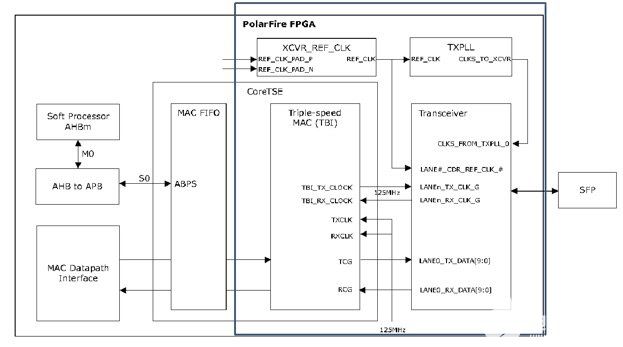

以下高级框图显示了如何使用相同的 FPGA 器件实现两种不同的 1 GbE 解决方案,一个通过 GPIO,另一个通过收发器。

图 1. 使用 Microsemi PolarFire FPGA 通过 GPIO 实现 1 GbE。

图 2. 使用 Microsemi PolarFire FPGA 在收发器上实现 1 GbE。

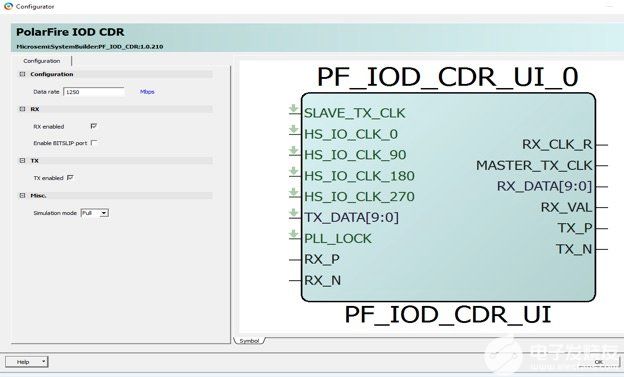

在第一个示例中,片上系统 (SoC) FPGA 设计软件工具用于通过 GPIO 实现接口功能。FPGA 的以太网接口 IP 包括一个内核,该内核结合了 GPIO 和 CDR,该内核可用于设备的每个 GPIO bank 通道,为 1 GbE 数据传输速率提供时钟和数据恢复。器件的每一侧都可以有多个内核共享来自位于 FPGA 架构角落的锁相环 (PLL) 的高速信号。GPIO 内核从软件套件的目录中实例化,然后通过选择数据速率(在本例中为 1250 Mbps)进行配置。它与 PLL 内核和 MAC 发送和接收逻辑相结合来完成设计。GPIO 内核的快照如下图所示。

图 3. GPIO 内核 GUI 配置器。

功率比较

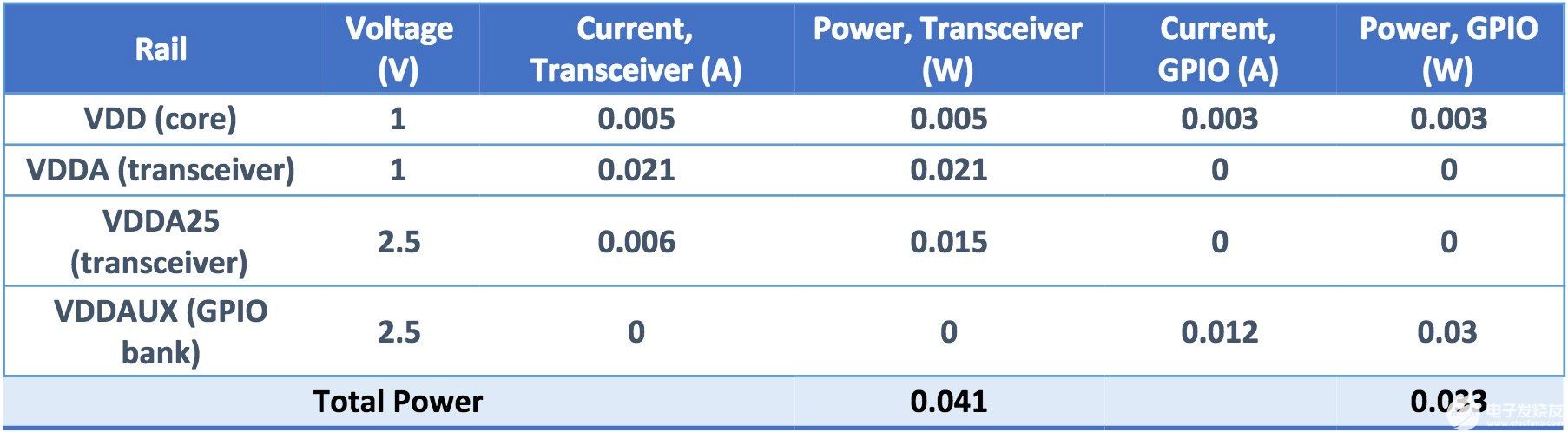

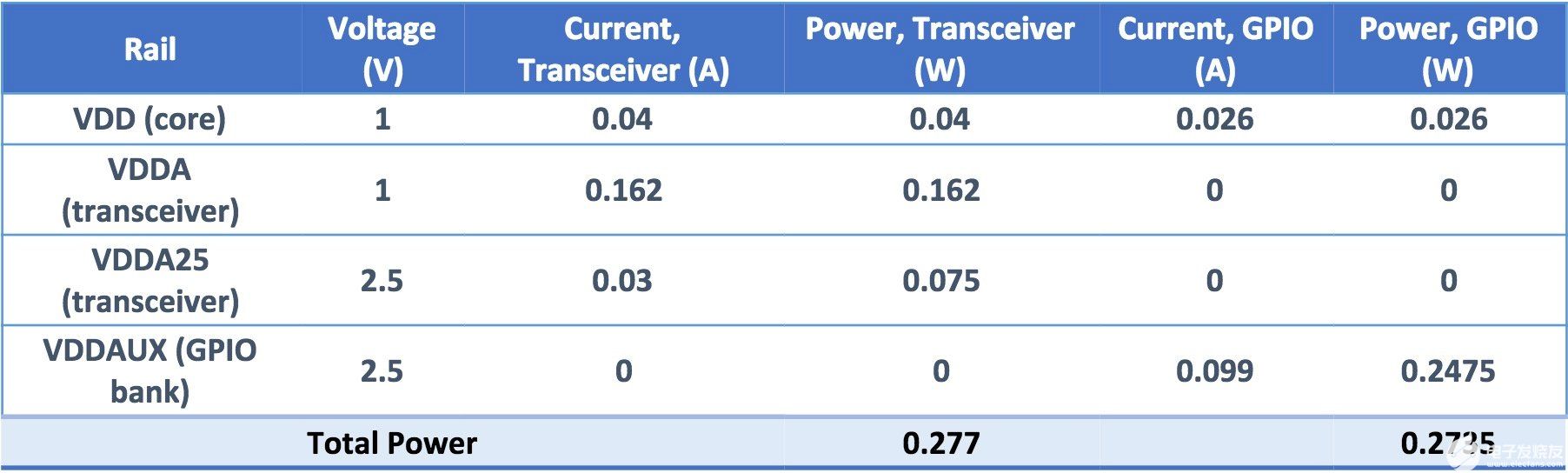

虽然为 GbE-over-GPIO 实现实例化以太网接口 IP 与为收发器实现实例化收发器内核、收发器 PLL 和参考时钟之间的架构资源可用性没有差异,但比较电源效率是另一回事。GPIO CDR 的功耗低于收发器,从而降低了使用多个 GbE 链路的应用的功耗。为了比较基于收发器的实现与基于 GPIO 的实现的功率数,我们使用了 PolarFire MPF300T 设备(FCG1152 封装)的预先(基于模拟的初始估计信息)功率数。

下表列出了单通道 GPIO 或单通道收发器、8 通道 GPIO 或 8 通道收发器以及 16 通道 GPIO 或 16 通道收发器的不同电源轨的总功耗。

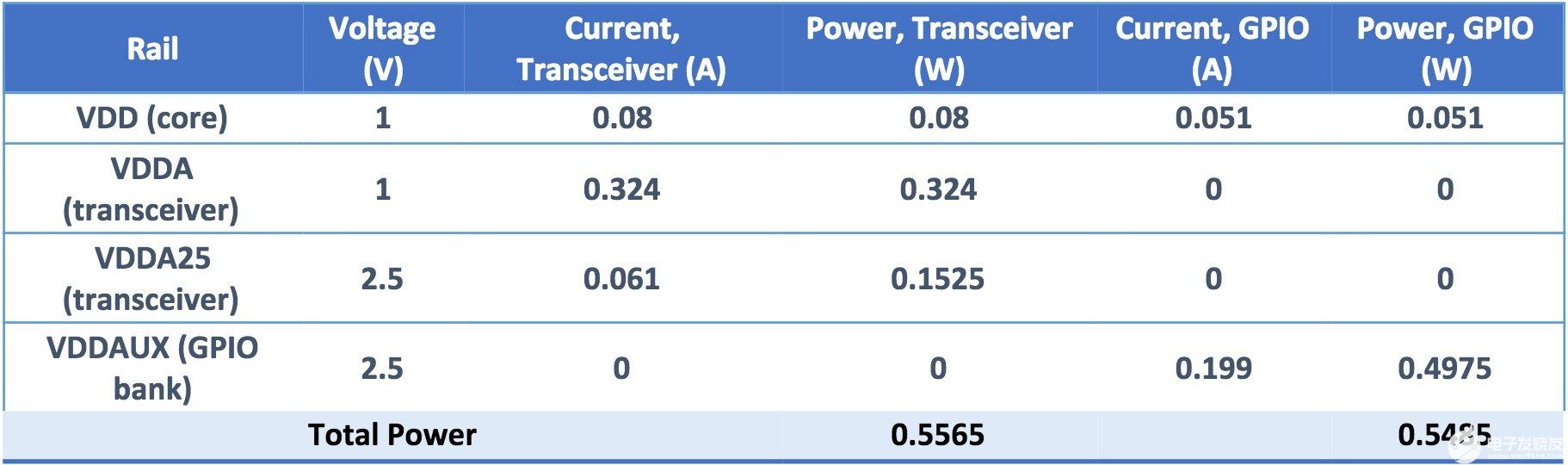

表 1:功率比较——1 个收发器通道与 1 个 GPIO 通道

表 2:功率比较——8 通道收发器与 8 通道 GPIO

表 3:功率比较——16 通道收发器与 16 通道 GPIO

SGMII over GPIO 提供更多优势

最新的中档 FPGA 还通过在 GPIO 上实施串行千兆位媒体独立接口 (SGMII) 来支持众多 1Gbps 以太网链路。

过去,如果设计人员采用更大的封装和额外的收发器,他们只能使用中档 FPGA 来实现基于 GPIO 的 SGMII。通常,他们不得不转向逻辑元件 (LE) 数量更多的 FPGA,从而增加了功耗和成本。但是,使用最新的中档 FPGA,很容易实现 SGMII-over-GPIO,与使用收发器实现 SGMII 相比,所需的配置块更少。基于 GPIO 的实现使用跨多个通道和存储体的共享 PLL,而收发器需要专用 PLL,从而降低了 GPIO 的总功耗。

查看下面的资源比较,很明显,使用 GPIO 可以实现比收发器更多的端口。使用 GPIO 的另一个优势是高速收发器通道可以保留用于其他协议,例如 10 GbE、CPRI、Interlaken 和 PCIe。

表 4:资源比较

提供的数据适用于 Microsemi PolarFire FPGA。

FPGA 可以成为将更多 GbE 接口封装到当今更小的系统占用空间中的理想解决方案,只要它们能够满足日益具有挑战性的电源要求。最新的中档 FPGA 通过提供通过 GPIO 使用结合了 GPIO 和 CDR 的 IP 内核来实现此接口功能的选项来实现这一点。

这种方法无需收发器即可在单个设备中提供多个 GbE 端口,可显着降低功耗,同时更容易实施具有多个 10G 和 1G 接口端口的混合高性能解决方案,并以非常低的增量扩展端口密度总功率增加。该方法对低功耗小型可插拔 (SFP) 模块、定制工业交换机、可扩展 L2/L3 交换机和其他系统的设计人员特别有吸引力,他们可以利用小尺寸和大量廉价、低- 当今中档 FPGA 解决方案提供的高功率和高效 GPIO。

-

#电子技术 #FPGA 千兆网以太网工程(项目开发能力)明德扬助教小易老师 2023-11-04

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

基于FPGA的UDP千兆以太网光通信2023-08-31 6674

-

简谈基于FPGA的千兆以太网设计2023-06-01 1337

-

如何快速分辨以太网与千兆以太网2022-05-06 6522

-

千兆以太网发展现状 千兆以太网技术优势2021-03-21 8920

-

千兆以太网发展现状_千兆以太网前景2020-04-20 2694

-

以太网的传播速率_以太网的传输介质2020-03-20 8416

-

简谈基于FPGA的千兆以太网2018-02-03 7087

-

基于Xilinx FPGA的嵌入式串行千兆以太网设计2017-11-23 4121

-

基于Xilinx FPGA的千兆以太网控制器的开发2015-01-23 31517

-

基于FPGA的十端口千兆以太网接口的设计与实现2009-08-29 735

-

ATM与千兆以太网的区别2009-05-25 5672

全部0条评论

快来发表一下你的评论吧 !