基于AD9280的高速采集电路设计方案

描述

针对大带宽采样需求,设计了基于AD9208的高速采集电路,通过分析时钟抖动,噪声等因素对采集电路的影响,设计了相关电路,包括低抖动时钟电路、模拟信号输入电路、电源电路,并测试了在不同输入频率下,AD9208的无杂散动态范围。

引 言

数字接收机在合成孔径雷达、无线电通信、以及仪器仪表等场合中占有重要地位。随着电子产业的发展,数字接收机对采样率、模拟信号输入带宽以及分辨率等要求越来越高,因此对模数转换电路的设计要求更加严格。目前高速采样系统设计达到Gsps以上,除模数转换器(ADC)本身性能指标要求外,在外围电路设计以及印刷电器板(PCB)布线上都有很高的要求,相关芯片大部分由国外制造,国内正处于发展期,相关技术需求越来越高,因此对高带宽、高分辨率的模数转换电路研究具有重要的意义。

本文选用ADI公司生产的3Gsps、14Bit ADC芯片AD9208,分析其性能参数以及相关影响因素,进行了采集电路设计,重点分析设计了时钟电路、模拟信号输入电和电源电路,保证时钟、模拟信号输入通道和电源满足设计要求。

1 采样电路影响因素分析

信噪比是采样电路最关键的性能指标,式(1)表示了信噪比与量化噪声,热噪声和时钟抖动的关系:

式中:tJ-Clock-Input来源于时钟电路;tJ-Analog-Input来源于模拟信号输入电路。

通过查询AD9208技术手册,tJ-Analog-Input=55fs,tJ-Clock-Input=0,fA =3GHz,将其代入式(4)可得到在3GHz理想模拟信号输入条件下,理想的采样电路信噪比σS/Nidea-adc=59.68dB。在采样电路设计中,为提高信噪比性能,应尽可能减少时钟抖动tJ-Clock-Input和模拟信号输入抖动tJ-Analog-Input。

2 采集电路分析与设计

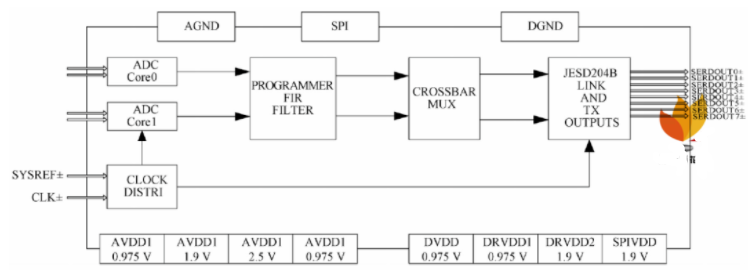

采集电路设计以AD9208为核心,其结构如图1所示,外部接口主要包括模拟信号输入,采样时钟输入,电源,以及SERDES传输所需要的时钟和传输通道。

图1 AD9208结构示意图

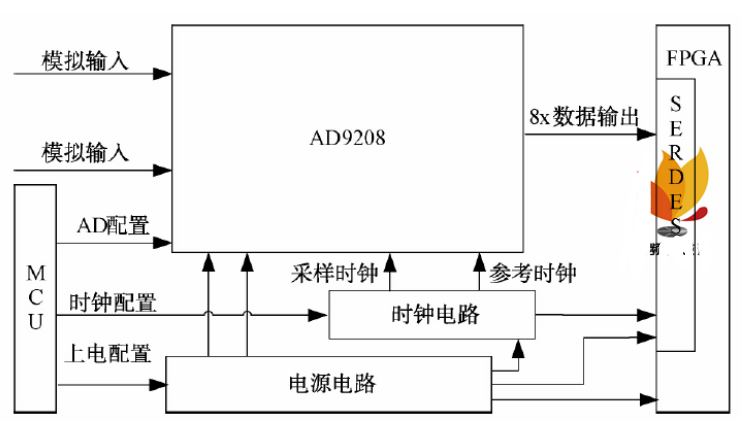

根据AD9208具体设计要求,设计的采集电路主要包括前端模拟输入电路、时钟电路、供电电路、数据接收电路和管理配置电路等,如图2所示。据第1节所述,时钟电路和模拟信号输入电路至关重要,同时电源供电是保证电路工作的重要因素,本节将进行详细分析和设计。

图2 采集电路原理示意图

2.1 时钟电路分析与设计

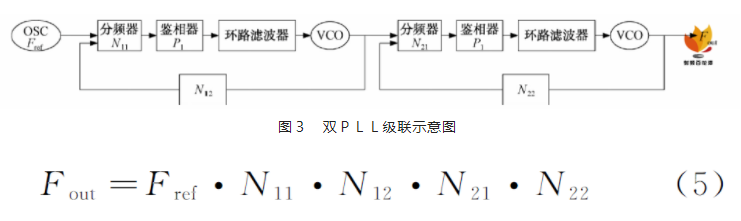

高速ADC需要1个低抖动的高频采样时钟,通常由时钟源和锁相环(PLL)电路产生,除选择良好的时钟源,PLL电路的设计至关重要,高速ADC需要的采样时钟带宽较高,因此可采用2级PLL结构,第1级PLL环路滤波器带宽较窄,滤除鉴相器输出的谐波分量,为PLL2提供了1个高精度、低相噪的参考时钟,以期PLL2为高速ADC提供大带宽、低抖动的采样时钟。PLL级联方式如图3所示.式(5)表示了输出频率Fout和时钟源频率Fref的关系:

任何时钟电路均会产生时钟抖动,时钟电路总抖动tJ-Clock-Input包括时钟源、PLL电路、分频电路等各种级联电路抖动的均方根。AD9028在3G理性模拟信号下信噪比σS/Nidea-adc =59.68dB,为保证设计要求,最终信噪比应在53dB以上,将σS/N = 53dB,tJ-Analog-Input=55fs,fA =3GHz,tJ-Analog-Input=0,代入式(3)和式(4)可计算出tJ-Clock-Input=95fs。因此在时钟电路设计时应选择时钟抖动在95fs以下的器件。

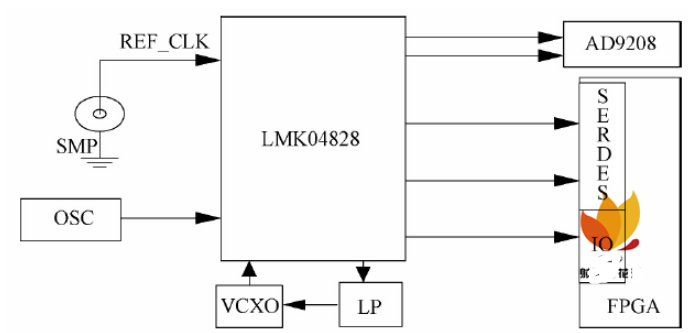

本设计中,为简化电路,选择Ti 公司的LMK04828,时钟抖动为90fs,满足时钟抖动要求。支持双PLL级联工作模式,且N11、N12、N21、N22可自动配置,锁定后时可以同时输出多路时钟,满足ADC采样、数据发送和FPGA 数据接收的时钟要求,保证时钟同步。图4为设计的时钟电路原理框图。

图4 时钟电路原理框图

2.2 模拟信号输入电路分析与设计

目前,用来驱动ADC 的方案主要有变压器和差分放大器2种。第一,变压器是无源器件,不需要消耗功率,且一般认为它引入的噪声是可忽略的。第二,差分放大器是有源器件,需要消耗能量,具有一定的谐波失真和较宽频带内的白噪声,会降低ADC的信噪比和有效分辨率。

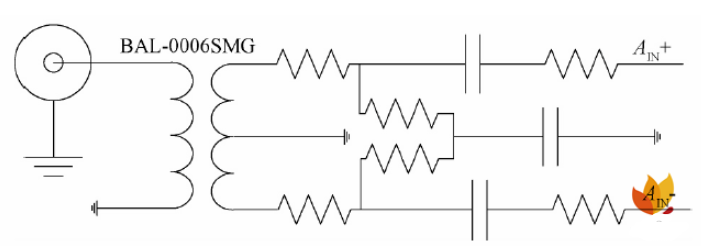

本次设计模拟信号从同轴电缆接插件中输入为单端信号,AD9208模拟输入通道为差分形式,虽然放大器也能实现该功能,但变压器为无源器件,并且具有电流隔离功能,带宽更宽,功耗低,且不引入噪声,对SNR没有影响。为满足AD9208信号输入带宽,选用型号为BAL-0006SMG的BALUN 射频变压器,阻抗50Ω。

在将模拟信号转换为差分信号后,需要进行阻抗匹配,根据AD9208输入阻抗要求,设计的模拟信号输入电路原理框图如图5所示。

图5 模拟信号调理框图

2.3 电源电路设计

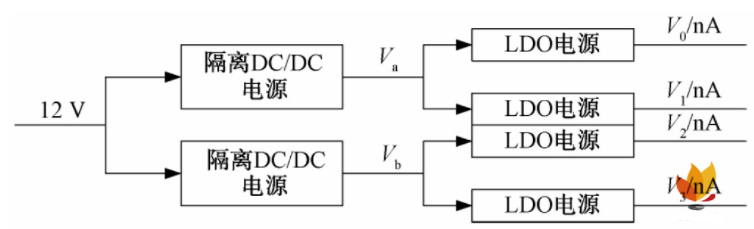

高速ADC电路设计中,要确保电源来源及目的端的电压及电流满足需求。一般会涉及多种电源,分布式电源架构往往更适合高速电路设计,即采用2级电源转换,第1级电源的目的是获得中间电源,同时为单板提供电源隔离保护,允许输出较大的纹波和噪声,第2级电源的目的是输出器件所需要的电源,重点是限制输出端的噪声和纹波。如图6所示。

图6 分布式电源框图

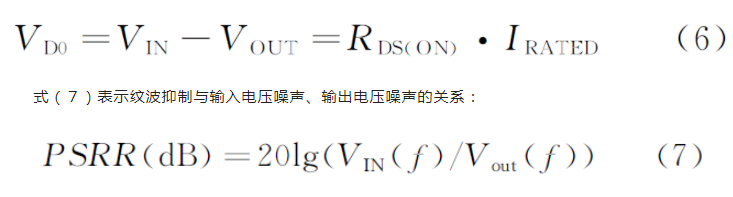

通用的电源包括开关型DC-DC和低压差线性稳压器(LDO),开关型DC-DC效率高,能实现隔离保护,LDO电源相对于DC-DC电源纹波小、稳定性高,但输出电流较小。显然在分布式电源架构中,第1级适合采用开关型DC-DC,以提供隔离保护和更高的转换效率,第2级电源采用LDO电源,以提供精确的电压和纹波抑制。在设计时,LDO电源电路为器件直接供电,应注意输出电压精度、压降、延时、散热、纹波抑制(PSRR)等。以TPS7A91为例,该器件在负载和温度范围内精度达1%,LDO功耗为输出电流与压降的乘积,在满足目的器件所需电压的情况下,应尽可能减少压降,其中包括合理降低输入电压,增加散热以降低电源温度,从而减少电源功耗,获取更高效率。式(6)表示了压降与额定电流的关系:

显然降低压降可以减少功耗,抑制纹波。因此在LDO电源设计时,在满足输出电压的要求下,应尽可能减少输入电压。

目前器件集成度越来越高,内部晶体管数量越来越大,受器件电源管脚数目限制,外部电源需给内部电路提供公共的供电节点,此时器件供电处的噪声会通过内部电路传播,影响器件内部工作稳定包括晶振、PLL、延时锁相环(DLL)的抖动特性,AD转换电路的转换精度,严重时甚至引起逻辑错误。器件供电引脚处的噪声主要来源于电源本身输出纹波,器件因逻辑转换产生的瞬态电流,电源无法实时响应目的器件对电流需求的快速变化,信号通过过孔换层引起的电源噪声。其中包括选用低纹波电源器件,在目的器件管脚处放置旁路电容作为电荷缓冲池以满足器件对电流需求的快速变化,滤波以消除噪声。

降低输出噪声VOUT(f),需提高电源的纹波抑制和降低输入噪声。除选用高纹波抑制电源器件,还需要在电源参考电压处增加合适的前馈电容。综上,电容在电源电路中占有十分重要的地位。

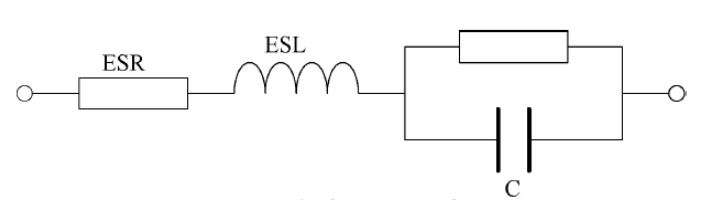

电容的本质是储存电荷和释放电荷,因此作为电荷缓冲池容易满足器件工作电压不随电流和功耗的剧烈变化而变化。同时电容阻抗Z =1/(jωC),频率不同,电容阻抗不同。高速设计中,电源噪声往往占据不同的频带,且电容并不是纯粹电容,同时包含电容分量和电阻分量,如图7所示。

图7 电容分量示意图

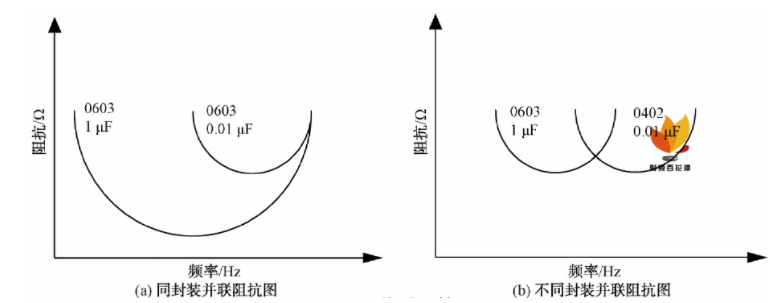

因此在选取不同电容增强滤波特性时,不仅考虑电容值,还应考虑封装和材料不同影响的其他特性。以某厂家提供的0603封装1μF,0603封装0.01μF,0402封装0.01μF阻抗曲线来分析,如图8所示,显然只选用0603封装1μF和0603封装0.01μF并未拓宽低阻抗频带,选用0603封装1μF和0402封装0.01μF可以拓宽低阻抗频带,并联放置相同电容可以获得更低阻抗。

图8 并联阻抗图

3 验 证

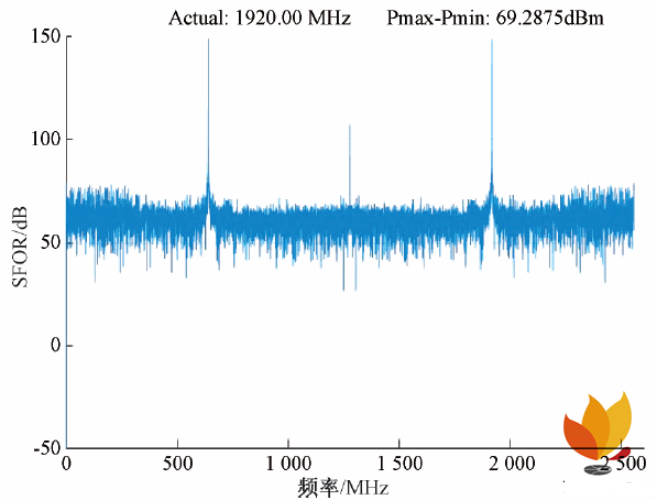

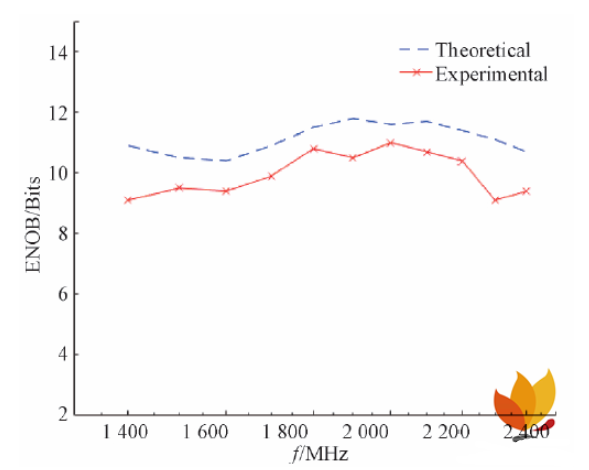

在完成板卡基础调试后,利用信号源产生步进100MHz的模拟信号,并将采集数据进行快速傅里叶变换(FFT),图9为1920MHz模拟信号输入下,计算得到的无杂散动态范围,图10将各频点得到的数据根据式(2)转换为有效位数曲线,可以验证电路采样位数在9.6~12 位,发挥了AD9208性能,满足设计要求,为后续数据处理提供了良好的平台。

图9 FFT数据图

图10 ENOB对照图

4 结束语

本文通过分析ADC信噪比性能影响因素,明确时钟抖动、信号输入对提高ADC性能有着重要的影响,详细分析和设计了时钟电路、模拟信号输入电路和电源电路。最后通过输入各频点模拟信号测试,对比AD9208手册提供的数据,验证了采集电路性能,为后续数据处理打下了基础。

作者:王德恒,刘文政

来源:舰船电子对抗

- 相关推荐

- 热点推荐

- 模拟信号

-

verilog 如何驱动AD9280采集电压2018-06-11 8645

-

请问AD9280做ad转换非线性很大是正常的吗?2018-08-15 4592

-

两片AD9280能否数据线接在一起靠三态引脚区分读数2019-01-09 2095

-

高速模数转换器MS9280参数和兼容AD92802022-05-13 21652

-

高速ADC,MS9280替代AD9280,P=P直接替代2022-05-17 5556

-

关于AD9280非线性的问题求解2023-12-13 589

-

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?2023-12-14 518

-

ad9280数据手册2016-12-26 1468

-

数模模数转换芯片AD92802022-07-06 1367

-

AD9280完整的8位32MSPS,95毫瓦cmos模数转换器2017-10-11 1160

-

AD9280 完整8位、32 MSPS AD2019-02-22 7630

-

485接口EMC电路设计方案2020-02-05 7869

-

小信号放大电路设计方案汇总2021-09-14 3543

-

AD9280模数转换芯片产品说明2021-11-03 1168

-

深入解析AD9280:8位、32 MSPS CMOS A/D转换器的卓越性能与应用2026-04-07 237

全部0条评论

快来发表一下你的评论吧 !