详解FPGA的时序input delay约束

详解FPGA的时序input delay约束

今日头条

描述

第一章 FPGA时序约束分享03_input delay约束

作者:潘文明

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

《FPGA时序约束分享01_约束四大步骤》概括性地介绍 了时序约束的四个步骤,对时序约束进行了分类,并得到了一个分类表。

《FPGA时序约束分享02_时钟约束》详细介绍了关于时钟的约束,根据时钟来源可以分成输入时钟约束、PLL等衍生时钟约束和自己分频的时钟约束等三种类型。这三种类型的约束方法均有所不同,读者需要掌握区分方法。

本文,笔者将详细介绍输入延时(input delay)的概念、场景分类、约束参数获取方法以及约束方法。

在高速输入设备与FPGA通信场合,设置输入延时(input delay)约束非常重要。

例如明德扬研发的高速ADC模块:mdyFmcAd9653,该模块集成了2个125M采样率、分辨率为16位的AD9653,采集数据时通过LVDS传输至FPGA上。该LVDS的时钟频率为125M,数据位宽为16位,FPGA接收时,需要进行输入延时(input delay)约束,将LVDS时钟和数据的相位关系告知FPGA,从而让FPGA能够正确接收,如果约束不正确,则会出现接收错误的情况。

还有一个常用场景,就是网络芯片的RGMII接口。RGMII接口用于网络芯片和FPGA之间的网络数据传输,网络芯片往FPGA发数据,即FPGA接收数据时,就需要设置输入延时(input delay)约束。RGMII接口务必要做时序约束,否则会出现偶发性的数据接收错误的情况,笔者在做“弱小信号采集系统项目”时,就在这里吃过亏。

开始正文,首先讨论并明确输入延时(input delay)的概念。

第1节 输入延时概念

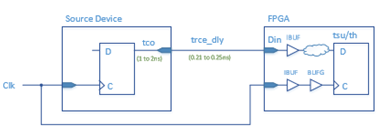

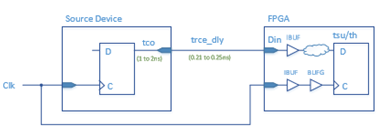

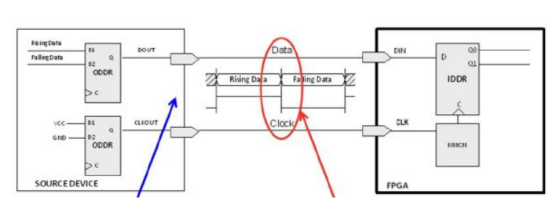

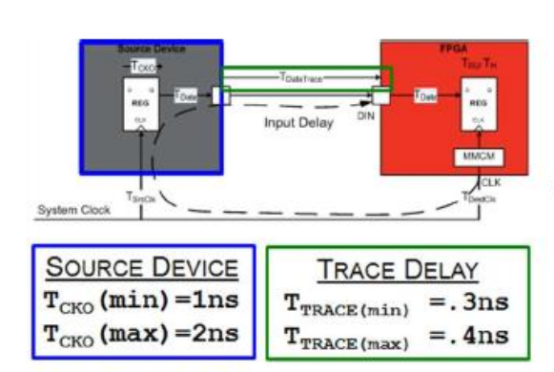

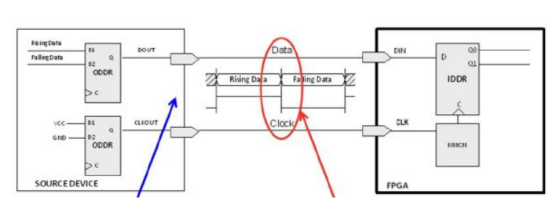

上图是一个典型的输入延时的模型,该模型由一个上游器件source device以及一个FPGA组成。上游器件将数据传送给FPGA,FPGA接收数据。从FPGA角度来看,输入接口由时钟接口和数据接口组成,上图右边FPGA的输入管脚,上面即是数据接口,下面是时钟接口。

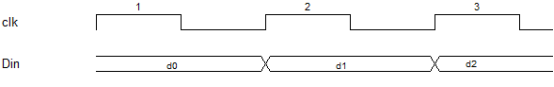

Din是由时钟clk产生的,理想情况下,Din的变化时刻一定是时钟的上升沿,即变化点和时钟上升沿对齐,如上图所示。

但在传输过程中,由于时钟和数据会存在延时差异,从而到达FPGA管脚是处于不同的时刻,数据和时钟之间会存在相位差,如下图所示。

上图描述了连续3个时钟下,数据接口din和时钟clk的相位差,第1个时钟相差了1ns,第2个时钟差了1.8ns,第3个时钟相差了1.3ns。相位差的变化有可能是延时原因,也有可能是上游器件的原因,总之,这些相位差数据是变化的,但它的变化应该在一个确定的范围,即肯定是存在一个最小值,同时存在一个最大值,相位差在这两个范围内变动。

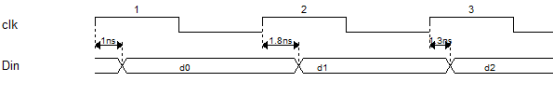

将其变化范围汇总起来,制作成如下的一张图。

上图中的灰色区域,就是相位差的变化范围。

现在可以给出输入延时(input delay)的定义:数据相对于时钟的延时,即数据时间-时钟上升沿时间。

a.注意是数据时间-时钟上升沿时间,这意味着输入延时可正可负。当延时在时钟右边时,输入延时是正的,当延时变化点在时钟上升沿左边时,输入延时是负的。

b.输入延时通常是一个变化范围,其有两个参数,最小延时min和最大延时max。最小延时即上图中灰色区域最左边点,最大延时是灰色区域最右边点。

c.输入的实际延时一定在最小和最大之间。约束时,需要设置好最小min和最大max的值。

d.上图中的clk和din是指FPGA管脚的,非上游器件管脚的。

e.牢记输入延时的概念定义,后面场景无论如何变化,万变不离其宗,都是按这个定义约束的。

第2节 约束语句

设置输入延时的约束语句,其语法非常简单,如下

set_input_delay -clock

是想要设定input约束的端口名,可以是一个或数个port。

-clock之后的clock_name,是时钟域的名字。

注意,这个clock_name是设置约束约束时定义的时钟域的名字,而非“时钟”名。

可以是一个真实存在的时钟

也可以是预先定义好的虚拟时钟

delay分两种

-max ,输入的最大延时,用于建立时间setup的分析,具体原因看后面部分。

-min ,输入的最小延时,用于保持时间hold的分析,具体原因看后面部分。

下面是具体的两个例子

set_input_delay -clock [get_clocks clk0] -min 0.5 [get_ports Din[*]]

set_input_delay -clock [get_clocks clk0] -max 1.5[get_ports Din]*]]

上面约束了信号Din相对于时钟域clk0,有最小延时0.5和最大延时1.5ns。

第3节 输入延时的目的

请继续看上面的输入延时的模式,注意看FPGA的内部结构。上游器件将数据发到FPGA的输入管脚,FPGA对其进行采样,采样一定会使用到D触发器,所以输入的时钟和数据,最终均会连到FPGA内部的D触发器上。

由前面几篇文章的讨论可知,D触发器是有建立时间和保持时间要求的。这个建立时间和保持时间,是这个D触发器的物理特性,是一定会有的,但这个数值是多少,工程师不知道,而综合工具如VIVADO、QUARTUS等会知道。

当Din和clk的延时不满足D触发器的建立时间和保持时间时,综合工具自动调整内部延时,例如增加一些BUF,或者增加线长等方式,使得信号最终到达D触发器时,能够满足建立时间和保持时间的要求。

所以综合工具需要知道输入的延时是多少,进而调整内部延时,最终满足D触发器的建立时间和保持时间要求,这就是设置输入延时的目的。

有几点需要注意的。

a.设置输入延时,只是客观描述外部信号,即数据和时钟和相位关系。只要知道综合工具这种相位关系,剩下的调整是综合工具自动完成的。

b.虽然综合工具可以调整内部延时,从而达到内部D触发器正确采样的目的,但这个延时是有一定范围的,存在无论怎么调都无法满足的情况。

第4节 获取参数的两种方法

由本文的约束语句一节,可以知道为了设置输入延时约束,需要知道两个参数:最大延时值max和最小延时值min。

那我们一般如何获取这两个参数呢?有两种方法,一种是查阅数据手册,另一种是通过示波器测量。

4.1 查阅数据手册

数据和时钟的相位偏差,通常来自于上流器件的寄存器延时和走线延时。

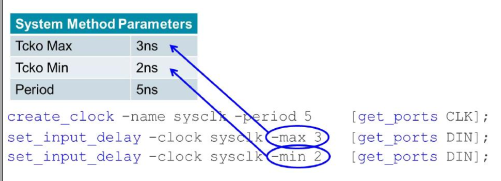

一个正规的器件,其数据手册会清楚地标明输出数据和时钟的延时范围,通常是寄存器延时TCKO等,大家可以查找一下。

至于走线延时,通常可以通过线长度,计算得到延时值。

所以第一种方法,就是查阅数据手册,获取时序参数,具体如何使用,可以看后面内容。

4.2 示波器测量

第二种方法是示波器测量的方法。

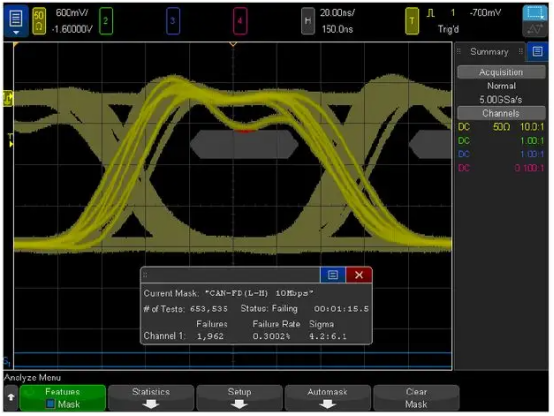

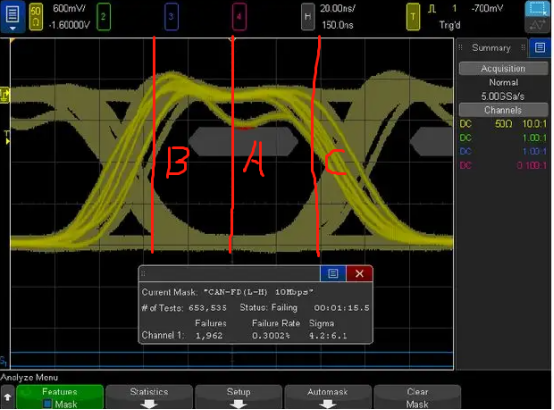

方便的话,使用示波器接到FPGA的输入的时钟和数据管脚,调整示波器处于眼图模式,就可以得到眼图,其样式大致如下。

上图是按照时钟基准来获取到的眼图,从上图就可以得到数据相对于时钟的延时信号,从而得到max和min值。

知道了上面两种方法后,还要结合应用场景,才能正确地设置时序参数。

第5节 应用场景概念

5.1 系统同步和源同步

数据接口的同步方式,分成系统同步和源同步。

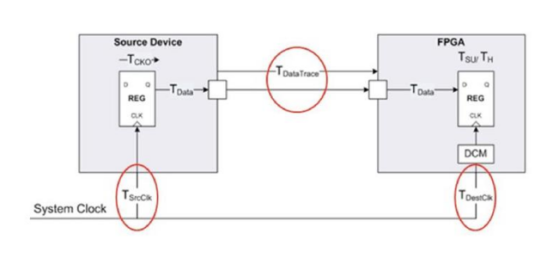

系统同步是指板上有一个时钟源,该时钟源将时钟送给各个器件,并且保证送给各个器件 的相位是相同的。如上图中,时钟system_clock送给了source device和FPGA,并且两者时钟TsrcClk和TdstClk相位是一样的,上游器件只发数据给FPGA即可。

系统同步要求时钟信号在系统级上同源,板级走线的延时也要对齐,要求很高,也比较难做。

源同步如上图,FPGA的时钟来自于上游器件 ,即上游器件将数据送给FPGA的同时,送一个随路时钟给FPGA,FPGA利用这个随路时钟来采样数据。源同步方式,没有时钟相位同步的要求,所以相比系统同步简单很多,应用也更加广泛。

5.2 SDR和DDR

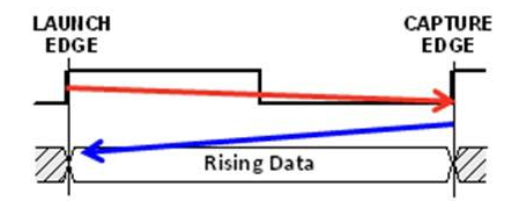

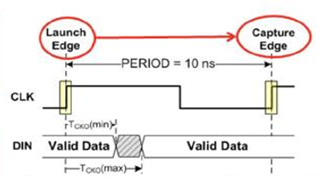

SDR是指数据只在时钟上升沿有效,当前时钟上升沿产生数据,在下一个时钟上升沿对这个数据进行采样的方式,上图就是SDR的示例。

DDR是指数据在时钟上升沿和下降沿都有效的一种传输方式。时钟上升沿产生的数据,在下一个时钟下降沿被采样;时钟下降沿产生的数据,在下一个时钟上升沿被采样。

由引可见,同样时钟频率下,DDR的速率是SDR的两倍,速率更高,要求自然也更高。

系统同步由于要求时钟信号在系统级上同源,板级走线的延时也要对齐,无法达到更高速的设计要求,所以大部分情况也仅仅应用SDR方式,本文针对系统 同步,只讨论SDR的方式。

源同步接口最大的优点就是大大提升了总线的速度,可以是SDR方式,也可以是DDR方式,本文针对源同步,将讨论

SDR和DDR两种方式。

5.3 中心对齐和边沿对齐

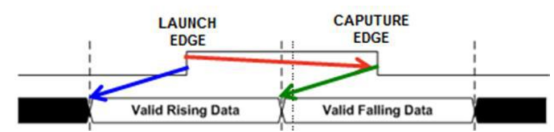

在DDR的传输方式中,我们又可以分成中心对齐和边沿对齐两种方式。

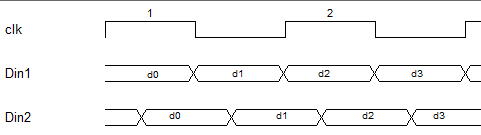

上面是FPGA收到的一个理想的传输波形图。Din1的变化点与时钟clk的边沿点对齐,这种传输方式就是边沿对齐。Din2的变化点则是在clk的低电平或者高电平中间,这种传输方式就是中心对齐。

上图是一个理想的波形,是假设Din1和Din2 零延时的情况,但实质上这是不可能的。在实际中,必会有延时,而且必定会有抖动,这个抖动围绕着数据变化点可能向左偏,也可能向右偏。由此,边沿对齐的实质波形如下图(在时钟边沿左右抖动,中间稳定)。

同理,中心对齐的实质波形将如下图所示(时钟边沿处稳定,中间抖动)。

第6节 各种场景下的约束方法

经过前面的铺垫和讨论,现在正式讨论各个应用场景下,输入延时的约束方法。

6.1 系统同步

系统同步的特点是时钟到各个器件的延时是一样的,这意味着设置输入延时时,不需要考虑时钟的延时,可以认为时钟延时是0,我们只需要考虑数据延时。

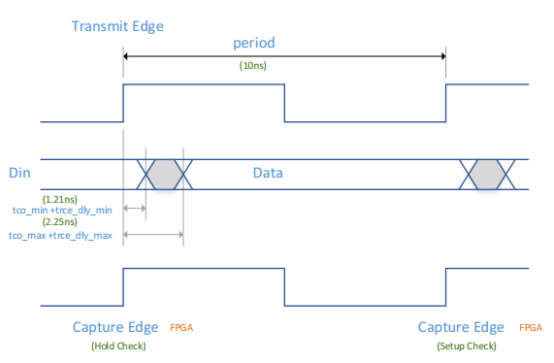

数据延时为两种,一种是上游器件在时钟控制下将数据输出到上游器件管脚的延时;另一种是数据从上游器件管脚,到FPGA管脚的延时。

查阅数据手册

假设通过查阅数据手册,得到TCKO最小是1ns,最大是2ns;通过计算布线长度,得到线延时最小是0.3ns,最大是0.4ns。由此可计算得到,输入最小延时:最小的TCKO+最小的线延时,即1.3ns;输入最大延时:最大的TCKO+最大的线延时,即2.4ns。所以可以有如下约束语句。

set_input_delay -clock sysclk -min 1.3 [get_ports Din]

set_input_delay -clock sysclk -max 2.4 [get_ports Din]

示波器测量

如果您找不到数据手册,或者电路板做得不标准,也可以使用示波器测量方法得到参数。假设眼图如下:

上图中,中间的A处是时钟上升沿时刻,B处是眼图闭合的左侧,C处是眼图闭合的右侧。从示波器中,可以得到B到A的距离,以及C到A的距离。而这两个距离,则正对应输入延时的最小值和最大值。如下图,图中的灰色区域,就是上图中的B到C的区域。

如前面所述,系统同步要求较高,大部分都是SDR情形,所以不在此讨论DDR的情节。

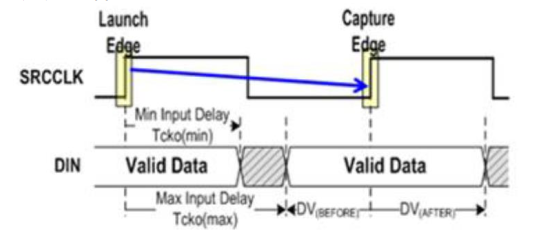

6.2 源同步SDR

源同步SDR的约束方法,与系统同步非常相似。

源同步是上游器件同时传输了时钟和数据,如果布线做得标准的话,即线等长的话,可以认为数据延时和时钟延时是一致的,也就是说我们可以不考虑线延时的情况。

所以通过数据手册,查询 到TCKO延时,就可以设置最大最小值了。

通过示波器测量,也可以获取到参数,下图就是眼图。

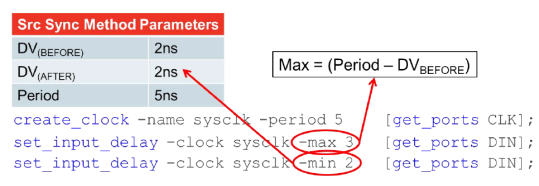

上图中,A是时钟上升沿处,B是眼图的左侧,定义为DV(befre),C处是眼图的右侧,定义为DV(altera),这两值都可以测量到。

上图是对应的波形图。

如何通过DV(befre)和DV(altera),获取到最小延时和最大延时呢?

认真观察,可以知道,最小延时就是DV(after);而最大延时则要计算一下,时钟周期-DV(before)。

下面就是一个配置的例子。

6.3 源同步-DDR

讨论完成源同步的SDR,接下来讨论源同步的DDR情形。源同步的DDR是时钟上升沿和下降沿都会采数据的情况,可以进一步划分成中心对齐和边沿对齐情形。

6.3.1 DDR中心对齐

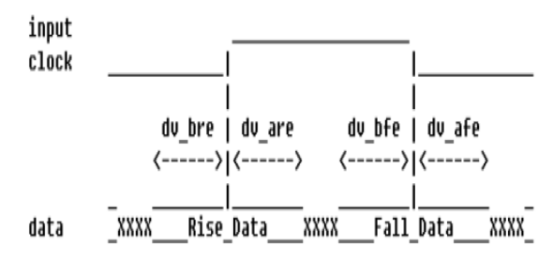

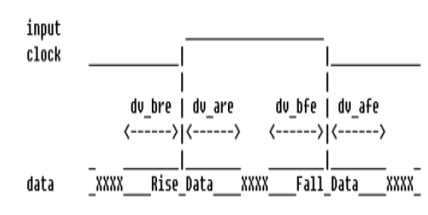

上图是DDR中心对齐的波形图,其中有4个参数可以通过示波器得到,分别是上升沿前dv_bre、上升沿后dv_are、下降沿前dv_bfe和下降沿后dv_afe。

注意,上图中,Fall_Data是由时钟上升沿产生,在时钟下降沿采样的;Rise_Data是由时钟下降沿产生,时钟上升沿采样的。

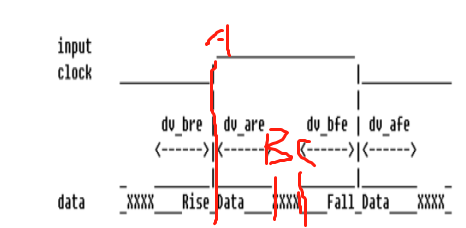

根据输入延时的定义,上升沿的输入最小延时是上图中的B到A的时间;输入最大延时是上图中的C到A的时间。因此,可知上升沿输入最小延时等于:dv_are;上升沿输大最小延时等于:半个时钟周期-dv_bfe。

下降沿的情况看上图。根据定义,下降沿的输入最小延时是B到A的时间;下降沿输入最大延时是C到A的时间。注意,根据周期性,上图中的C和D是相同的点。

可此可知,下降沿的输入最小延时是dv_afe;下降沿输入最大延时是:半个时钟周期-dv_bre。

现在举例说明,假设

时钟的频率为:100M,即周期为10ns;

数据data的dv_bre:0.4ns

数据data的dv_are:0.6ns

数据data的dv_bfe:0.7ns

数据data的dv_afe:0.2ns

则有,上升沿的输入最大延时:半个时钟周期-dv_bfe=4.3ns;上升沿的输入最小延时:dv_are=0.6ns;下降沿的输入最大延时:半个时钟周期-dv_bre=4.6ns;下降沿的输入最小延时:dv_afe=0.2ns;

可以列出出如的约束语句:

set_input_delay -clock clk -max 4.3 [get_ports data]

set_input_delay -clock clk -min 0.6 [get_ports data]

set_input_delay -clock clk -max 4.6 [get_ports data] -clock_fall -add_delay

set_input_delay -clock clk -min 0.2 [get_ports data] -clock_fall -add_delay

上面的语法中,使用-clock_fall表示下降沿;使用-add_delay表示与前面的约束一起生效。

6.3.2 DDR边沿对齐

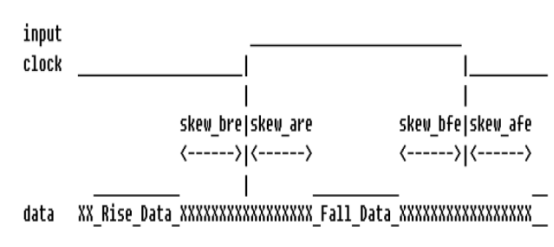

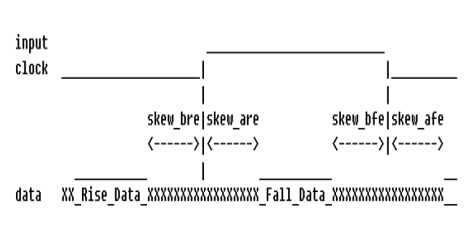

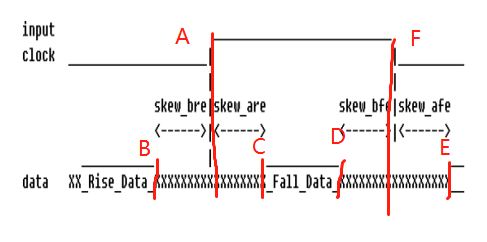

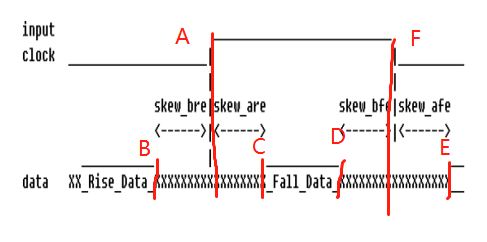

上图是DDR中心对齐的波形图,其中有4个参数可以通过示波器得到,分别是上升沿前skew_bre、上升沿后skew_are、下降沿前skew_bfe和下降沿后skew_afe。

注意,上图中,Fall_Data是由时钟上升沿产生,在时钟下降沿采样的;Rise_Data是由时钟下降沿产生,时钟上升沿采样的。

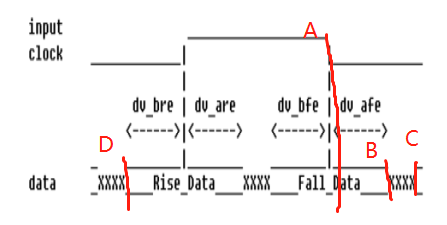

根据输入延时的定义,上升沿的输入最小延时是上图中的B到A的时间;输入最大延时是上图中的C到A的时间。有读者会疑问,为什么不是D和E呢?注意一下输入延时的定义,是“产生的数据”到“产生该数据的时钟沿”的距离。Fall_data是由A产生的,B到C区域,都是Fall_Data的变化区域,所以应该看的是B和C到A的距离 。这个时候,B在A的左边,说明该值是负数。

理解了上面的定义,可知上升沿输入最小延时等于:-skew_bre;上升沿输入最大延时等于:skew_are。

下降沿的情况看上图。根据定义,下降沿的输入最小延时是到D到F的时间;下降沿输入最大延时是E到F的时间。

可此可知,下降沿的输入最小延时是:-skew_bfe;下降沿输入最大延时是:skew_afe。

现在举例说明,假设

时钟的频率为:100M,即周期为10ns;

数据data的skew_bre:0.6ns

数据data的skew_are:0.4ns

数据data的skew_bfe:0.3ns

数据data的skew_afe:0.7ns

则有,上升沿的输入最大延时:skew_are=0.4ns;上升沿的输入最小延时:-skew_bre=-0.6ns;下降沿的输入最大延时:skew_afe=0.7ns;下降沿的输入最小延时:-skew_bfe=-0.3ns;

可以列出出如的约束语句:

set_input_delay -clock clk -max 0.4 [get_ports data]

set_input_delay -clock clk -min -0.6 [get_ports data]

set_input_delay -clock clk -max 0.7 [get_ports data] -clock_fall -add_delay

set_input_delay -clock clk -min -0.3 [get_ports data] -clock_fall -add_delay

上面的语法中,使用-clock_fall表示下降沿;使用-add_delay表示与前面的约束一起生效。

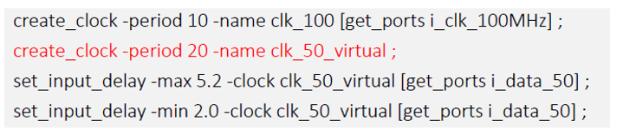

6.4 有数据无时钟

有一种特殊的输入信号,该信号是没有对应的时钟,是一种异步信号。例如最常见的UART串口信号,上位机发给FPGA只有一根线,双方按照约定的波特率进行通信。

FPGA使用内部的时钟去采这个异步信号,由于时钟和信号是异步的,因此无论怎么调整,都不能保证一定能够满足D触发器的建立时间和保持时间要求,这个时候要做异步信号同步化处理后,才能采集,否则会出现亚稳态现象,严重的会导致芯片崩溃。关于这部分内容,可以看时序约束的其他章节。

本文要探讨的是,对于这种异步信号,需不需要做输入延时的约束呢?

答案是需要的。对其进行时钟约束,其主要目的不是为了调整延时,而是为了告诉综合工具,这个信号是处于不同时钟域的,避免被系统认为属于某一时钟域,从而不产生警告,进而导致工程师遗漏了此问题的解决。

由于异步信号没有时钟,因此我们需要构造一个虚拟时钟,如以下语句,就是产生了一个50M的虚拟时钟clk_50_virtual,注意该语句并没有关联任何端口,所以是虚拟的;还要注意的是,定义为50M是随便的,您可以定义为其他任何频率。

create_clock -period 20 -name clk_50_virtual

当构造了虚拟时钟了,就可以设置异步信号的输入延时了,例如下面语句。注意5.2也是任意的。

set_input_delay -max 5.2 -clock clk_50_virtual [get_ports i_data]

第7节 总结与建议

最后,对本文进行简单的总结 。

a.本文先介绍 了输入延时的概念,然后分成不同的应用场景,根据这些应用场景不同,分别使用不同的约束方法。

b.输入延时约束关键的是获取约束参数,可分成查阅数据手册和示波器测量方法。

c.输入延时约束,只是客观反映外部信号的情况,千万不要理解成“要求系统,让输入延时多少ns”。即不是要求系统做什么,而是告诉系统输入信号的情况,而系统决定怎么做。

第8节 相关产品

本文提到的mdyFmcAd9653,是由明德扬科教研发的多通道,高分辨率和高采样率数模转换器的ADC系列子板,搭载两片ADC芯片,支持ADI、上海贝岭、北京时代民芯科技、中电24所等生产的芯片,完全PIN对PIN兼容;共支持8通道同步输入;共支持16位采样分辨率;支持最高125MSPS的采样率,适用于医疗电子、雷达、卫星导航等多种应用场合。

第9节 相关文章

1.《FPGA时序约束分享01_约束四大步骤》

2.《FPGA时序约束分享02_时钟约束》

3.《mdyFmcAd9653产品说明书》

-

FPGA I/O口时序约束讲解2023-08-14 3238

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4492

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 13015

-

时序约束的相关知识(二)2023-03-31 3530

-

FPGA的IO口时序约束分析2022-09-27 2532

-

FPGA的IO约束如何使用2022-09-06 3028

-

FPGA的时序input delay约束2022-07-25 3978

-

FPGA设计之时序约束2022-03-18 2353

-

Vivado中如何做set_input_delay约束2022-02-16 5250

-

FPGA时序约束分析余量2019-11-10 5410

-

FPGA中的时序约束设计2017-11-17 3091

-

华为内部经典FPGA时序资料---FPGA input delay约束的方法2017-03-04 4367

-

FPGA时序约束方法2015-12-14 1006

-

FPGA静态时序分析——IO口时序(Input Delay /output Delay)2012-04-25 3424

全部0条评论

快来发表一下你的评论吧 !