相变存储器和DC-DC转换器在汽车中的应用

描述

意法半导体将在VLSI 2021 技术和电路研讨会上发表三篇论文,两篇关于最大的汽车嵌入式相变存储器 (PCM),一篇关于由堆叠 LC 振荡器制成的新型片上 DC-DC 转换器,形状像八号。 因此,我们与一些作者坐下来,以更好地了解 VLSI 2021 选择他们的工作的原因以及他们的研究对行业的影响。事实上,这些贡献的独特之处在于它们将焦点放在了 FD-SOI 上。例如,只有 FD-SOI 基板才有可能发表关于新 PCM 的两篇论文。同样,ST 正在使用 FD-SOI 来缩小新的片上 DC-DC 转换器。虽然许多设备受益于 FinFET 技术,但这些发现表明 FD-SOI 在今天仍然发挥着重要作用。因此,让我们进一步探讨这些进展。

VLSI 2021 电路与技术:相变存储器

当今最大的嵌入式汽车级 PCM

Fabio Disegni 将展示容量为 16 MB 的新型 28 纳米嵌入式 PCM。由于汽车行业对可靠性的严格要求,为了冗余,每个逻辑位使用两个存储单元。因此,理论上可以通过每比特仅使用一个单元来进一步增加容量。无论如何,这项创新具有很高的象征意义,因为 ST 现在在嵌入式非易失性存储器中提供的单元尺寸仅为 0.019 µm 2。以前,工程师必须使用分立的内存模块才能获得这样的密度。此外,该论文详细介绍了 ST 已经合格并正在抽样的内存技术。简而言之,工程师可以期待商业设备在一年内使用这项技术。

Fabio 的论文将成为 VLSI 2021 电路的一部分,解释了工程师对新存储器的期望。ST在 10 ns 处测量了其随机访问时间,这与之前的模型相当。然而,鉴于容量非常优越,我们正在研究 166 Gbit/s 的理论读取吞吐量。该白皮书还介绍了一种用于更新的无线内存配置,可将容量增加到 24 MB。因此,设计人员可以根据他们的应用在冗余或增加容量之间切换。因此,开发人员可以获得更高密度的嵌入式相变存储器和更灵活的架构。

当今最先进的汽车级 PCM

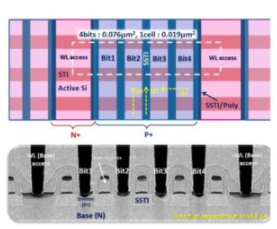

由 SSTI 分隔的四个位线

ST 的首席工程师 Olivier Weber 将在 VLSI 2021 技术大会上发表一篇论文,解释我们如何设法在 28 nm 创建新的 16 MB 嵌入式 PCM 模块。因此,他的演讲是一个补充说明,深入探讨了隔离负责加热硫族化合物的双极结晶体管 (BJT) 的创新。实际上,要写入 PCM 单元,系统会向 BJT 施加电压,BJT 会加热化合物以改变其状态。非晶态具有高电阻并表示逻辑 0。多晶相具有高导电性并表示逻辑 1。从一个状态移动到另一个状态只需向 BJT 发送适当的电压即可。因此,隔离它是最重要的。

在离散模块中,制造商通过称为超浅沟槽隔离 (SSTI) 的工艺隔离 BJT。Olivier 的论文是一项突破,因为它展示了 ST 如何在业界首次将这一过程应用于嵌入式 PCM。为了实现这一点,我们正在使用 FD-SOI 衬底的掩埋氧化物在位线之间创建隔离墙,从而防止位线到位线的泄漏。此外,ST 论文表明,可以使用相同的工艺将嵌入式单元从今天的 0.019 µm 2缩小到0.015 µm 2。因此,该技术具有高度可扩展性,并应进一步帮助相变存储器模块民主化。

VLSI 2021 技术:片上 DC-DC 转换器

ST 的射频模拟设计师 Mathieu Coustans 最终将在 VLSI 2021 Technology 上与苏黎世联邦理工学院合作发表另一篇论文,其中介绍了一种由垂直堆叠的变压器制成的 DC-DC 转换器,形状像数字 8。尽管转换器具有嵌入式特性,但它提供了令人感兴趣的效率和广泛的工作电压范围(从 0.8 V 到 3 V)。ST仍在努力在商业设备中实施该技术。因此,现在谈论大规模生产还为时过早。然而,当使用 FD-SOI 晶圆时,该论文在 22 nm 处显示出可喜的结果。事实上,该研究目前表明在 0.2 W/mm《sup》2《/sup》 时的峰值效率为 78.1%。

ST 和苏黎世联邦理工学院通过堆叠两个 D 类 LC 振荡器实现了这一性能水平,这些振荡器随后进行了电和磁耦合。该设计在不需要输出电容器的情况下大大降低了纹波,并且它的磁场更受控制(只有 58 dBm/µV,而传统环路变压器为 85 dBm/µV),从而降低了 EMI。原因是无源器件相互耦合,而不是电路的其余部分。该架构还可以实现更小的栅极电容,这部分解释了功率密度的增加。因此,即使转换器的片上尺寸可能稍大一些,它也有助于使用更小的封装。

审核编辑:郭婷

-

dc-dc转换器的作用是什么2024-06-10 13878

-

如何降低DC-DC转换器的纹波噪声2024-03-13 3412

-

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理2023-09-19 5283

-

DC-DC转换器实用设计考虑和应用2023-08-25 1930

-

DC-DC升压转换器的资料分享2022-07-26 2828

-

DC-DC转换器的相关资料分享2021-12-28 2676

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7110

-

电源内阻对DC-DC转换器效率的影响2021-11-16 2907

-

什么是DC-DC转换器?DC-DC转换器是如何命名的?2021-11-09 4646

-

DC-DC转换器原理2021-09-15 3252

-

什么是DC-DC转换器2021-07-30 1854

-

非隔离式的DC-DC转换器解析2020-12-09 5492

-

DC-DC转换器2010-03-09 4011

-

DC-DC转换器是什么及其参数2009-11-14 20812

全部0条评论

快来发表一下你的评论吧 !