关于EUV光刻机的缺货问题

描述

似乎有不少分析师最近提出,今年下半年缺芯问题就会得到缓解——这一结论的观察角度未知。但从半导体制造材料和设备的角度来看,无论如何都很难得出这样的结论。。.

细致到可以深究成熟工艺的光掩模(photomask)短缺问题——据说也是近期才发现的,尤其是28nm及以上工艺的产能开始受到掩模短缺问题的影响。不过这并非本文要谈的重点,未来或许我们可以单独撰文探讨;而更迫在眉睫的乃是光刻机的短缺。

前不仅Intel才宣布了原本位于俄勒冈州波特兰(Portland)的一台EUV(极紫外光)光刻机,已经迁往爱尔兰Fab 34工厂。如果说光刻机够用的话,也不至如此了。这只是光刻机当前及未来很长一段时间内将要短缺的一个缩影,它给行业和不同企业带来的不确定性将是深远的。比如单说Intel要在2025年夺回尖端制造工艺王座,在EUV光刻机都无法满足其生产需求的情况下,根本就是无从谈起的。

不光是EUV光刻,前不久ASML刚刚发出警示信号今年只会有60%的DUV(深紫外光)光刻机订单得到满足。在致分析师与投资者的季报电话会议上,ASML首席执行官Peter Wennink表示:“尽管当前宏观经济环境存在不确定性,我们仍然相信市场的根本驱动力不变。我们持续看到覆盖全部市场范畴、前所未见的客户需求,从先进到成熟工艺节点。我们正开足最大马力,并预期到明年需求仍将超过供给。”

ASML计划今年发货55台EUV光刻设备(EUV scanner),以及大约240台DUV光刻机。目前其DUV光刻机未交付订单超过了500台,所以购买全新DUV光刻设备(包括用于成熟和尖端工艺节点的)的订单交付期(或者说间隔期)大约是2年。今年仅能满足60%的DUV订单需求。以全速输出能力运转,关键问题也就是产能极限了。

不过本文着重来谈谈EUV光刻机的缺货问题。

EUV光刻机需求侧现状

在《评估Intel超越台积电的可能性》一文里,我们已经大致提到过Intel很快就要面临EUV光刻机根本买不到的尴尬了——这对Intel接下来异常关键的3、4年来说简直就是灾难,因为其后续尖端制造工艺都需要EUV光刻机。

台积电和三星从7nm工艺节点就开始应用EUV光刻层了,并且在随后的工艺迭代中,逐步增加半导体制造过程中的EUV光刻层数。借助EUV光刻,所需制造工序数量更少,图案保真度更高,节省时间和良率成本。Intel则将在接下来的工艺节点(Intel 4)引入EUV光刻技术,相较其他两家更晚。在这个时间点也显得最为尴尬,起码另外两家已经应用EUV光刻2代以上了,EUV光刻机有储备。

更具体地说,台积电Fab 15的5、6、7期在跑7nm EUV光刻工艺。Fab 18的1、2、3期造5nm工艺;预计2024年5nm工艺要达到240k片晶圆/月的产能;亚利桑那州Fab 21的5nm产能要增加额外的20k片晶圆/月。Fab 18的4、5、6期做3nm扩产,预计在产能上还要比5nm更高。Fab 20的1、2、3、4期在规划2nm。

三星这边,其实除了逻辑晶圆7nm、5nm、3nm工艺需求EUV光刻,另外DRAM存储对EUV光刻的应用也会需求量增大。其1z节点就在行业内率先引入了EUV光刻,有1个EUV光刻层,而1 alpha节点预计提量会有5个EUV光刻层。目前其华城(Hwaseong)和平泽(Pyeongtaek)的Fab厂有EUV设备,平泽还预备大规模扩产,以及规划中的奥斯汀逻辑fab厂也将应用EUV光刻技术。

Intel当前有3个研发fab厂需求EUV光刻工具,1个生产fab厂可装配EUV光刻机——不过后者目前似乎还没有装上EUV工具。而且Intel当前还在扩建8个可应用EUV的生产fab厂。应该说,在3家尖端工艺逻辑晶圆厂方面,台积电的EUV工具数量是远超三星的;Intel则因为入局最晚,现在是最被动的。

另外既然三星作为DRAM供应商需求EUV光刻机,那么SK海力士、美光自然就不会例外。美光宣布1 delta与1 gamma节点要应用EUV光刻;SK海力士的1 alpha节点已经在基于EUV光刻做生产,大约5个光刻层,据说也给ASML下了比较大的订单;另外南亚科技似乎也有应用EUV的准备。

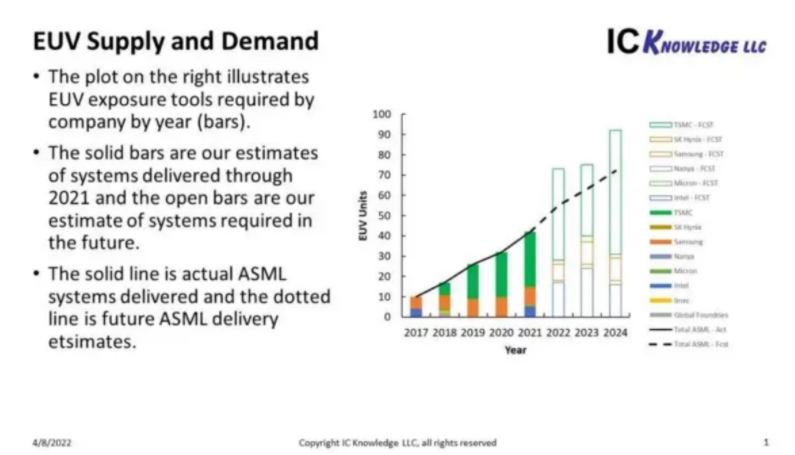

IC Knowledge基于以上动向给出了他们对于EUV光刻工具需求与供给侧的预期。上面这张图柱状条表示光刻设备需求量(空心的是预期),而折线表示ASML实际能够提供的量(虚线为预期)。从2021年的柱状条可见,台积电掌握着超过一半的光刻系统,三星次之,随后是Intel。IC Knowledge认为,2022-2024年市场对于EUV光刻工具的需求量会增多。则预计2022年会有18台设备短缺,2023年短缺12台,2024年短缺20台。

从这样的情势来看,至少未来3年内,依赖尖端制造工艺的芯片都将受制于EUV光刻设备的不足(通常是PC、手机以及更多HPC类应用)。作为仅剩的3家尖端制造工艺晶圆厂,Intel可能成为其中最艰难的。前不久就有消息说Intel CEO亦谈到了EUV光刻系统会成为未来建新厂的瓶颈。

比较有趣的是,Scotten Jones上个月发表评论说:“我认为EUV系统短缺产生的影响,还在于对于EUV光刻层的使用问题上。”“EUV对于横向的nanosheet而言更重要。”在3nm解读文章里,我们大致谈到过三星3nm GAAFET新型晶体管结构,它对EUV更为依赖。

而由于EUV光刻系统短缺,“我相信那些企业会被迫将EUV应用到影响更大的层上,并在其他部分层继续使用多重曝光。”这也是个挺有趣的解读思路,毕竟Intel 7工艺就没有使用EUV光刻,但晶体管密度也达到了台积电7nm的相似水平。在EUV光刻机短缺的大前提下,大概更多晶圆厂也不得不考虑减少芯片制造的EUV光刻层,并将某些原本可以用EUV光刻的层改用DUV做多重曝光了。

ASML这边的瓶颈,可能是“玻璃”

其实ASML今年Q1的财报并不能看出太多惊喜,不过订单量之多(70亿欧元)还是让人感受到了行业的供需不平衡现状的。投资者普遍比较关心的是ASML有没有可能提量来满足市场需求。Peter Wennick对此似乎并不是很有信心,倒是反复提及要等等看2025年的可能性,可能以其作为解决供应链问题的目标时间。2025年?Intel欲哭无泪啊。。.

Semiconductor Advisors LLC的分析师提到,ASML产能受限并不是因为芯片,也不是因为疫情或者俄乌冲突,问题是出在了ASML的供应商身上。造成瓶颈的关键供应商就是德国的蔡司(Zeiss)。所以这部分的小标题用了“玻璃”——以前我们就总在开玩笑说,磨玻璃的比玩沙子的高级。当然单纯用玻璃来代表蔡司是不对的,应该说是光刻机上的镜组和光学系统。

对ASML光刻机有了解的读者应该会很清楚,蔡司是当代尖端光刻工艺几乎唯一的光学镜组供应商。Semiconductor Advisors分析师表示ASML在这个部分是全部依赖于蔡司的,别无二选。玩摄影的同学对蔡司应当不会陌生(vivo之类的手机消费品上,现在也频繁出现蔡司的小蓝标了),这是德国的百年光学大厂(总有各种手工打磨镜片的传说)。不过蔡司并不是一家典型的商业企业,从组织属性来说赚钱也非第一要务。

据说一方面蔡司本身并没有足够的空间来增加产能,且基于其组织属性和百年传统,也无意于加快速度。不过Semiconductor Advisors的这个说法是否确切,可能还有待做进一步的考证。他们也并没有提供有关蔡司构成EUV光刻机输出瓶颈的论据。只不过在全球缺芯,ASML还缺光刻机的当下,蔡司的确可能成为产能瓶颈的重要一环。

只是越来越多导致缺芯的因素和瓶颈出现,或许会让更多的企业和政府反思半导体制造全球化的合理性。就像此前我们在俄乌冲突评论文章里提到的,现下的各种问题,从疫情到缺芯,从局部冲突到全球贸易争端,都将半导体行业推向一定程度的区域化(regionalization)-而非全球化。当半导体制造被全球仅有的1-2家公司卡住咽喉,对任何企业和政府来说都不会是什么好事;起码要有备选方案。

这是持续如此之久的缺芯潮,暴露出的最大问题,虽然在半导体尖端制造工艺这个人类精密加工技术的皇冠上——从技术层面来看——现阶段任何国家和地区的区域化可能都不大现实。

-

euv光刻机目前几纳米 中国5纳米光刻机突破了吗2022-07-10 55274

-

euv光刻机出现时间 ASML研发新一代EUV光刻机2022-07-07 5539

-

euv光刻机可以干什么 光刻工艺原理2022-07-06 8571

-

euv光刻机三大核心技术 哪些公司有euv光刻机2022-07-05 18843

-

EUV光刻机何以造出5nm芯片2021-12-07 12380

-

EUV光刻机何以造出5nm芯片?2021-12-01 14343

-

魂迁光刻,梦绕芯片,中芯国际终获ASML大型光刻机 精选资料分享2021-07-29 70632

-

EUV光刻机还能卖给中国吗?2020-10-19 11242

-

光刻机工艺的原理及设备2020-07-07 17564

-

关于EUV光刻机的分析介绍2019-09-03 15371

全部0条评论

快来发表一下你的评论吧 !