射频微波电路中的电源去耦旁路电容的使用

电子说

描述

前言

可能大伙儿看到“电源旁路电容为何要选择0.1uF 10uF?”这个标题,已经准备好50米大砍刀,撸起了袖子准备开喷啦

对于电容这个名词,相信咱们做电路的朋友(或者说学过模电,电路分析的童鞋们)再熟悉不过了,其或为隔直通交,或为匹配,或为旁路,或为传感器,或为DAC全二进制权重的电容阵列等等,基本上在有源电路与系统中99.99%的概率都会用到电容。

在微波射频网《3D动画+动图|详解电容工作原理》一文中,详细展开了关于电容的一些原理和基本用法,大家感兴趣可以前去进一步学习。本文主要集中讨论下射频微波电路中的电源去耦旁路电容的使用,根据笔者的理解去讨论回答下面两个问题:

(1)在射频电路中,为什么电源需要加旁路电容?

(2) 针对射频电源端的旁路电容我们又该如何选择呢,是不是直接用常见到的0.1uF,10uF的组合就可以了呢?

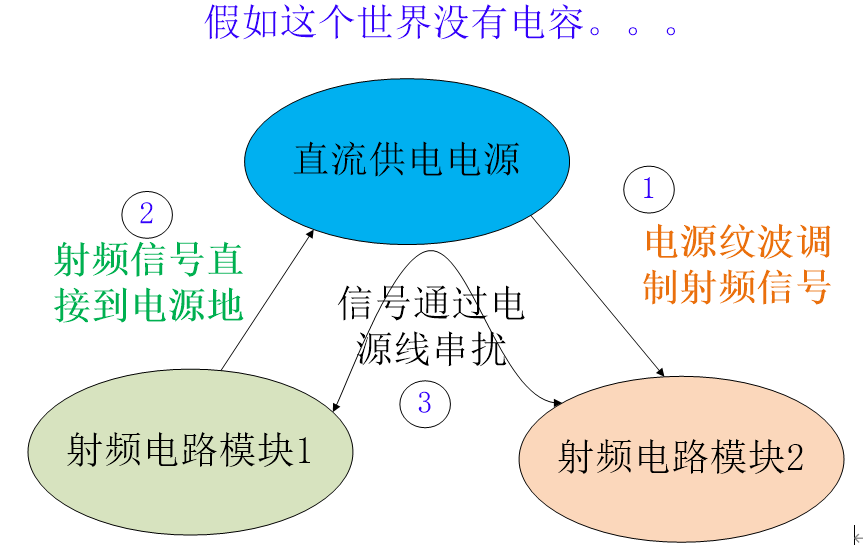

电源端加旁路电容的作用

我们知道,射频电路最终需要外部提供一个直流电源供电,这个直流电源与射频芯片内部的晶体管或者场效应管的基极(栅极)或者集电极(漏极)直接相连,一方面,由于电源具有一定的纹波,往往会导致射频信号受到调制,表现出一定的信号恶化,更有甚者导致电路不稳定;另一方面,电路里面的射频信号看到电源端的等效输入阻抗极小,这便导致射频信号直接传输到了电源的地端,使输出射频信号大打折扣;最后便是各个模块之间,通过电源线相互耦合,导致射频模块电路性能恶化。

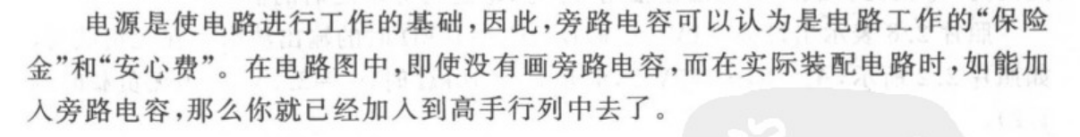

相信做过电路的童鞋们一定阅读过由日本铃木雅臣写的《晶体管电路设计(上)(下)》一书,该书可为学做实际模拟电路的宝典,在书中有这么一段话,我这里给摘抄下来。

因此在电源端加载旁路电容,不管是在模拟电路还是数字电路,都是十分必要的。

旁路电容的高频特性

既然在电源端加载旁路电容十分必要,那么我们设计的时候怎么加载,加载多少旁路电容合适呢???

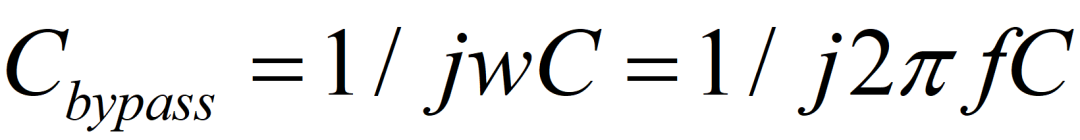

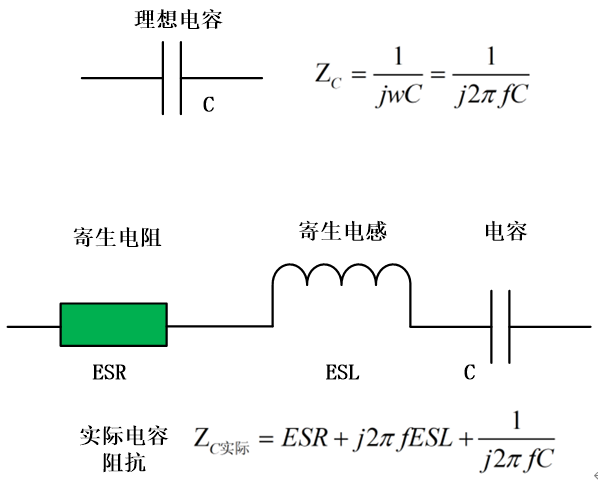

首先,我们知道电容的阻抗公式为:

那么在实际电路中,我们往往采用的多个旁路电容,这个时候一些小机灵就会问,岂不是就可以用一个来代替了?

乍一看上面的等效电路没毛病,至少从数学层面上来看似乎无懈可击,那么我们是不是就可以直接用一个电容值与两个并联电容值相同的电容来等效两个并联了呢?

从物理层面上来看,实际的电容是由寄生电阻,寄生电感,电容串联而成,如下图所示

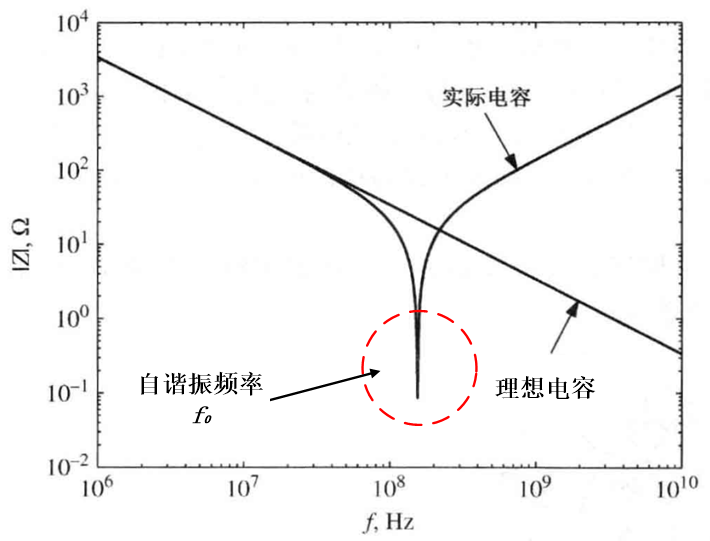

因此我们可以得到如下所示的电容的频率响应函数曲线,当电容工作在自谐振频率时,电容的阻抗为纯实部,低于自谐振频率时呈现容性,高于自谐振频率时,电容变成了电感变现为感性。

因此,如果我们如果只是在电源上只加载一个电容,势必只能在比较窄的带宽内可以实现良好的旁路滤波效果(在一定带宽内对射频信号呈低阻状态),正如《晶体管电路设计》一书中讲到,由于电容的寄生效应,为了得到宽带内旁路滤波效果,我们一般至少需要加两个容值有差异的电容并联到电源线。

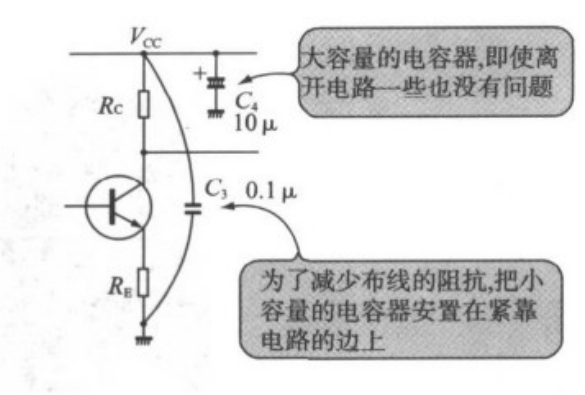

然而,同样在铃木雅臣的《晶体管电路设计》一书中并没有给出这两个容值一般差多少,书中倒是给出了一个实例,截图如下所示:

书中的电源旁路电容,选择了10uF和0.1uF,这样两个电容的容值比达到了100:1,这个时候,这样的示例在实际使用时往往又会存在一些问题,那到底是什么问题呢,我们下一小部分再来讨论。

电源旁路电容的选择

承接上一小节的问题,我们讨论到了,旁路电容的比值问题,如果两电容差值过大会惹来一些不必要的麻烦,那么到底是啥麻烦呢???”。

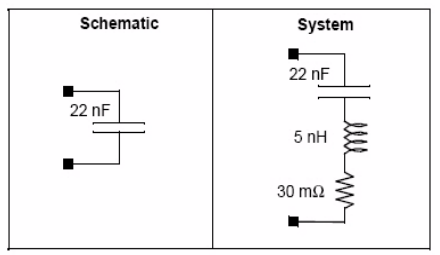

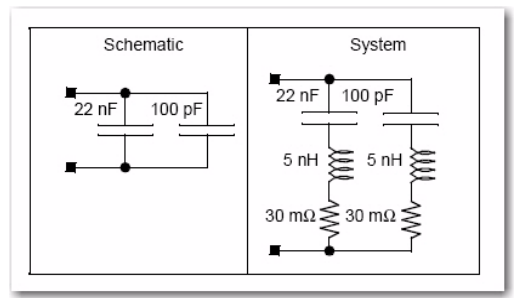

首先我们先看一个由英飞凌公司给出的一个数据手册《Infineon-AN1032_Using_Decoupling_Capacitors-ApplicationNotes-v05_00-EN》,英飞凌想必大家都熟悉吧,全球功率半导体市场的市占率约为19%,排名第一,2020年4月,英飞凌以90亿欧元成功收购美国同行赛普拉斯(Cypress),让其实力更是傲视群雄。那么其官网给出的关于旁路去耦电容的相关数据手册想必对我们还是有一定帮助的,在文中其提到了22nF电容和100pF的等效电路如下图所示:。

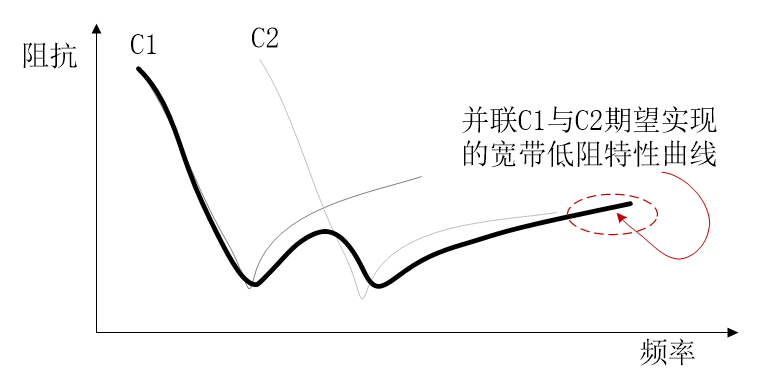

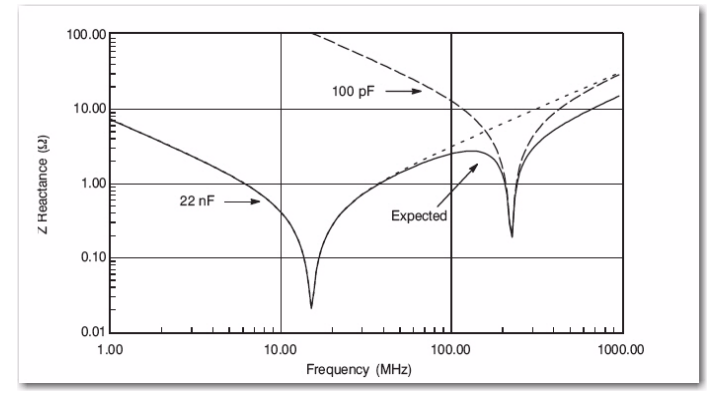

我们期望当22nF的电容和100pF的电容并联后得到如下实线所示的效果:

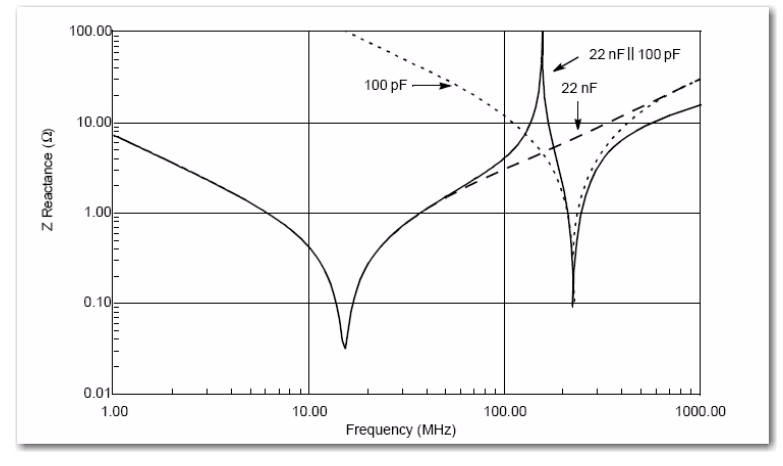

然而现实是当22nF的电容和100pF的电容并联后,得到了如下实线所示的效果:

所以残酷的现实告诉我们,原本并联两个电容是想得到一个阻抗相对较低的,宽带的平滑曲线,但是现实是打脸的,在并联完了22nF与100pF的电容后,在其原来的两个电容的阻抗曲线交叠处出现了一个阻值极大值谐振点,这也导致这样组合并不合适于电源滤除高频的一些信号到地。

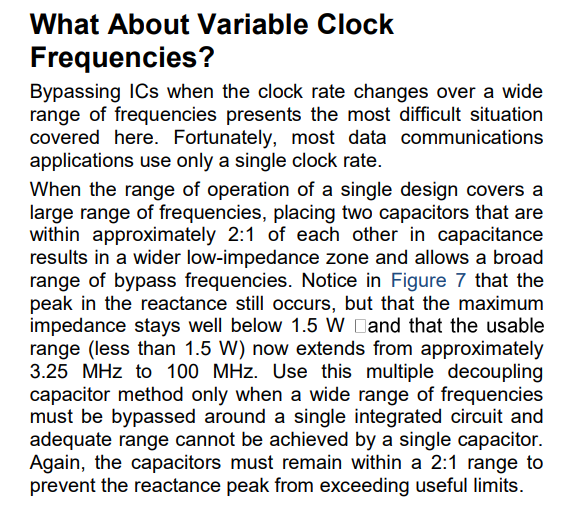

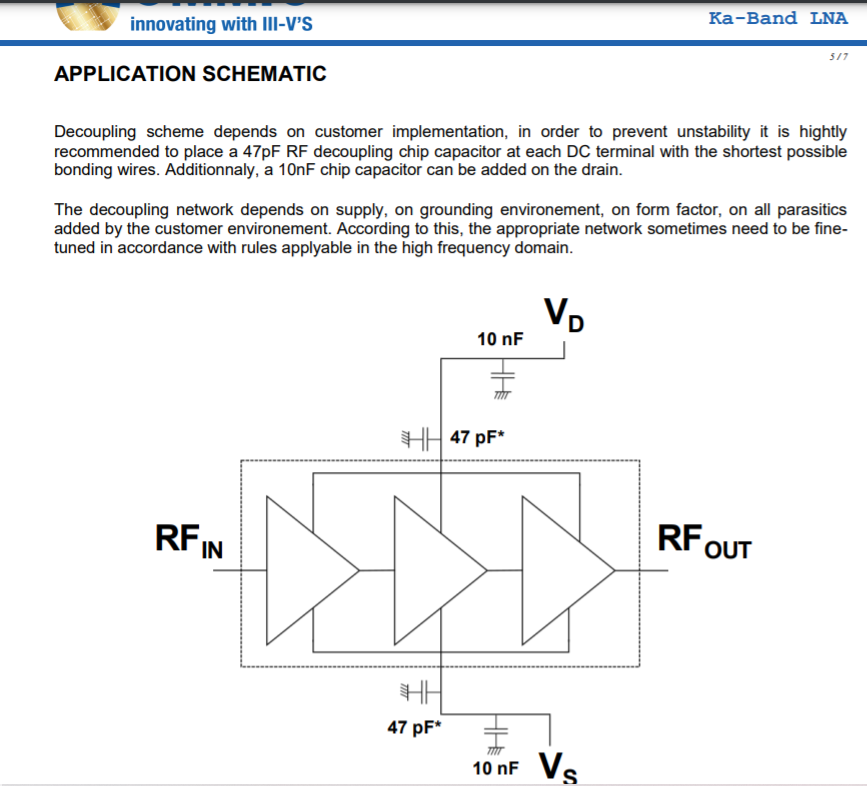

那么该如何选择旁路电容值呢?且看手册中的说明,如下

也就是说,我们最好采用的旁路电容值的间隔不要太远,最好是能够把容值之比控制在2:1之内。有图有真相,下面给出手册中将原来的20nF与100pF并联,改成20nF和10nF电容并联后的的阻抗-频率响应曲线图:

因此,后面如果要做好电路电源的滤波,旁路电容的选择要慎重又慎重,特别是看过上一篇射频问问RF测试专栏里面由J博客主写作的《PA的包络跟踪电源》一文,也提到了在功率放大器设计的时候,去耦和滤波一定要小心考虑。

好了,看到这里大伙心中是不是对电源旁路电容的使用原则有点点感觉了,

似乎明白的点在于:

1. 对电源加载旁路电容,由于寄生效应,我们常常采用两个以上的并联电容,用以提高其工作带宽;

2. 两个电容的电容比尽量控制在2:1。

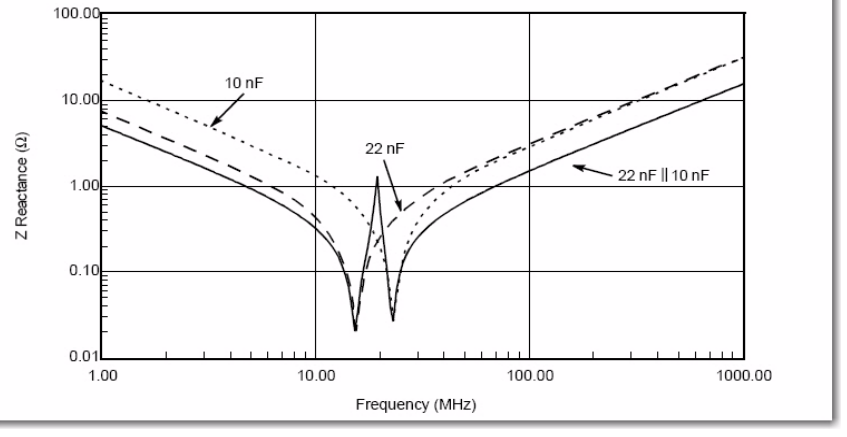

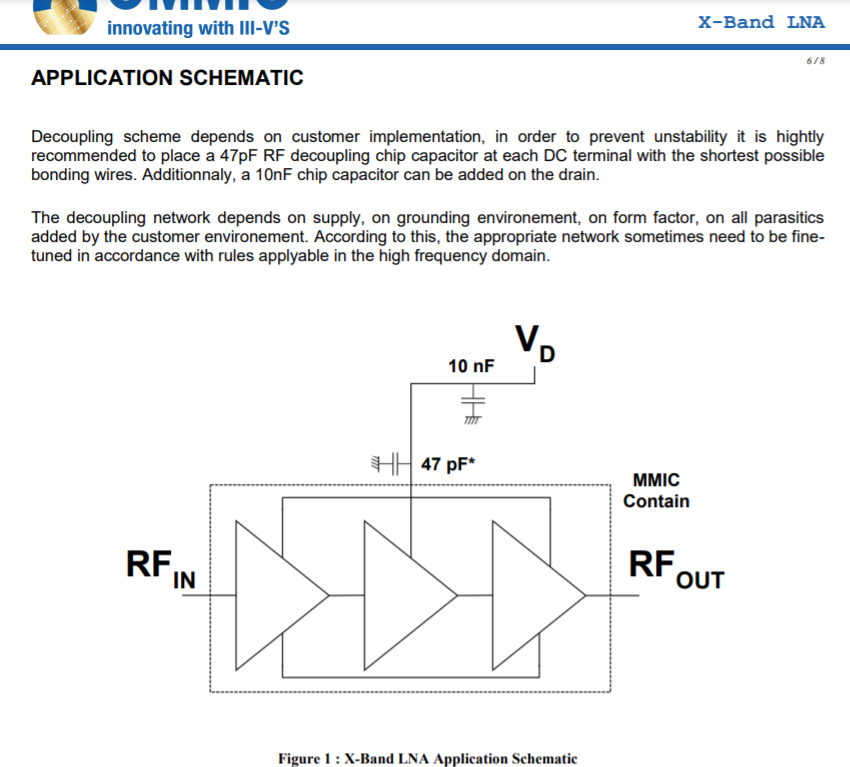

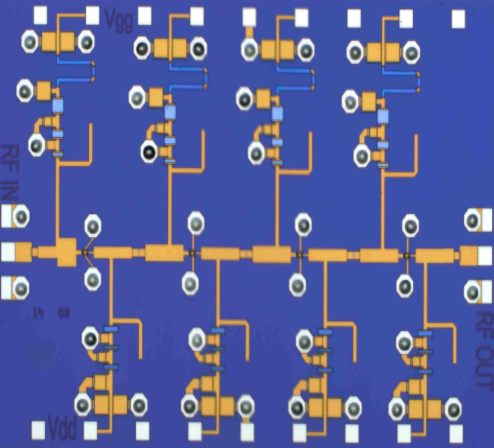

这个时候,我们随便打开一些射频微波芯片数据手册,我看一些微波毫米波数据手册上面给的芯片外围参考旁路电容并非我们所述的2:1的比例,比如这样的:

(某Ka波段LNA旁路电容选取值推荐)

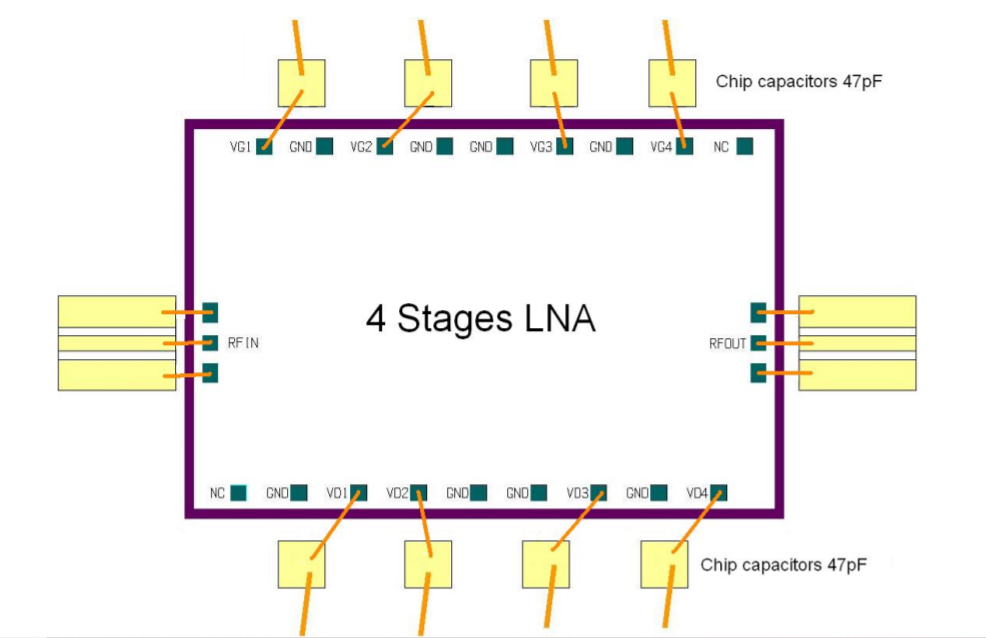

(某W波段LNA旁路电容选取值推荐)

这个时候手机旁边的你是不是又犯难了,这个旁路电容到底该咋选取啊!!!

好了,笔者这里给出一些自家敝帚般的观点,如果说得不对的地方,欢迎留言或者到群里来和大家一起交流探讨

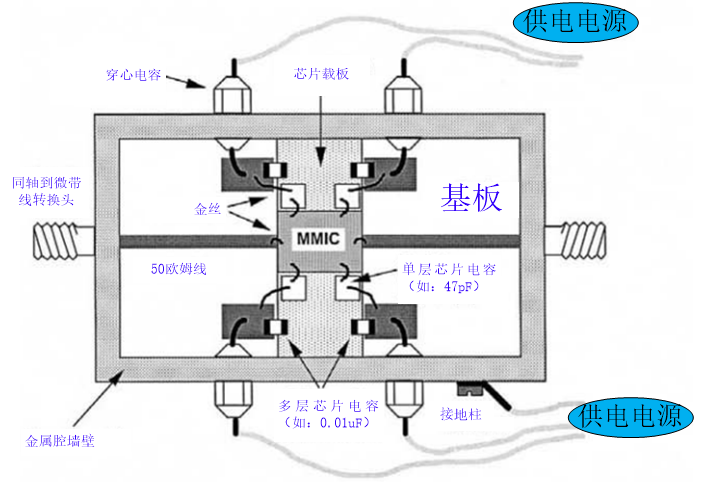

1. 针对板级射频电路的电源旁路电容的选择与布局

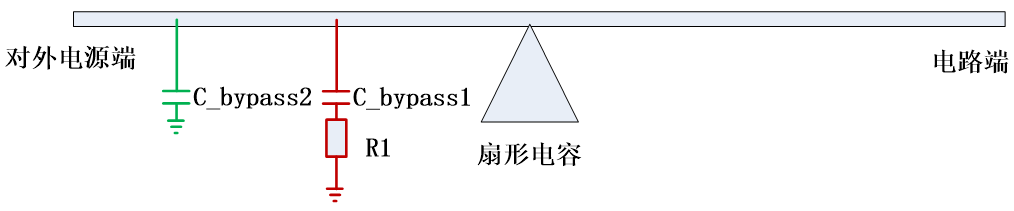

小电容尽量靠近芯片,大小电容的值最好是按照芯片数据手册的推荐值来,如下图示例所示:

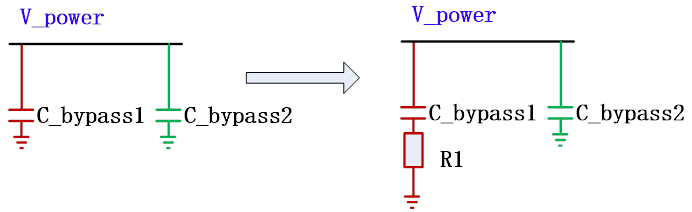

如果按照数据手册的旁路测试得到的电路在低频仍有振荡,不妨考虑在小电容C_baypass1上面串联一个小电阻R1,比如下图所示:

在上文所述的英飞凌的那个数据手册之所以会存在并联后的一个谐振尖峰的原因,主要是两个电容的响应曲线交叠处的各自的电阻都比较大。因此,如果我们在旁路电容中的某一个低寄生电阻的那个小电容上面串联一个小电阻,那么整个电源的旁路针对某一频率的等效电阻就会与最小的那个电阻值接近,当我们人为地设计一个小电阻后,便可以尽量规避掉谐振尖峰阻抗。

2.针对芯片级射频电路的电源旁路电容的选择与布局

芯片级的旁路电容,主要还是需要注意电容自谐振频率的位置,尽可能地把最小的电容的自谐振频率推到工作频率以外,同样如果仍旧无法解决低频谐振,可以尝试上文提到的方案,得到如下图所示的电源旁路电路结构:

当然,第一级扇形电容还可以用多层传输线包夹射频地的平板形式的电容代替,或许大伙还有更多想法和技巧,欢迎留言或者入群交流。

本期内容就到这里,希望没有浪费大家伙的时间,能有所获。

——END——《射频微波芯片设计》系列文章将持续更新,安排如下图所示:

审核编辑 :李倩

-

旁路电容和去耦电容在晶振电路中的作用2024-08-12 7618

-

旁路电容和去耦电容作用和区别介绍2024-03-01 5268

-

旁路电容和滤波电容,去耦电容分别怎么用?2024-02-03 3175

-

[转] 去耦电容和旁路电容的区别2022-11-04 14451

-

旁路电容和去耦电容的基础知识2022-10-25 2655

-

旁路电容、去耦电容及滤波电容的作用详解2021-06-22 6428

-

去耦电容和旁路电容相关资料分享2021-05-25 2245

-

旁路电容、去耦电容、滤波电容的作用分别是什么2021-03-17 3602

-

电容去耦和旁路的区别2021-01-11 2288

-

浅谈PCB中的去耦电容设计2021-01-07 3612

-

浅谈滤波电容、去耦电容、旁路电容之间区别2018-10-07 30441

-

PCB设计中的去耦电容和旁路电容2011-02-24 5696

-

去耦电容和旁路电容的区别2011-02-15 9121

全部0条评论

快来发表一下你的评论吧 !