FIFO中断通信逻辑介绍

描述

自中科昊芯推出专题讲解SCI串口通信以来,第一期主要讲解SCI串口FIFO通信原理,第二期主要讲解SCI串口自动波特率,本期主要讲解FIFO中断通信逻辑。

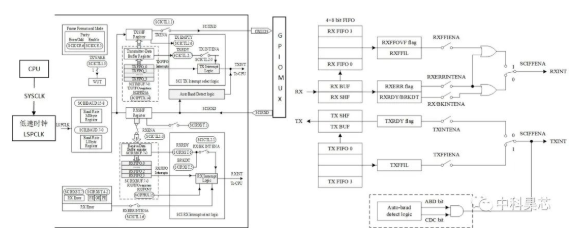

HX2000系列SCI模块原理与中断逻辑如下,中断逻辑为:当SCITXBUF数据被传输到TXSHF寄存器时,将通过SCICTL[TXRDY]产生一个发送中断,使能SCICTL[TXINTENA]打开发送中断信号,将通过PIE响应CPU执行,使得CPU可以连续写数据到SCITXBUF,使得SCI模块可以向PC端连续发送数据。当SCI接收一个完整帧,并将RXSHF寄存器中的数据传输到SCIRXBUF寄存器中,将通过SCIRXST[RXRDY]产生一个接收中断,使能SCICTL[RXBKINTENA]打开接收中断信号,将通过PIE响应CPU执行,使得CPU读取PC端发送的数据帧。

由此设计SCI串口FIFO中断通信实例:采用SCI与串口CH340,连续发送数据,PC端接收发送的数据;通过串口调试助手,向CPU发送任意一组数据,CPU接收发送的数据。

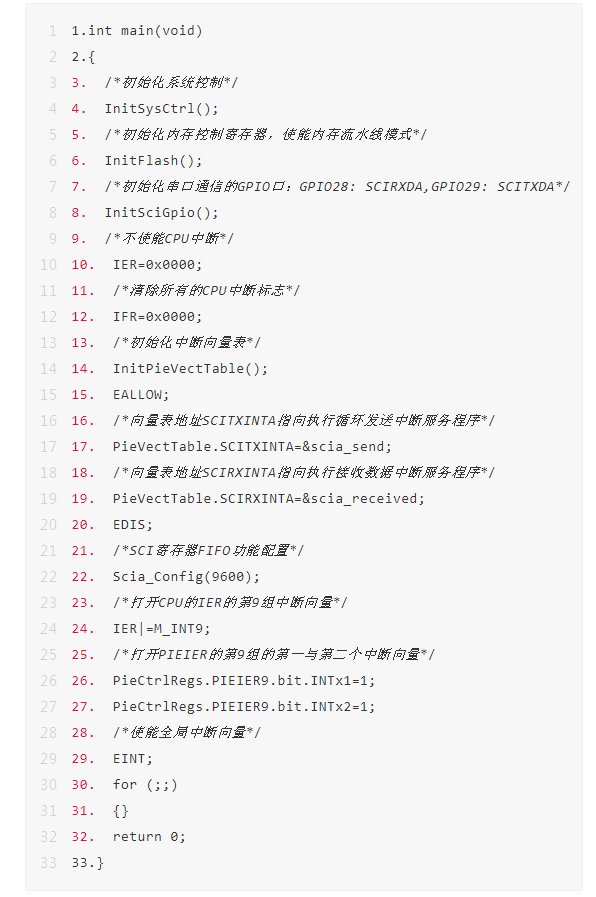

基于以上分析,在CDK上开发SCI串口FIFO中断通信输出程序,代码包括:SCI GPIO外设引脚配置,FIFO功能配置,发送与接收中断程序,主程序调用执行。主要代码如下:

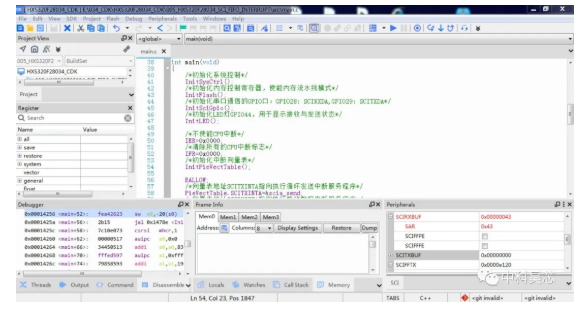

CDK上开发SCI串口FIFO中断通信程序,其编译结果为:

编译通过后,就可以开始调试了,DSP端连续发送数据的调试结果如下:

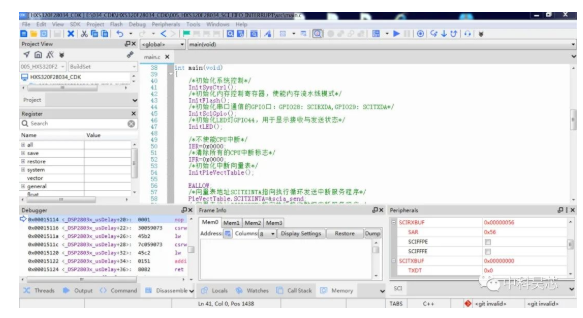

PC端发送数据的调试结果如下:

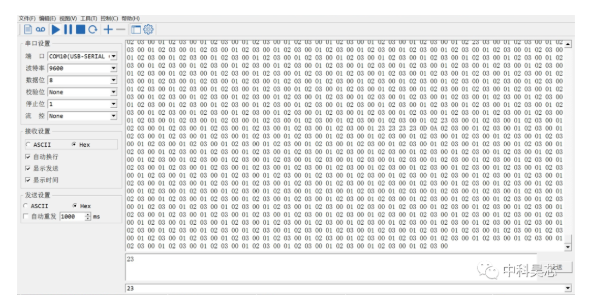

调试后,可通过串口调试助手查看发送与接收到的数据如下图:

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

同步FIFO和异步FIFO区别介绍2024-06-04 3848

-

如何使用硬件FIFO来减少接收中断次数2023-11-06 1443

-

Xilinx FIFO手册2022-08-28 530

-

CAN中断逻辑图这个"FIFO0发送中断"是否应该改为“FIFIO0接收中断”?2022-06-17 754

-

芯教程丨平头哥助力中科昊芯HX2000系列芯片专题SCI串口通信(三)FIFO中断通信2022-05-26 1828

-

SCI串口自动波特率介绍2022-04-26 4405

-

STM32使用FIFO实现USART串口发送中断2021-12-28 1012

-

【STM32+cubemx】0005 HAL库开发:uart串口中断和fifo环形队列2021-11-15 1138

-

如何使用带FIFO的串口来减少接收中断次数2021-08-16 8202

-

xilinx7系列FPGA新设计的IO专用FIFO解析2020-11-29 3939

-

RX中断逻辑是怎么样的?2020-06-14 1369

-

基于异步FIFO在FPGA与DSP通信中的运用2017-10-19 1002

-

微机原理--逻辑中断处理2016-12-12 746

全部0条评论

快来发表一下你的评论吧 !