使用Modelsim编译激励文件的详细流程

描述

前序

对于激励文件,我常用的是直接手写,最初学这个的时候,好像是用的Quartus里的那个Modelsim-Altera的工具去弄了下图形化编辑去制作约束,现在讲到这ModelSim了,也就再捡点来折腾下,还是有点学习价值,毕竟编辑的约束就真的很“直观”了。

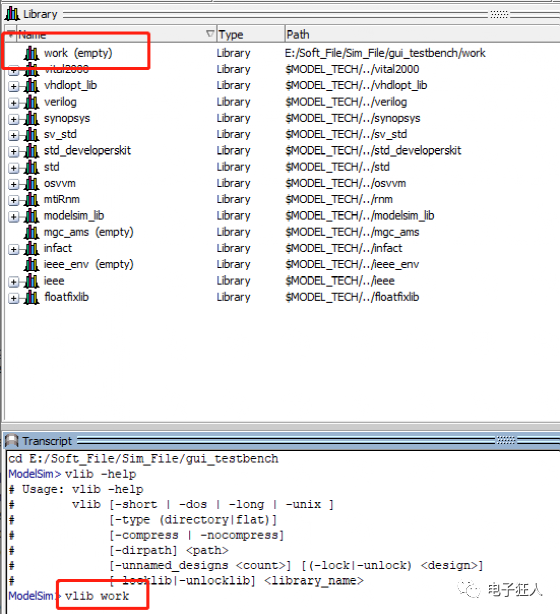

编译文件

其他的就不多回忆了,直接开正题吧,一如既往,把待用的文件准备好,这次就只需要一个counter.v的文件,然后把ModelSim的当前路径切换到你文件所放的路径,接着在脚本窗口敲:

vlib work

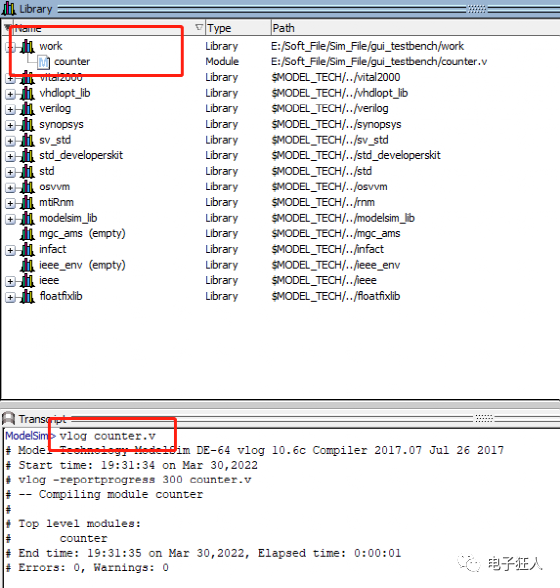

再把文件编译一下:

vlog counter.v

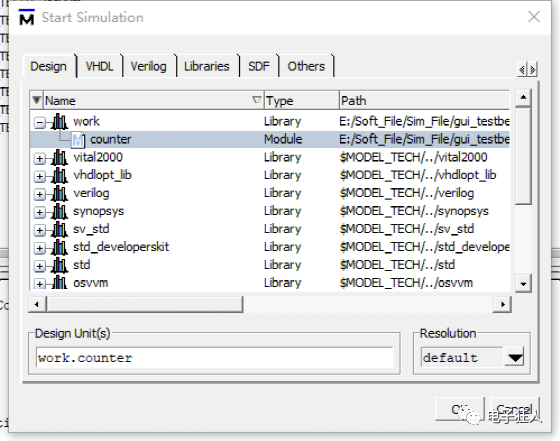

在菜单栏里 Simulate => Start Simulation,弹出来的窗口把文件选好准备进仿真界面;

产生激励信号

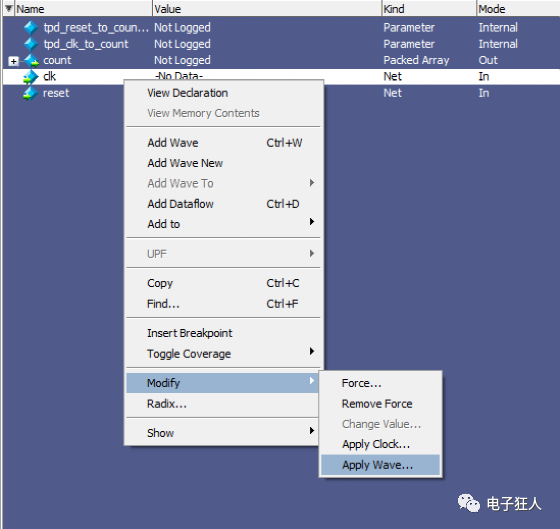

在仿真的界面,选中Objects的窗口里的clk,右键如下操作:

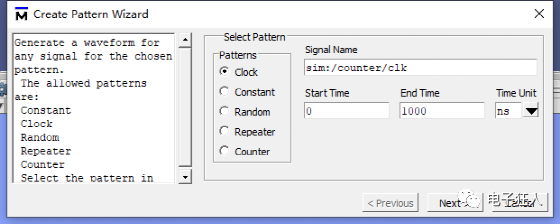

出来的界面,就是设置类型,然后就是开始和结束的时间,精度都是ns,根据自己情况改,我就默认Next下去

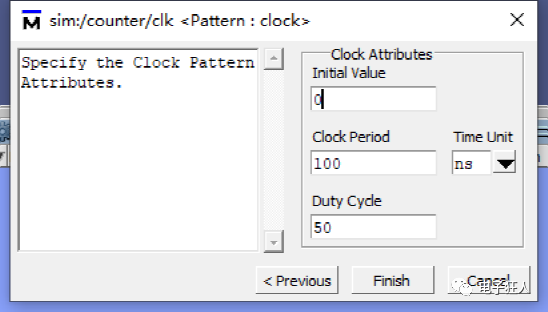

这个窗口就是让你配时钟参数,占空比、周期之类的,初始值写个0进去

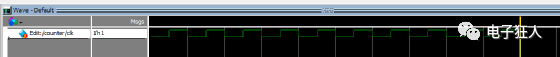

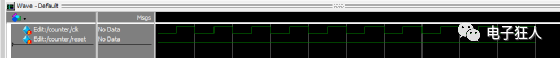

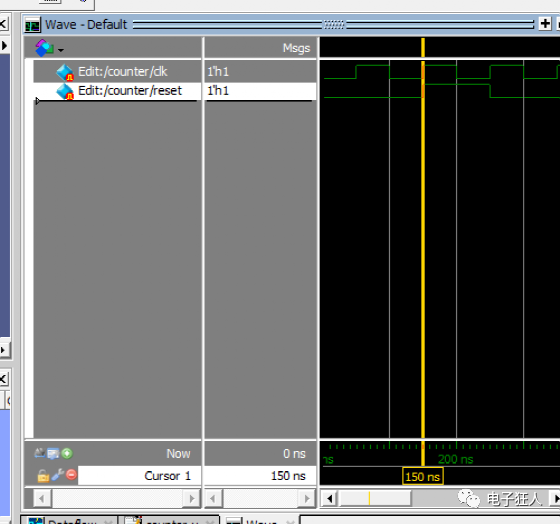

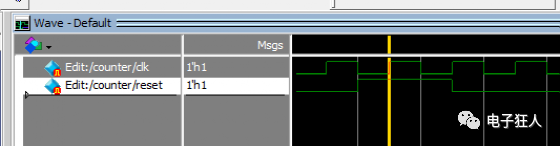

接着就在Wave的界面出现一个带“Edit”还有红色标记的clk信号

时钟有了,就再加个复位信号

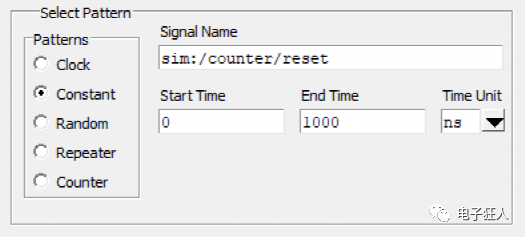

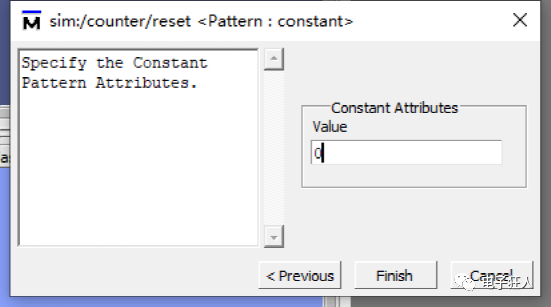

操作与上类似,类型就选个常数

把变量值写个0

结束后,就有复位信号出现了

因为这个文件的功能比较简单,所以有这两个信号就够用了,接着演示下怎么图形化的去编辑波形,从而得到自己想要的激励形式;

编辑激励信号

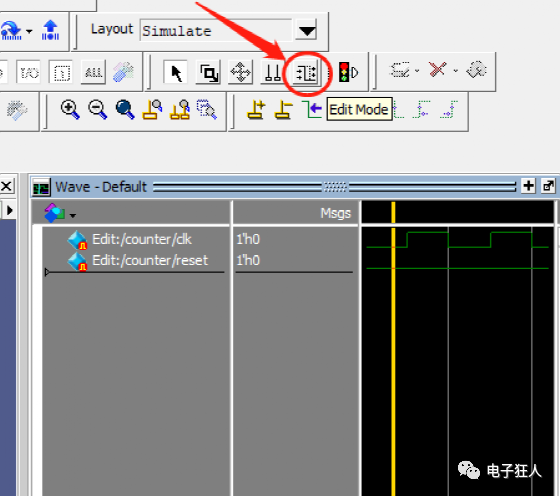

因为代码是使用的高电平复位,所以先让复位工作起来,再停止复位,就相当于在现在的0常量里头加一个高电平脉冲,先鼠标点下Wave的界面,然后工具栏里的这个Edit Mode的图标就会生效

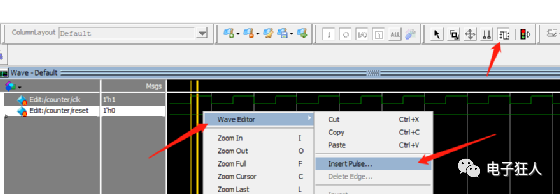

把模式切换到编辑模式,选中reset,右键后的Wave Editor就可以看到Inset Pulse的功能

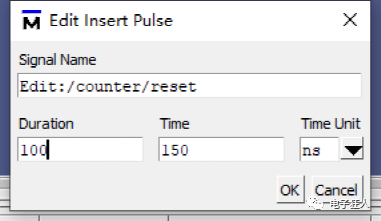

出现的设置项,就是要保持多长时间,已经开始插入脉冲的时刻;

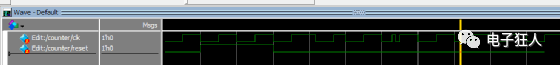

reset就发生对应的变化

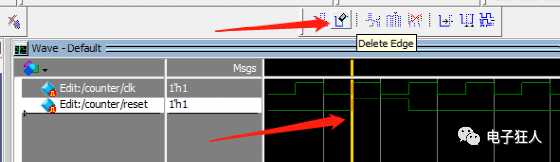

如果添加的不对,就可以选择好添加脉冲的边沿时刻,然后再工具栏找到“Delete Edge”的图标(右键Wave Editor里也是一样),点一下,出现的窗口是需要删除的边沿时刻,确定后就会把这个对应的时刻后边的整个边沿连续的部分,都删除(删除了记得再插回去哈,接着往下演)

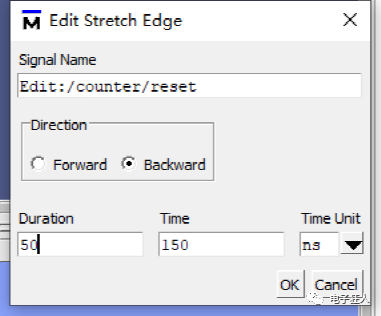

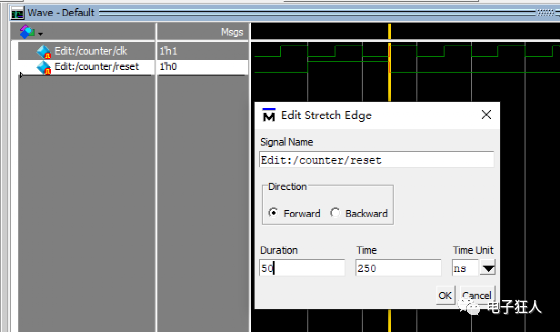

如果复位时间感觉不够,就再补个拉伸的操作,把边沿扩长,比如在150ns的时刻,从后向前补50ns(就相当于高电平在前面的50ns)

然后就可以看到效果了,在边沿拉升到了100ns处

如果要往后面补,就选后边沿,从前往后补

编辑上就是这样根据自己情况去插入或者删除多余的状态,然后再过一下,把时钟的信号随便打乱几拍(乱操作哈,别当成实际应用了.....)

约束就假装编辑好了,然后可以准备“逆”生成一个激励文件了~

激励文件生成

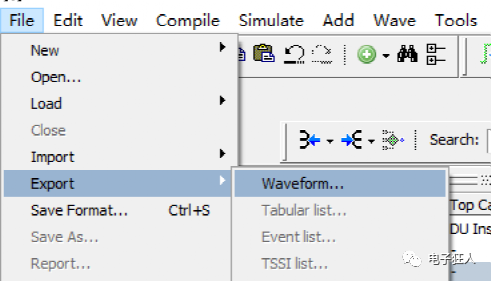

开始导出对应的文件

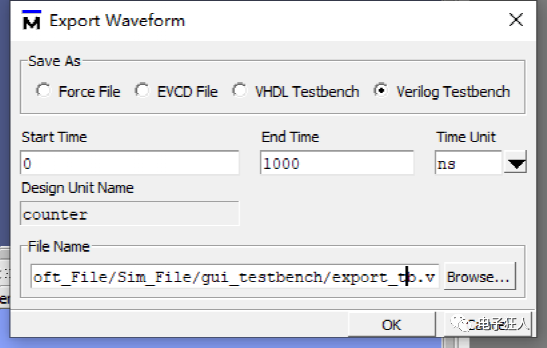

选择Verilog形式的激励文件(也搞个ECVD File),1000ns后结束激励,选好存储的路径,文件名也设置好就可以OK

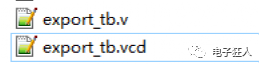

在对应的路径就能有这两个文件了

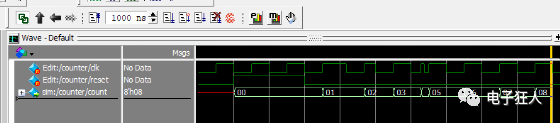

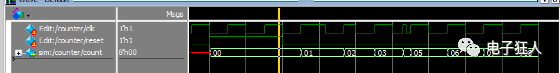

这时候再将Obejcets里的count变量添加到Wave窗口,并运行1000ns仿真,发现数据出来了~

退出仿真

Testbench测试

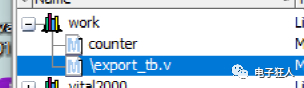

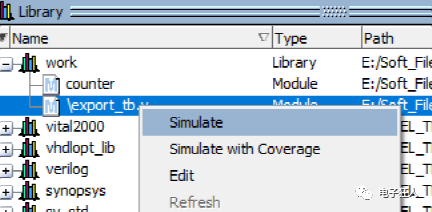

准备用刚刚导出的激励文件来进行仿真测试,先把它编译到工作库里

vlog export_tb.v

然后运行仿真

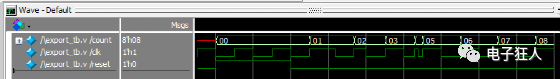

把信号添加到Wave里作观察,并运行1000ns的仿真

add wave *

run 1000ns

可以看到仿真按激励进行~

退出仿真

EVCD测试

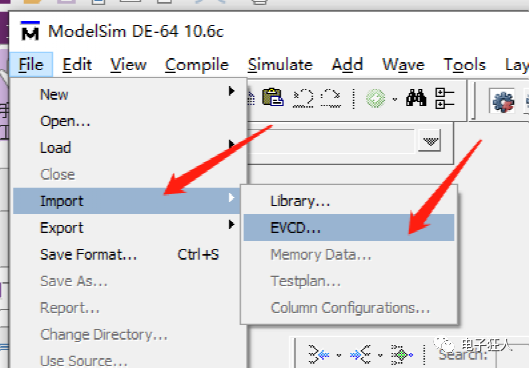

接着演示下VCD文件的使用,直接启动counter的仿真,然后先点下Wave界面,把这个EVCD的导入形式激活

再把EVCD导进来,编辑的信号就又出来了,再把count的变量也加到Wave里,并运行1000ns

run 1000ns

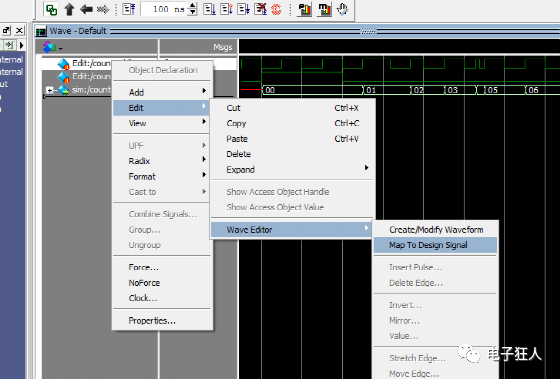

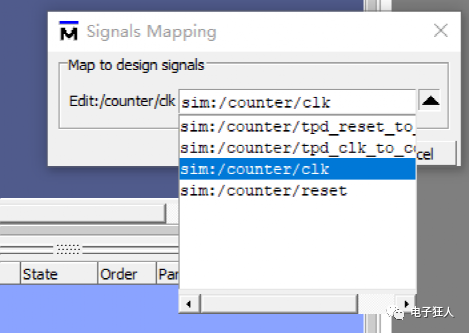

补个EVCD的使用,如果EVCD里的信号没有和对应的代码变量名对应起来,可以自己手动去把它进行映射,比如,clk

在窗口里选择要映射的信号,OK后就映射好了

结束

这种可视化编辑,然后再产生出激励文件的形式大概就这样了,还不会咋写激励文件的可以这样尝试折腾折腾,说不定就突然很有“灵感”了。

原文标题:Modelsim的仿真之路(激励文件“逆”生成)

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

-

ISE 关联 Modelsim 详细操作2024-03-22 1216

-

在 i.MX8M Plus EVK 上刷新和调试 Cortex-M7 固件详细流程是什么?2026-05-18 125

-

modelsim激励程序怎么编写2014-04-26 3926

-

STM32自定义USB设备开发详细流程讲解2019-08-03 7228

-

ModelSim文件下载入口2010-02-09 1619

-

多晶硅制备详细流程及图解2011-01-10 2451

-

Modelsim百问(一)2011-05-26 1092

-

modelsim仿真详细过程(功能仿真与时序仿真)2017-12-19 77351

-

仿真软件ModelSim及其应用,ModelSim的仿真流程2018-12-29 10812

-

三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料2019-07-09 2207

-

PE工具安装的详细流程详细说明2020-12-10 1296

-

FPGA设计的全部流程详细说明2021-01-29 1227

-

Modelsim注册文件2022-12-12 590

-

BOSHIDA DC电源模块检测稳定性能详细流程2023-06-30 1382

-

自动售货机MDB协议中文解析(七)MDB-RS232控制纸币器的详细流程和解析2024-09-09 2747

全部0条评论

快来发表一下你的评论吧 !