基于MAX+PLUSⅡ的十进制计数器的设计

编程实验

描述

O 引言

MAX+PLUSⅡ开发系统是易学易用的完全集成化的设计开发环境。目前已发行10.0版本。该软件与LATTICE公司的iSPEXPERT及 XILINX的FOUNDATION相比具有使用简单,操作灵活,支持的器件多,设计输入方法灵活多变等特点。常用的设计输入方法如下:

(1)图形设计输入:MAX+PLUSⅡ的图形设计输入较其他软件更容易使用,因为MAX+PLUSⅡ提供丰富的库单元供设计者调用,尤其是在 MAX+PLUSⅡ里提供的mf库几乎包含了所有的74系列的器件,在prim库里提供了数字电路中所有的分离器件。因此只要具有数字电路的知识,几乎不需要过多的学习就可以利用MAX+PLUSⅡ进行CPLD/FPGA的设计。

(2)文本编辑输入:MAX+PLUSⅡ的文本输入和编译系统支持AHDL语言、VHDL语言、VERILOG语言三种输入方式。

(3)波形输入方式:如果知道输入、输出波形,也可以采用波形输入方式。

(4)混合输入方式:MAX+PLUSⅡ设计开发环境,支持图形设计输入、文本编辑输入、波形编辑输入的混合编辑。

1 十进制计数器的设计

十进制计数电路结构如图1所示。主要由消抖电路、BCD码计数器和七段译码器构成,各部分电路介绍如下:

1.1 开关防颤动电路

按钮从最初按下到接触稳定要经过数毫秒的颤动,键松开也有同样问题,如图2所示。键入时间ta因人而异,一般开关 ta<100ms。设置开关防颤动电路目的:按键一次,输出一个脉冲。即将开关的实际输出作为开关防颤动电路的输入,而开关防颤动电路的输出为图2 所示的理想输出。

1.2 BCD码计数器

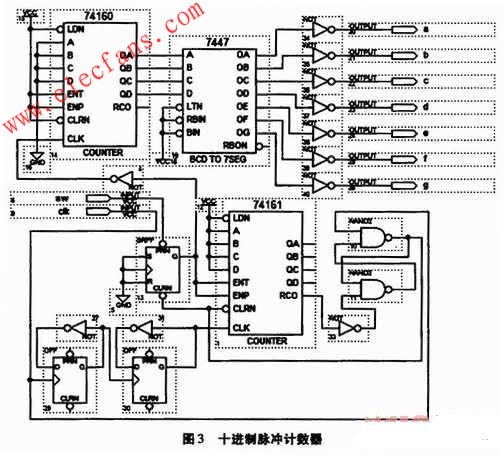

本设计采用的BCD码计数电路由74160构成,74160是十进制同步计数器(异步清除),在其功能表中,当LDN、ENT、ENP、CLRN四个输入端都接高电平时,对CLK输入脉冲上升沿进行计数,由QA-QD输出8421码。

1.3 七段译码器电路

本设计采用的七段译码器电路由7447和外部共阴极数码管构成,7447七段译码器将BCD8421码译成数码管所需的七段数显码。

综上所述,所设计的十进制计数器电路如图3所示。

2 十进制计数器的仿真

打开PC机界面MAX+plusⅡ软件,输入图3的电路图;选菜单File\Project\Set Project to Current File,然后选菜单MAX+plusⅡ\complier编辑当前图形文件;对图3进行仿真,仿真结果如图4所示。由图4知:所设计的电路(图3)符合十进制计数器的逻辑要求。

用Byte Blaster下载缆线联结PC机并口和实验箱J1(JTAG),打开实验箱电源开关。选择菜单项MAX+plusⅡ\Programmer,单击 Program按钮,即开始下载程序。打开实验箱电源开关,连续按K52键,数码管LED1将从0按顺序变到9,符合十进制计数器的逻辑要求。

3 结束语

MAX+PLUSⅡ是电子设计领域的一场革命,它的应用越来越广泛,MAX+PLUSⅡ在实验教学的应用,不仅是提高设计效率的需要,更重要的是培养适应创新、创业人才的需要,以适应电子工业的竞争与发展。

- 相关推荐

- 热点推荐

-

基于FPGA的十进制计数器2022-12-20 1045

-

十进制计数器的工作原理2022-10-31 30208

-

CD4017十进制计数器的应用实验2022-05-11 1273

-

74ls160十进制计数器2018-01-18 265437

-

十进制计数器/分频器2017-04-06 3965

-

二五十进制计数器2016-03-22 1706

-

DIY十进制计数器2013-12-03 3710

-

4位十进制可逆计数器电路2010-12-10 7811

-

十进制计数器,十进制计数器原理是什么?2010-03-08 25681

-

8421码同步十进制递增计数器2009-09-24 6883

-

100进制计数器2009-06-28 8531

-

基于MAX+plusⅡ开发平台的EDA设计方法2008-06-24 4132

-

十进制计数器工作原理2008-01-21 30760

-

十进制计数器2007-06-20 5519

全部0条评论

快来发表一下你的评论吧 !