详解RTL设计中多时钟域的处理方法

描述

【 一 】

数字IC系统逻辑设计这部分主要介绍两个方面,一个是RTL的设计基础;另一方面是verilog基本语法。这一篇文章主要介绍一下RTL的设计基础。

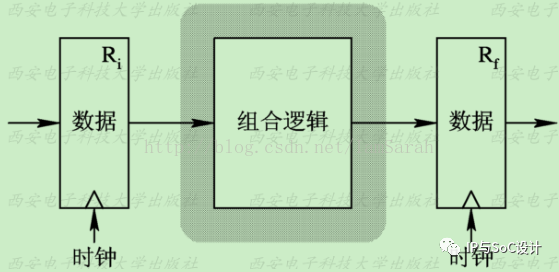

RTL设计都是采用同步电路设计方式,了解同步电路的设计要求是RTL设计的第一步。下图是一个同步电路的示例:

其中,组合逻辑实现设计所需要的功能,寄存器用于暂存数据用时钟控制。只有当时钟进行有效跳变时,才将新的数据所存起来,否则数据保持原值。时钟相当于同步电路中的指挥。时钟一般是由晶振产生,或者由外部输入,如果需要还需要用锁相环进行倍频、相移等操作。

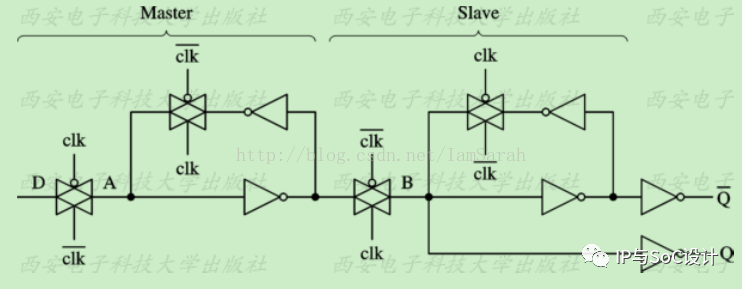

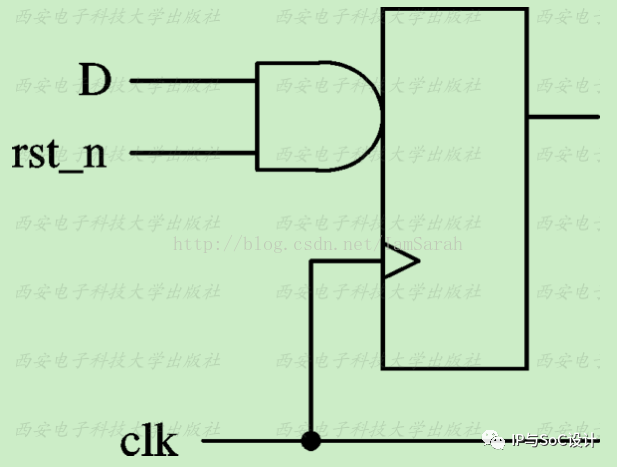

下面对寄存器做一个介绍,一个寄存器的结构如下图所示:

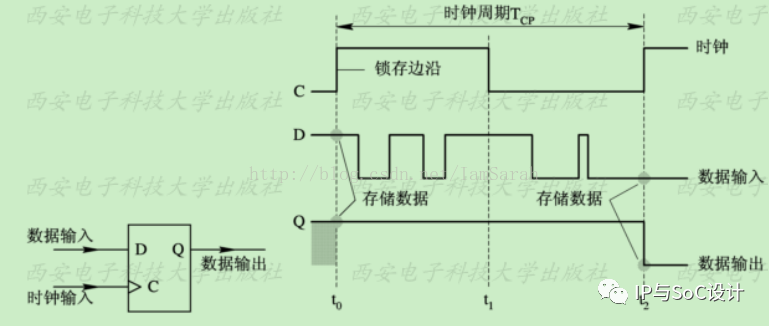

寄存器的功能如下图所示:

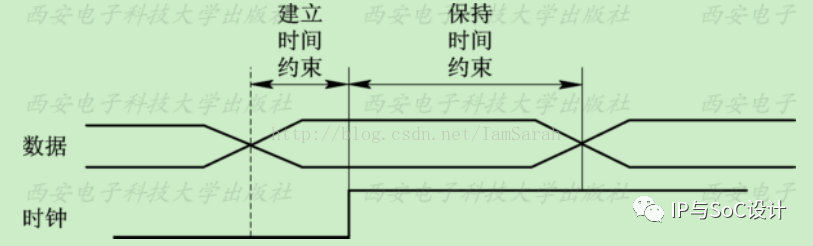

由图可得,该寄存器在时钟的跳变沿锁存数据,然后数据会保持直到下一个跳变沿。寄存器要正常工作,必须保证D端的数据变化与时钟的有效沿不能距离太近,否则有可能锁存错误的数据。在综合库中,规定了数据变化端跟时钟跳变沿最短的时间要求,即建立时间约束和保持时间约束。建立时间规定,在时钟沿到达前的某段时间内,数据必须稳定;保持时间定义了在时钟沿之后的某段时间之后,数据才能发生变化。

对于一个寄存器来说,除了数据端与时钟端有时序要求。异步复位端与时钟端也有要求。假设一个寄存器是已不复位的,复位信号低电平有效。当复位信号是低电平时,寄存器被初始化。当异步复位信号跳高时,寄存器在时钟跳变沿锁存新的数据。如果异步复位信号跳高的时刻距离时钟有效沿太近,寄存器可能继续保持复位状太,也可能锁存新的数据。因此有必要定义时钟有效沿与异步复位无效沿之间的时序要求,这就是recovery/removal的时序要求,如图所示;

寄存器中建立时间/保持时间、recovery/removal的时序要求, 对设计的最大组合逻辑延时、时钟树的构造、复位树的构造都提出了要求。复位树、时钟树一般由后端工具进行处理。对RTL设计者来说,最需关注的是建立时间的问题。设计中的时序违例通过静态时序分析工具可以检查出来。

在IC系统中, 复位的目的是为了将芯片强制到一个已知的状态。同步复位与异步复位都能达到这个目的。两者的差别在于:同步复位需要时钟有效沿到达时才能起作用,而异步复位不需要。如下,是同步复位电路:

同步复位的优点在于:

1)在采用基于周期的仿真器场合,同步复位简单

2)寄存器可以滤掉复位上的毛刺

缺点:

1)需要时钟,在某些场合带来不便。假如设计中包含三态总线,总线上接着许多寄存器。当上电后,晶振还未起振,锁相环还未稳定,这时候没有时钟,所以复位还没有起作用,因此会导致总线上发生冲突。只有增加上电复位电路才能解决此问题。

2)采用同步复位,复位成为路径组合逻辑的一部分,由于复位的负载比较大,因此会使得复位树的延迟比较大,从而导致在路径上的延迟比较大。

异步复位的优点是不需要时钟,且复位不会影响到路径延时。缺点是:复位上的毛刺不能被由它复位的寄存器过滤掉;复位的无效沿与时钟之间存在时序要求。

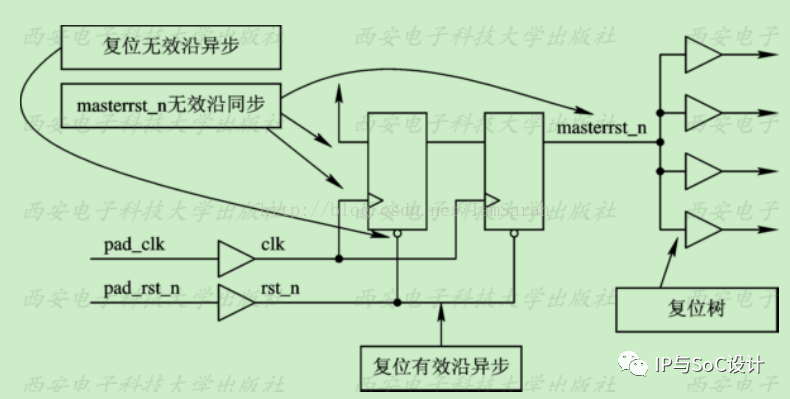

将同步复位和异步复位优点结合起来:给出了一种异步复位,同步释放的复位方法,如下图所示:

该电路的原理是:当复位信号有效时,两个同步器都为低,因此同步器的输出立即变低,而不管此时是否存在时钟。当复位信号变高后,经过时钟跳变沿后才能将高电平锁存到同步器的输出,也就是说,同步器的输出的无效沿是与时钟同步的。

【 二 】

这篇文章主要讲一下RTL设计中多时钟域的处理,之前在异步FIFO设计中已经讲到这个问题,这篇更全面详细的介绍一下多时钟域的处理。

多时钟域之所以难以处理,是因为在两个时钟域之间传递信号时,不可避免地会出现建立时间/保持时间违例的问题。寄存器会锁存错误的数据,引起功能错误。

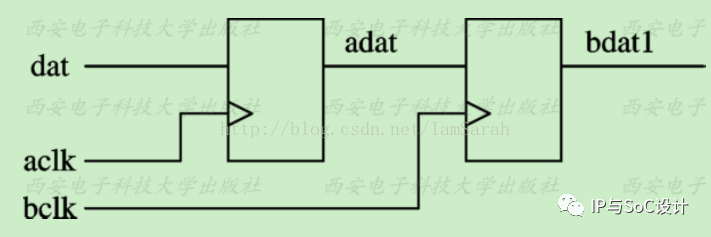

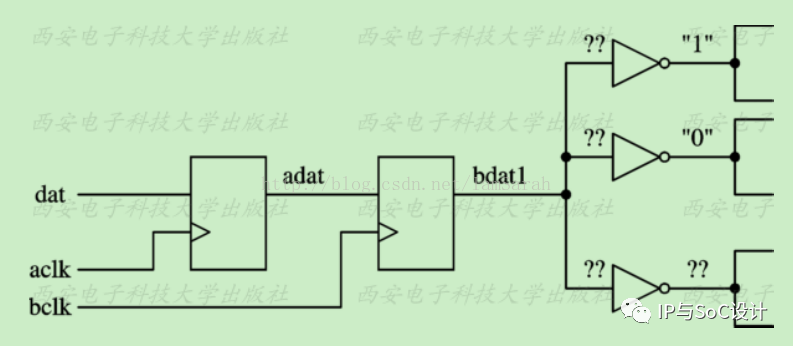

现考虑在两个时钟域间传递1位信号的情况。如下图是多时钟域传递一位信号的示例:

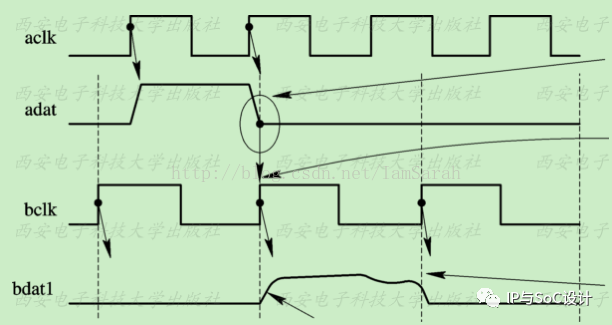

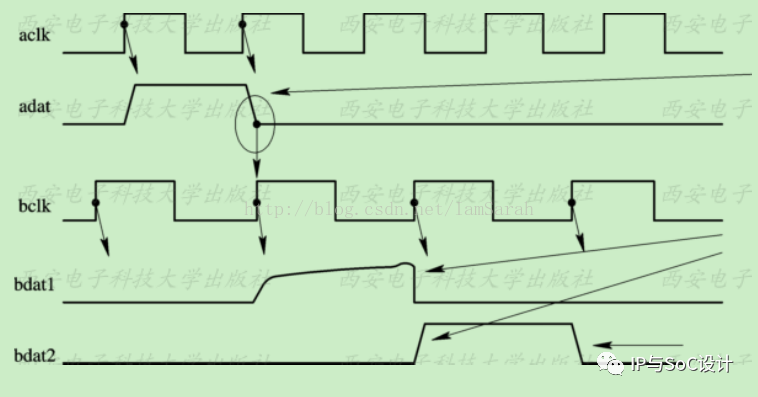

在这个例子中,aclk与bclk是两个异步时钟。由aclk时钟域产生的数据adat要送到bclk的时钟域。由于bclk与aclk不同步,所以会出现这种情形:在一定时刻,adat的变化沿距离bclk的采样沿非常接近,不能满足建立时间和保持时间的要求。这样, 寄存器可能会进入亚稳态。下图是这种情况下的波形图:

bdat1的值会传递给其他模块。在实际芯片中,在bdat1处于亚微态的时候,有些模块会认为自己收到的是“1”, 有些会认为是“0”,这种不一致会导致功能错误,如下图所示:

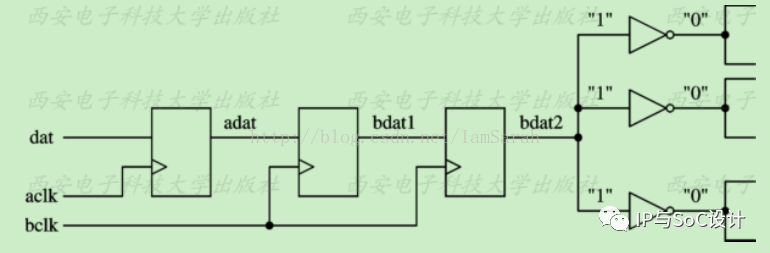

这种情形需要采用下图所示的同步器来避免:

采用同步器之后,其波形如下图所示:

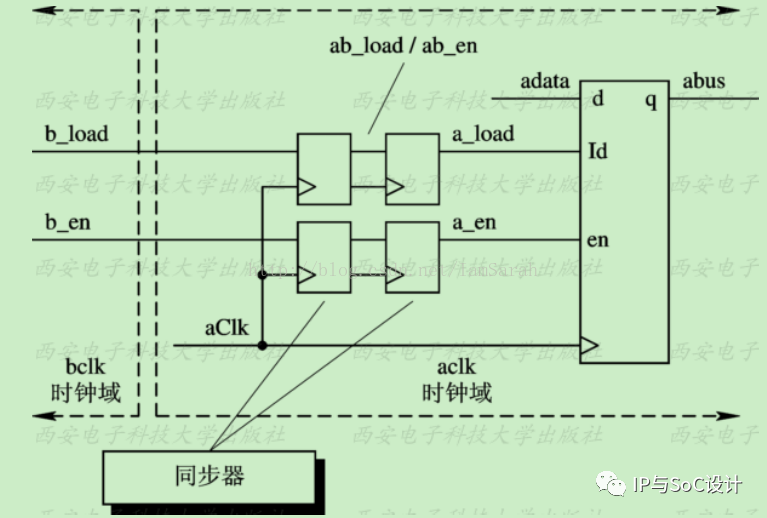

下面看一下相关的多位信号的传递,同步器适用于在多时钟域间传递1位信号,但是对于相关的多位信号,采用这种技术仍然会出现问题。如下图所示,在多时钟域间传递两位信号:

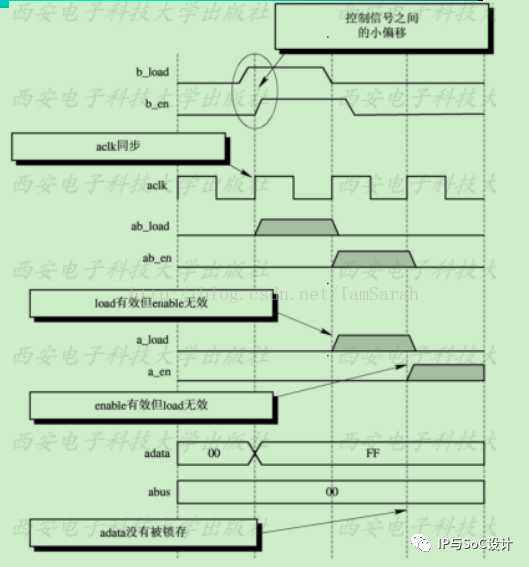

在这个例子中,有两个信号b-load和b-en由bclk时钟域传递到aclk时钟域。这两个信号相关。我们假设在某个时钟周期内, b-load与b-en同时有效,那么这两个信号分别经过同步器后,得到的波形如下所示:

由于b-load信号与b-en信号的延迟不同,两者的上升沿之间有一些偏移。如果同步器的采样时钟正好也位于两个信号变化沿之间, 则采样后的信号有可能会相差一个周期。这种情况下,可以将两个信号进行逻辑与操作变成一个信号送到同步器。但是很多时候,无法对传递信号进行简单的合并。这个时候就可以考虑先将这些信号变成格雷码,然后通过同步器来传递。由于格雷码在一个周期内仅有一位发生变化,这样经过同步器之后就可以得到正确的结果。

上述方案都是基于同步器的,依据的原理是降低寄存器处于亚稳态的概率。另外一种方案是用多组寄存器来存储信号,过一段时间再进行读操作。在开始读操作的时候,数据早已经稳定下来,就不会出现建立时间/保持时间违例的情况。这也就是基于异步fifo在多时钟减传递信号的基本原理。关于异步FIFO的设计,已经讲过,在此不再赘述。

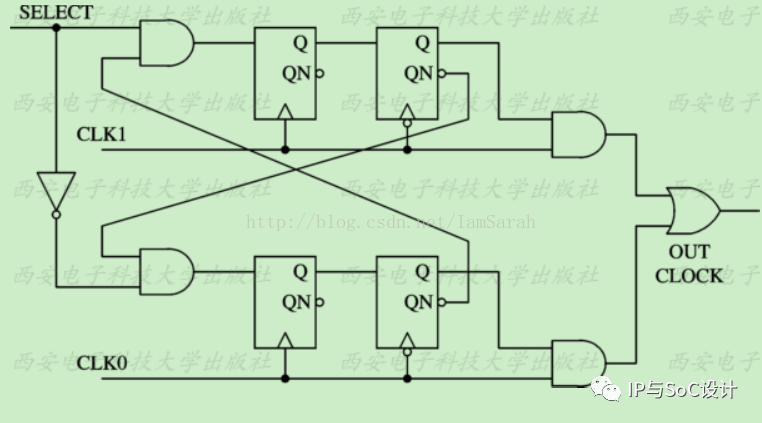

下面讲一下时钟切换电路,有些设计中需要进行时钟切换。动态地将始终从高频切换到低频或者由低频切换到高频,切换过程中会出现毛刺。时钟上的毛刺是非常致命的,可能会导致功能错误。要避免这种问题可以采取两种方法,一种是在时钟切换时,进入复位,当切换完成后,复位结束;另一种方法是采用时钟切换电路,如下图所示,这种切换电路跟锁存器的设计有异曲同工之妙。

原文标题:带你科普RTL设计基础

文章出处:【微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

关于跨时钟域信号的处理方法2022-10-09 8650

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1742

-

多时钟域的设计和综合技巧系列2022-04-11 5864

-

IC设计中多时钟域处理的常用方法相关资料推荐2022-06-24 11533

-

基于多时钟域的异步FIFO设计2009-12-14 590

-

关于FPGA中跨时钟域的问题分析2019-08-19 4098

-

多时钟域的同步时序设计和几种处理异步时钟域接口的方法2020-07-24 5538

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2728

-

RTL中多时钟域的异步复位同步释放2021-05-08 3288

-

解析多时钟域和异步信号处理解决方案2021-05-10 5006

-

介绍3种方法跨时钟域处理方法2021-09-18 23671

-

FPGA中多时钟域和异步信号处理的问题2021-09-23 3960

-

IC设计中的多时钟域处理方法总结2023-04-06 1692

-

FPGA跨时钟域处理方法(二)2023-05-25 1934

-

关于FPGA设计中多时钟域和异步信号处理有关的问题2023-08-23 1677

全部0条评论

快来发表一下你的评论吧 !