锗基衬底抗蚀剂剥离工艺研究

锗基衬底抗蚀剂剥离工艺研究

今日头条

描述

引言

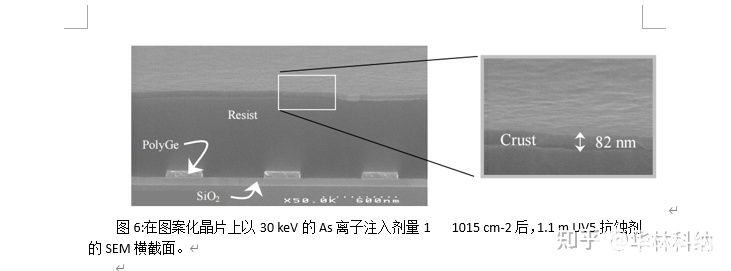

具有高k栅极电介质的锗和绝缘体上锗(GeOI)MOSFET由于锗比硅具有更好的载流子传输特性,最近受到了先进技术节点的关注。对于Ge或GeOI CMOS,必须确定Ge专用的抗蚀剂剥离工艺,因为锗与实际清洗溶液不兼容。初始相容性研究显示了在高N2/(O2+N2)等离子体比的干燥步骤期间锗的钝化作用。对于后有源区蚀刻,在构图的绝缘体上多晶锗(PolyGeOI)晶片上进行的干剥离显示出良好的兼容性。由于水冲洗步骤导致的横向Ge消耗通过干法工艺被最小化,这表明了等离子体钝化效应。注入后剥离特别困难,因为Si典型溶液对Ge具有高度侵蚀性,还因为抗石墨化。使用升温工艺,获得了良好的抗蚀剂去除效率。

介绍

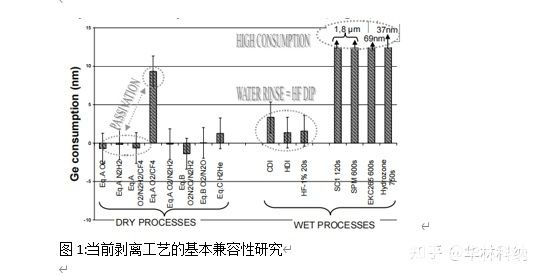

由于其比硅更好的载流子迁移率,锗是高性能MOSFETs的有前途的候选材料。由于与Ge兼容的高k材料,不稳定的天然Ge氧化物不再是在CMOS器件中使用Ge的限制。由于GeO2在水中不稳定,CMOS技术工艺必须适应这种材料。对于CMOS器件,在有源区蚀刻和离子注入之后需要抗蚀剂剥离。在硅晶片上1.8 μm外延锗上进行的测试表明,大多数通常的硅抗蚀剂剥离工艺,结合氧等离子体和湿化学,显著蚀刻锗结构(图1)。

注入后的剥离特别困难,因为抗蚀剂会因注入而硬化,并且侵蚀性化学物质是强制性的。一方面,硫酸过氧化物(SPM)和标准清洁剂1 (SC1 ),它们通常用于去除光刻胶在高剂量植入后,由于GeO2的水溶性,显示与Ge的相容性最差。另一方面,诸如二氧化硅的普通保护层必须由较低温度的沉积材料代替。这种层对离子注入过程引起的损伤更敏感。

本研究的目的是我们华林科纳寻找一种有效的锗基衬底抗蚀剂剥离工艺。为了实现这一点,研究了在干燥步骤中形成钝化层以保护Ge免受氧化步骤的影响。由于已知等离子体中的N2或H2添加剂会钝化各向异性蚀刻中的侧壁,所以研究了将这些气体添加到标准灰化工艺中。第一项研究在毯式晶片上进行,以调查兼容性。然后,在图案化的晶片上评估后有源区蚀刻和注入后抗蚀剂去除的相容性和效率。

结果和讨论

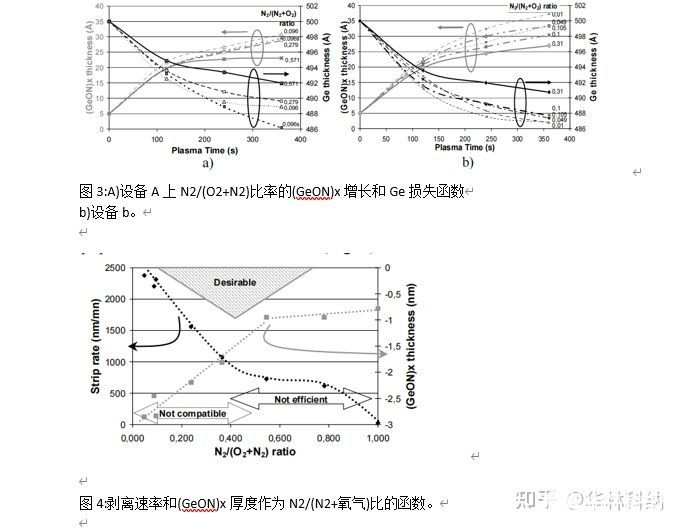

在多晶硅覆盖层晶片上进行初始兼容性研究。对于不同的N2/(O2+N2)比,通过椭偏仪测量多晶硅锗层上钝化层的生长,称为(GeON)x,以及相关的锗损失。图3-a和B显示了干燥设备A和B的(GeON)x增长(灰色)和Ge损失(黑色)。这些测量结果表明,N2/(O2+N2)比越重要,钝化层越薄。需要强调的一点是设备A上的N2/(O2+N2)比率为0.57:可以看到(GeON)x增长饱和,导致最低的Ge消耗。(GeON)x生长稳定,表明钝化结束。

在设备A上,用相同的N2/(O2+N2)比(0.096)测试了两种不同的CF4流。不太重要的CF4流量称为0.096 std,是当前标准工艺中使用的CF4流量。对于这两种不同的CF4流,看不到明显的变化。

为了最大限度地减少湿法清洗过程中的氧化物消耗,HF 0.1%比HF 1%更好。对覆盖氧化物晶片的测试显示在该溶液中蚀刻缓慢,几乎为2.1纳米/分钟(表II)。30秒或更短时间的HF 0.1%浸渍可通过剥离去除残留物。这种HF浸泡也将使氧化物表面变得平滑,用于下一步的光刻。

结论

由于与Ge兼容的高k材料,不稳定的天然Ge氧化物不再是在CMOS器件中使用Ge的限制。技术过程必须适应这种材料,特别是剥离,因为它与当前的清洗溶液不相容。

在本文中,在对基于Ge的晶片的初步研究中,评估了N2/(N2+O2)比在干剥离工艺中的影响。结果表明,必须在一方面具有高比率的氮和另一方面保持良好的抗蚀剂去除效率之间找到折衷。

对于Ge活性区域剥离,已经发现灰化步骤的可接受兼容性水平。必须继续进行研究,通过XPS研究更好地了解钝化机制以及水洗过程中钝化层的行为,将水洗过程中的CD损失降至最低。

对于注入后剥离,利用升温干燥工艺已经实现了良好的效率;然而,需要HF浸泡来去除所有的残留物,并且为了下一步的光刻而平滑表面。为了最小化氧化物消耗,注入后退火需要氧化物,HF 0.1%的浸渍比HF 1%更好。

-

图形反转工艺用于金属层剥离的研究2009-10-06 10515

-

双面柔性PCB板制造工艺及流程2011-02-24 3438

-

PCB液态光致抗蚀剂制作工艺浅析2010-10-25 863

-

抗蚀剂的涂布-双面FPC制造工艺分析2018-03-19 5735

-

详解无臭氧抗蚀剂剥离工艺2022-03-30 1187

-

光刻胶剥离和光掩模清洁的工艺顺序2022-04-01 1101

-

通过光敏抗蚀剂的湿蚀刻剂渗透研究2022-04-22 1223

-

光致抗蚀剂剥离和清洗对器件性能的影响2022-05-06 984

-

光刻胶剥离工艺的基本原理2022-05-12 3621

-

新GaAs IC 金属剥离的方法2022-06-27 1777

-

一文详解光刻胶剥离工艺2022-07-12 3181

全部0条评论

快来发表一下你的评论吧 !