分级优先级编码器电路图解析

描述

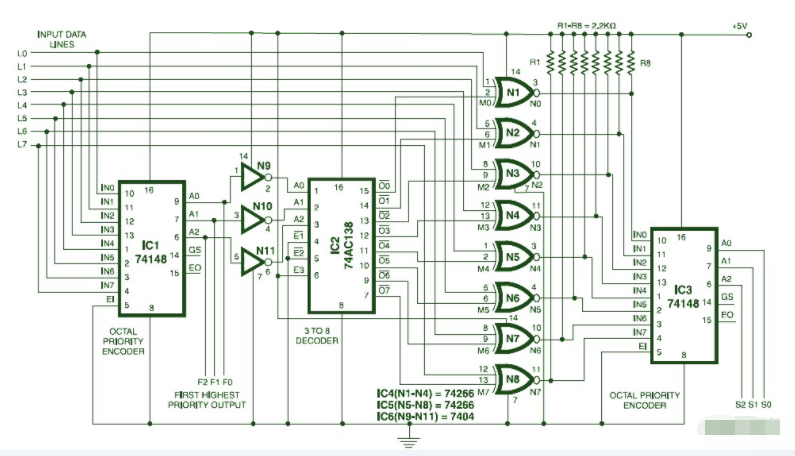

图是分级优先级编码器电路。在维基百科上描述,优先级编码器是一种电子电路或算法,可将多个二进制输入压缩成较少数量的输出。优先级编码器的输出是从最高有效输入位的零开始的序数的二进制表示。它们通常用于通过处理最高优先级的请求来控制中断请求。”

异常优先级编码器仅对最高阶数据线进行编码。但在许多情况下,不仅需要最高优先级信息,而且还需要次高优先级信息。这里介绍的电路对8行输入数据的最高优先级信息和次高优先级信息进行编码。该电路使用标准八进制优先级编码器74148,它是一个8线到3线(4-2-1)二进制编码器,具有“低”有效数据输入和输出。

第一个编码器(IC1)生成最高优先级值,例如F。IC1的有效“低”输出(A0、A1、A2)由门N9到N11反转并馈送到3线到8线解码器(74138),需要有源“高”输入。解码输出为“低”有效。解码器识别最高优先级的数据线,并使用XNOR门(N1到N8)取消该数据值,以保留由第二个编码器生成的第二高优先级值。

为了理解逻辑,让输入数据线表示为L0到L7。Lp是最高优先级线路(有效-“低”),Lq是次高优先级线路(有效-“低”)。因此Lp=0和Lq=0。Lp之上以及Lp和Lq之间的所有线(表示为Lj)都处于逻辑1。Lq逻辑状态之下的所有线都是不相关的,即“不关心”。这里p是最高优先级值,q是次高优先级值。(显然,q必须小于p,并且p的最小可能值被视为“1”。)

优先级编码器IC1生成二进制输出F2、F1、F0,它表示“低电平有效”格式的p值。补码后的F2、F1和F0被施加到3线到8线(八个输出中的一个为“低电平”有效)解码器74138。让74138的输出线表示为M0到M7。现在在M0到M7中只有一条线是“低”有效的,那就是Mp(其中p的值如上所述)。因此Mp线的逻辑电平为“0”,其他M条线的逻辑电平为“1”。

如图所示,使用八个XNOR门取消了最高优先级的线。让XNOR门的输出线为N0到N7。考虑相应XNOR门的输入Lp和Mp。因为Mp=0并且Lp=0,所以这个XNOR门的输出是Np=Lp=1的补码。所有其他L”都不会改变,因为相应的M”都是1”。因此,数据线N0到N7与L0到L7相同,只是L0到L7中的最高优先级在N0到N7中被取消。

N0到N7中的最高优先级是从L0到L7剩余的第二高优先级,即Nq=0和Nj=1用于q到优先级编码器2(IC3)以生成代表q的S2、S1、S0。因此提取第二高的优先级值。通过级联可以恢复第三高的优先级,以此类推。

例如,让L0到L7=XXX01101。这里最高的“0”行是L6,次高的行是L3(X表示“不关心”)。因此p=6和q=3。现在第一优先级编码器的“低”有效输出将为F2F1F0=001。74138的输入为110,它输出M0到M7=11111101。由于M6=0,只有L6由XNOR门补充。

因此,XNOR的输出为N0到N7=XXX01111。现在N3=0,“N”的最高优先级为3。优先级编码器2(IC3)将该值恢复为S2S1S0=100。

-

怎么实现8237 DMA控制器中使用的优先级编码器2019-04-24 1045

-

中断实现控制led灯解析优先级2021-08-16 1127

-

音调编码器电路图2009-03-23 1832

-

stm32定时器优先级2017-10-13 6009

-

优先编码器形式及作用2019-06-22 24076

-

SN5474LS147和SN5474LS148及SN5474LS748优先级编码器的数据手册2019-09-03 3176

-

STM32单片机中抢占优先级和响应优先级的表达方式解析2019-10-14 12458

-

STM32的中断:抢占优先级和响应优先级资料下载2021-04-03 1282

-

cortex M内核优先级设置2021-12-01 866

-

STM32F103芯片中断优先级以及FreeRTOS优先级设置2022-01-25 1734

-

中断优先级处理的原则及配置 抢占优先级和响应优先级的区别2022-05-18 31999

-

Free RTOS的优先级翻转2023-02-10 2657

-

什么是优先级反转2023-04-24 3599

-

二进制编码器的种类及特点2024-11-06 2468

-

优先编码器:高效数据选择与编码的解决方案2025-03-25 1300

全部0条评论

快来发表一下你的评论吧 !