RISC-V设计的基本安全协处理器PUFiot

描述

2021 年连接的物联网设备数量超过 460 亿,预计到 2030 年将达到惊人的 1250 亿。这将显着改变半导体市场,因为每个物联网设备都需要一个处理器内核来有效处理大量数据和相关交易。为了充分利用这种市场潜力,RISC-V 架构已成为 SoC 设计人员替代 x86 或 ARM 的新选择,这要归功于其开放的指令格式和低成本。

然而,随着物联网市场的不断扩大,对抗性攻击的破坏性也在不断扩大。连接应用程序的安全性现在是其设计的基本要素。连接的设备必须能够相互验证,确保安全的数据传输,并包括安全存储。虽然RISC-V 的安全指南仍在制定中,但为 RISC-V 用户提供有效的即插即用解决方案以加强 SoC 及其他产品的安全性至关重要。

需要什么样的设计来保护物联网应用?

在大多数情况下,需要考虑六个关键的 SoC 安全因素……

可信执行环境 (TEE):隔离需要更高安全级别的代码、数据和内存。

信任根:保护关键的安全参数;包括唯一 ID、证书、密钥和安全存储。

安全启动:阻止未经授权的操作系统和应用程序运行。

静态数据安全性:以加密/模糊的形式存储数据,具有可靠的访问控制以防止泄漏。

传输中的数据安全性:在传输前利用密钥对数据进行加密,以防止被截取。

安全 OTA 更新:确保现场的固件或软件更新以加密密文形式提供,并且不允许降级。

仅靠 CPU 无法达到这六个安全因素。芯片的设计需要一个密钥存储单元和一组密码算法来帮助 CPU 执行安全功能,包括身份验证、加密、解密和完整性检查,以实现这些功能。此外,安全操作(与非安全操作分开)需要一个隔离且可信的安全执行环境。还应实施防篡改设计,以保护安全环境免受攻击。

考虑到这些风险,经验丰富的设计人员通常会使用带有硬件信任根和防篡改设计的安全协处理器,以支持 CPU 执行应用程序和服务的所有必要安全功能。

弥补现有协处理器的不足

安全协处理器负责系统内与安全相关的事务,并允许 CPU 安全地执行其主要功能。实施后,硬件加速的安全协处理器将保护敏感信息并比 CPU 更有效地执行安全功能,而不会影响其计算能力。这不仅简化了系统设计,而且提高了整体性能。

在其架构中,ARM 提供与其 CPU 集成的 CryptoCell-312 作为安全协处理器来处理安全操作。相比之下,RISC-V 生态系统仍在成熟,还没有适合安全协处理器的解决方案。RISC-V 用户必须自行开发或采用合作伙伴的 IP 才能获得上述安全功能。如果他们选择内部开发,可能会出现一些挑战。他们有足够能力的安全开发团队吗?它将如何影响上市时间?自主研发的安全功能能否获得认证?当技术问题出现时,他们处理的能力如何?最后,成本是多少?所有这些挑战都可以通过采用来自有能力的合作伙伴的集成 IP 来避免。

现有解决方案缺乏全面的硬件信任根,也没有提供稳固的安全边界,因此容易受到攻击。市场上的大多数安全协处理器可能涵盖一到两个关键功能,但不足。例如,一些协处理器不支持某些加密算法,容易受到攻击,或者没有通过第 3 方认证。有些没有为密钥提供安全存储,导致协处理器从安全边界之外检索密钥(想象将您的密钥留在前门的保险库)。即使包括安全密钥存储在内的选项也存在不可避免的缺点,需要在生产过程中将密钥一一注入芯片,这使得制造或操作成本高昂且难以操作。一些协处理器对所有产品都有相同的激活密钥,

所有这些不足之处最终都可能成为物联网设备中的漏洞,这将不可避免地成为黑客入侵网络的目标。因此,即使是仅传输非敏感数据的微型物联网设备,如果被黑客操纵也可能造成巨大伤害。类似的事件数不胜数,最近的一次是 2021 年 5 月,当时最大的输油管道系统 Colonial Pipeline 遭到攻击。他们不仅关闭了整个管道,政府甚至还发布了区域紧急声明。仅支付的赎金就损失了420万美元。

PUFiot 支持 RISC-V 架构的片上安全性

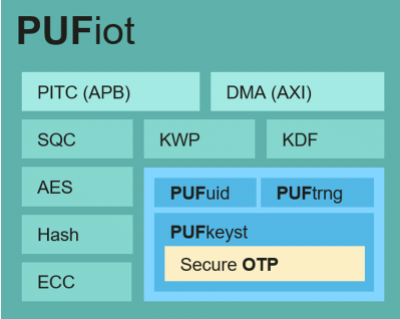

为了解决 RISC-V 生态系统中缺乏完整的安全协处理器的问题,PUFsecurity 的集成 IP 解决方案之一 PUFiot,是终极答案。它受到多层设计的保护,利用了一整套完全集成的硬件安全 IP。与纯粹基于软件的设计不同,PUFiot 的安全边界基于硬件的物理分离,因此建立了完善的可信执行环境 (TEE)。图 1 展示了 PUFiot 的设计架构。PUFiot 的核心是模拟硬件信任根设计。硬件信任根包含 eMemory 的专利 NeoPUF,为每个芯片提供唯一的芯片指纹 (UID),并提供 Riscure 认证的防篡改安全 OTP 用于密钥存储,防止对关键安全参数的物理/电气攻击。硬件信任根还带有一个真随机数生成器 (TRNG),

图1:PUFiot的设计架构

PUFiot 支持一整套 NIST CAVP 认证和第 3 方认证的中国 OSCCA 硬件密码算法。由于模块化设计,PUFiot 加密算法的定制仍然很灵活。这意味着用户的要求,例如在 SM4 和 AES 之间进行选择,可以在一个简单的过程中得到满足。因此,PUFiot 可以满足 RISC-V 当前和未来的安全要求。除了安全功能外,众多的数字和模拟防篡改设计进一步加强了 PUFiot,使其成为可靠的安全协处理器。同样,为了降低整个 SoC 系统设计的复杂性,PUFiot 支持用于寄存器访问控制的标准 APB 控制接口和具有标准 AXI4 控制接口的 DMA,以快速访问存储在系统内存中的大量数据。

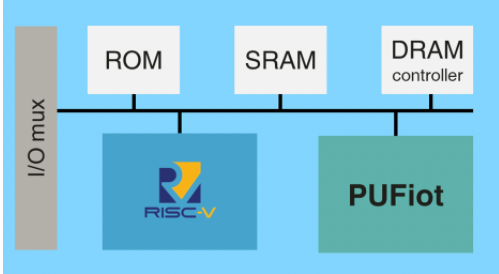

连同 NIST 标准的密钥包装 (KWP) 和密钥派生函数 (KDF) 以保护密钥的使用和导出,PUFiot 可以为 RISC-V 物理内存保护 (PMP) 按需生成多个密钥,以分别保护每个应用程序。此外,PUF 的特性非常适用于安全启动和安全 OTA 更新,因为不同物联网设备上的相同软件每个都有其密钥。因此,我们可以为即将进入市场的数十亿新物联网设备奠定坚实的安全基础。图 2 显示了以 PUFiot 作为其安全协处理器的 RISC-V SoC 设计。

图 2:包含 PUFiot 的 RISC-V SoC 设计

结论

为了保护 IoT 应用程序,PUFsecurity 利用芯片指纹技术来强化信任根,并开发了 PUFiot,这是一种具有广泛安全边界的安全协处理器,可以轻松集成到安全的 RISC-V 系统中。PUFiot 支持物联网世界所需的零接触部署。通过硬件加速的安全功能和访问控制,PUFiot 还满足云应用中的零信任安全要求。因此,PUFiot 作为一种安全解决方案非常适合配备 RISC-V 处理器的物联网设备。

审核编辑:郭婷

-

基于E203 RISC-V的音频信号处理系统 -协处理器的乘累加过程2025-10-28 231

-

Andes晶心科技推出D45-SE RISC-V处理器2024-12-26 1949

-

RISC-V协处理器是否可以像基于堆栈的ULP那样访问i2c硬件呢?2023-03-02 563

-

请问ESP32s3 ULP RISC-V协处理器是否支持ADC的读取?2023-02-13 589

-

求助,ULP RISC-V协处理器周期性唤醒的BUG怎么处理?2023-02-09 861

-

Codasip通过收购Cerberus增强RISC-V处理器设计的安全性2022-11-16 904

-

用于RISC-V设计的基本安全协处理器2022-10-18 1316

-

RISC-V设计的基本安全协处理器2022-08-16 2292

-

RISC-V开源处理器核介绍2021-07-23 2414

-

RISC-V是什么?如何去设计RISC-V处理器?2021-06-18 2736

-

RISC-V是通用RISC处理器还是可定制的处理器?2020-11-17 4520

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4366

全部0条评论

快来发表一下你的评论吧 !