Routing Complexity是什么含义呢?

描述

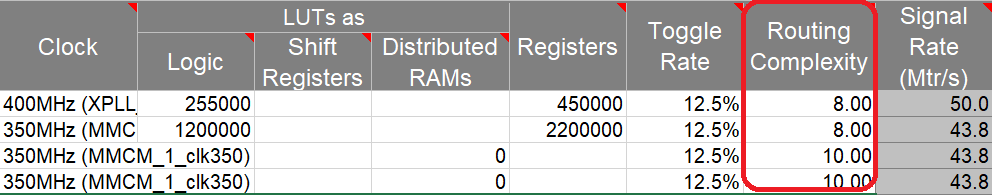

在对Xilinx FPGA设计进行功耗评估时,都要用到XPE(Xilinx Power Estimator)。从2015.4版本开始,针对UltraScale/UltraScale+器件,Fanout被Routing Complexity所取代,以获取更为精确的的评估结果,如下图所示。

在老版本的XPE中,对于动态功耗,需要准确填入扇出以估计布线资源的使用率。这里有一个假设:扇出越大,消耗的布线资源就越多。这会带来一个问题:如果一个设计中的短线或长线用得比较多,那么评估的布线模型就与实际布线结果不同。为了补偿这个差异,从2015.4版本开始,用物理实现的Routing Complexity取代了逻辑定义的扇出。 那么Routing Complexity是什么含义呢?

Routing Complexity实际反映的是每个logic cell使用的布线资源的平均数目。此值越大说明布线拥塞程度越高。典型值为8(也是默认值),可满足大部分设计的需求。同时,应将此值控制在5~15之间,过高(超过15)或过低(小于5)都不合适。例如,对于一个全局复位信号,其扇出非常大,导致Routing Complexity可能超过20,毕竟这个net需要到达芯片几乎所有的逻辑单元。但这种情况是比较罕见的。另一方面,某个net扇出为1,并且源端和目的端在同一个SLICE,那么Routing Complexity就会非常低。这种情况也是非常罕见的。 在填写Routing Complexity时,需要考虑如下几个因素:扇出、芯片规模、设计的资源利用率、综合或布局布线跟Floorplan相关的选项。 另一方面,如果我们已经有一个现成的设计,并完成了布局布线,那么可以在Vivado下利用命令report_power生成.xpe,并将该文件导入到XPE中,相应的Routing Complexity的值就会被反标到XPE里,这样可获得较为精确的Routing Complexity。

审核编辑 :李倩

-

Tapped routing知识点2023-02-11 2641

-

cdl in总是报错”in global routing, two instances overlap"怎么解决?2021-06-24 2590

-

通过Tabbed Routing测试结果研究该设计方法的利弊2020-08-20 2555

-

Design Complexity、congestion、Timing2017-02-08 5835

-

Routing_Guide2016-12-14 787

-

PCB_Auto-Routing设计2016-01-11 831

-

BGA routing guide2013-05-27 2239

-

PCB routing 策略&routingchecklist2012-08-20 2031

-

S3C6400_Routing Guide2011-08-01 598

-

Agilent N2X IPv6 Routing Emula2010-07-25 1012

-

Agilent N2X IPv4 Routing Emula2010-07-22 646

-

什么是Routing Policy2010-02-23 1058

-

PADS Routing Solutions使用教程2008-05-11 811

全部0条评论

快来发表一下你的评论吧 !