电容对信号上升沿的影响

电子说

描述

负载电容(IO电容)Cin对信号上升沿的影响

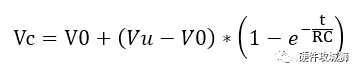

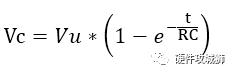

任何芯片IO都有输入电容,通常为2pf左右,加上寄生电容,大约3ps。这个电容相当于负载电容,高速信号在这个电容上建立电压,相当于给电容充电,电容的充电公式是:

V0是电容初始电压,Vu充满后的电压值,假设V0=0V。那么上面公式简化为:

当t = RC时,Vt = 0.63Vu;

当t = 2RC时,Vt = 0.86Vu;

当t = 3RC时,Vt = 0.95Vu;

当t = 4RC时,Vt = 0.98Vu;

当t = 5RC时,Vt = 0.99Vu;

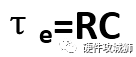

我们平时用的时间常数τe指电容两端电压从0V上升到1-1/e=1-37%=63%所需的时间(e=2.71828);

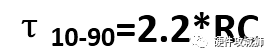

利用上述公式,计算出上升时间10%~90%所需要的时间是:

如果传输线阻抗50Ω,Cin=3pf,则τ10-90=0.33ns。如果信号的上升时间小于0.33ns,电容的充放电效应将会影响信号的上升时间。如果信号的上升时间大于0.33ns,这个电容将使信号上升时间增加越0.33ns

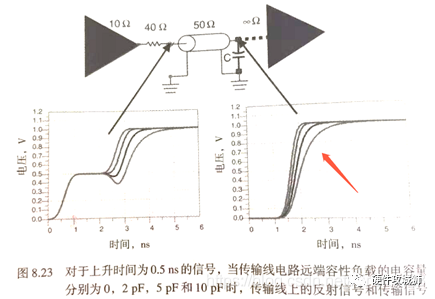

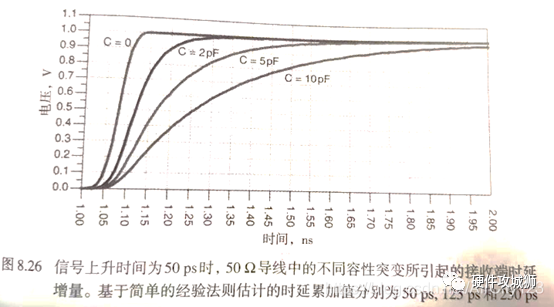

负载电容对信号上升沿的直接影响就是延长了上升时间,如下图:

线路中途容性负载对信号的影响

测试焊盘,过孔,封装引线或者连接到互连线中途的短桩线,都有寄生电容,相当于容性负载。这些容性负载通常是pf级别。

假设这些容性负载导致阻抗突变为25Ω,这导致信号传输到这里,有负的信号被反射,然后入射信号降低。当信号到达负载端后返回,在这个点,又有负的信号返回到负载端。从波形上看就是信号幅度下降,下冲,振铃,上升时间增加。

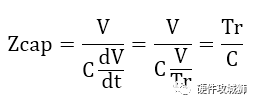

下面计算一下线路中途负载电容的阻抗:

假设上升沿是线性的dV/dt=V/Tr;

如果C很小,则Zcap很大,如果远远大于50Ω,那么与传输线的阻抗并联,几乎不影响整个传输线阻抗。如果Zcap的值与传输线相当,它与传输线50Ω并联,形成比50Ω小的阻抗,就会引起信号完整性问题。

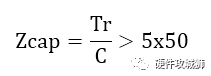

经验法则是Zcap>5x50Ω,就不会引起信号完整性问题。带入上述公式:

也即是:

假设上升时间是1nf,则允许的电容量为4pf;如果上升时间是0.25ns,则允许的电容量是1pf。

容性突变对信号上升时间的影响有一个经验公式:

50Ω传输线,对于2pf容性突变,传输信号的10-90%上升时间增加约50x2pf=100ps。50%门限的延迟累加约为0.5x50x2pf=50ps。

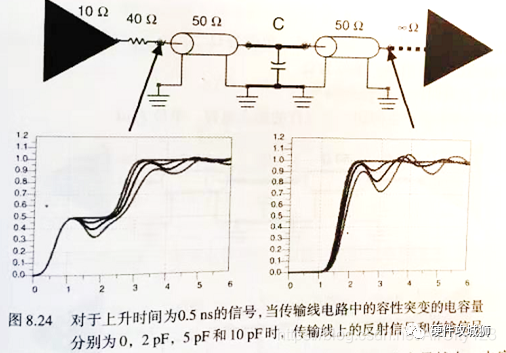

50%门限的延迟成为延迟累加,用这个衡量电容突变对延迟的影响比较准确。上面的经验公式比较准确,下面是仿真结果,基本能吻合:

要想降低电容突变对信号上升沿的影响,如果电容降低不了,就只能降低传输线阻抗了。

审核编辑 :李倩

-

为什么脉冲数字信号的波形中其上升沿和下降沿展开后会有边沿震荡2024-02-06 4121

-

EMC抗扰度之慢上升沿信号2023-12-08 1269

-

rs触发器是上升沿还是下降沿 触发器如何确定是上升沿2023-09-12 12073

-

使用SCL语言开发上升沿或下降沿指令2023-07-20 8245

-

扫描操作数的信号上升沿2023-06-27 3967

-

西门子1200上升沿和下降沿的操作流程2023-06-01 6086

-

信号带宽与上升沿的关系是怎么来的?2023-05-25 4205

-

安全PLC使用的上升沿和下降沿2023-02-20 6182

-

P_TRIG:扫描RLO的信号上升沿2023-01-29 4841

-

P_TRIG与N_TRIG扫描RLO的信号上升沿与下降沿2022-07-23 20003

-

负载电容(IO电容)Cin对信号上升沿的影响2022-06-28 6138

-

上升沿检测电路学习笔记2022-01-18 1491

-

上升沿和下降沿是什么意思?2021-12-08 11885

-

上升沿触发器有哪些2018-02-24 21539

全部0条评论

快来发表一下你的评论吧 !