关于边缘检测工程的问题解答

今日头条

描述

二、高手修炼专题课

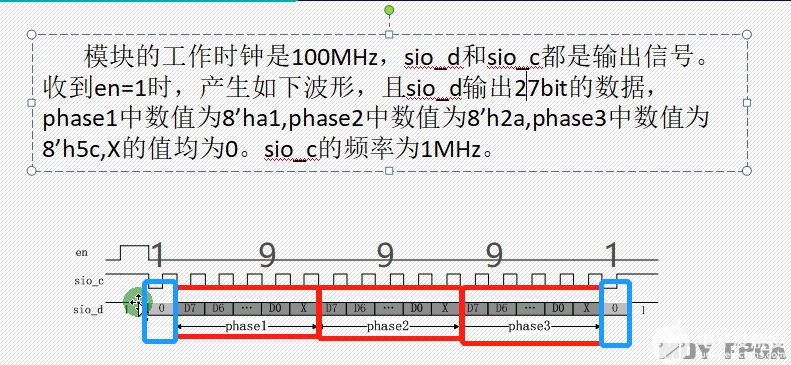

【问题2.1】计数器练习的9.4节中,第二个计数器的代码为什么是计30个呀?我认为应该是3*(8+1)+2=29个。

答:数据位一共是27位,开始位1位,结束位1位,还要注意看上图中,第三字节x后还有1位的0,之后才是结束位,所以一共是30位。

三、实用调试技巧专题课

四、FIFO架构设计专题课

【问题4.1】关于FIFO的深度计算问题,可以看此贴:

此答案来自于明德扬的书籍《手把手教你学FPGA》,电子版可以在此贴下载

【问题4.2】图中X代表什么意思

答:这个X是表示并串转换的次数。FIFO输出的Q是32位,正常情况下,是有4个字节的有效数据,因此x=4。但有一个情况,在包文的最后一个数据时,有可能是只有1字节、或者2字节、或3字节,或4字节有效,这个有效多少是取决于mdy的值(经过FIFO后,即是Q的33和32位)。可以代入数据可以看到x的值。例如:当q[33:32]=1时,表示有1字节无效,即3个字节有效,所以此时x等于3。

五、综合项目实践课——温度检测工程

六、综合项目实践课——边缘检测工程

【问题6.1】点拨开发板,下载工程检测工程后,没有反应。

答:注意:下载后,需要按下矩阵键盘的按键0(即左上角第一个按键),才能显示!!!

【问题6.2】点拨开发板可以显示摄像头拍摄过来的图片吗?

答:由于点拨开发板的资源不足,所以无法显示摄像头的图片,如要显示,建议购买MP801开发板。

【问题6.3】PCLK的时钟频率问题

答:FPGA提供XCLK给摄像头,摄像头利用XCLK产生PCLK。所以PCLK来源于XCLK,所以XCLK是多少,PCLK就是多少。

也就是说PCLK和XCLK频率大小一样,只是说可能不同相

【问题6.4】是否不使用PLL,而是用PCLK来作为采集模块的时钟?

答:PCLK经过插件连到FPGA,这其中可能会不稳定。为解决此问题,将PCLK连到PLL,产生一个同频同相的时钟,

使用这个时钟作为采集模块的工作时钟。这样,即使PCLK缺少或者不稳定,但产生的时钟也会保持稳定。

【问题6.5】摄像头寄存器配置模块中,配置的是04对应RGB,但是数据手册中RGB应该是01,这是为什么?

答: 这里的Bayer RAW本质上是RAW RGB格式,也是RGB格式。

RAW RGB:在摄像头里没有经过任何处理的数据。

RGB:在摄像头里经过了ISP等算法处理的数据。

如果想要最原始的数据,就使用RAW格式;如果要摄像头先美化一下,就使用RGB格式。想要哪种格式,取决于您的需求。

【问题6.6】边缘检测寄存器是怎么样配置的呢?

答:边缘检测中,ov7670_cfg模块和sccb模块,就是用来配置的,可以参考

【问题6.7】边缘检查课程案例OV接口是用MIMP还是DVP的?

答:OV7670是标准的SCCB接口,兼容IIC接口

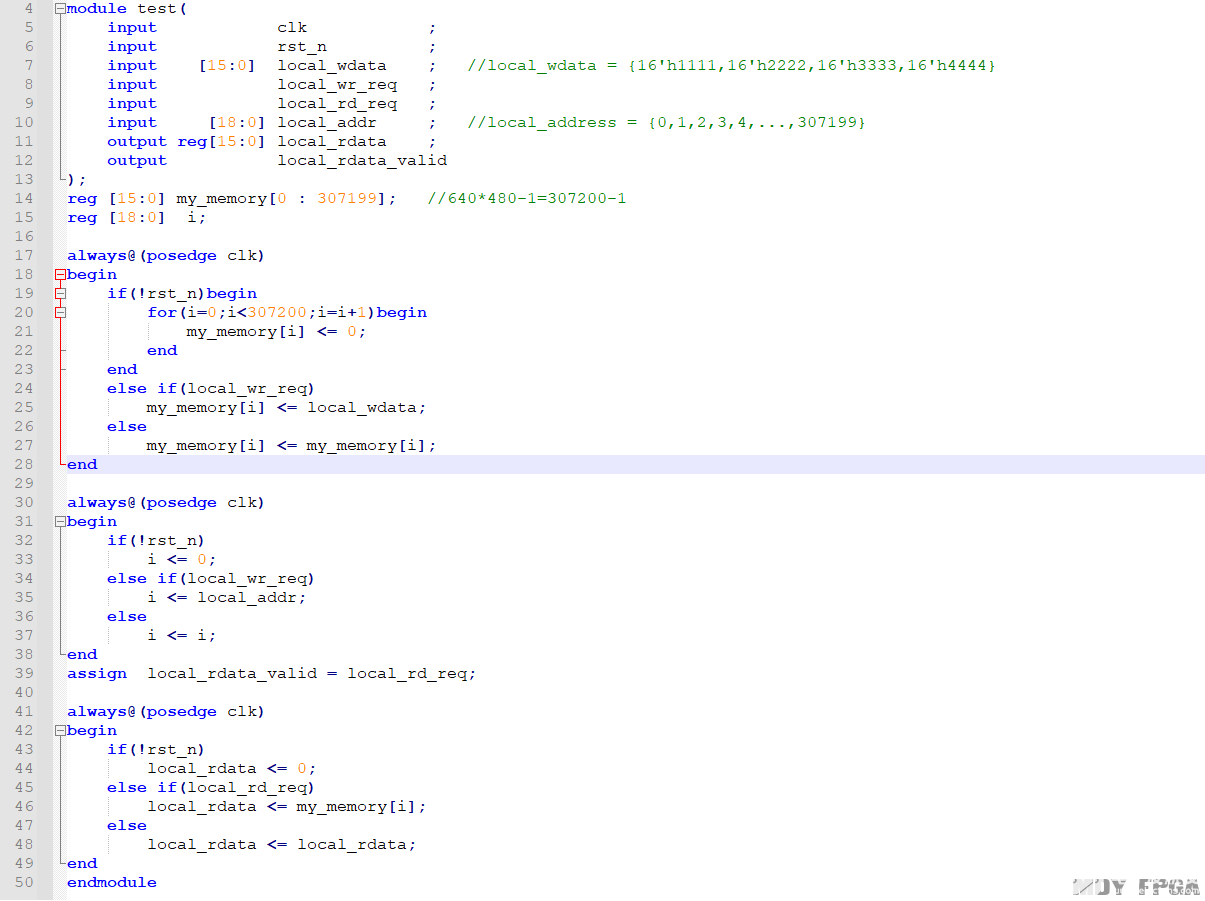

【问题6.8】请问在边缘检测模块中的vga_config模块,如果想显示完整的一帧图像(假设为彩条显示)而ram资源不够,我用的多维数组来做存储器存储16bit 640*480个像素点,

(目的:在local_wr_req时将写数据按地址存进去,在local_rd_req时将数据按地址读出来),请问以下代码方案是否可行,若不行,请问该如何实现此目的?(代码如下图示)

答:

1. 使用二维数组代替RAM方法:二维数据使用的是寄存器资料,通常RAM资源是远远大于寄存器资源的,所以RAM不足时,寄存器一般也不足。

2. 如果只是仿真用途,这个是可以的,可以不考虑资源。既然是仿真,那自然也可以增大RAM了。

3. 注意上面代码中有错误,读写地址是独立,不是共同一个的。读哪些地址数据,无关写地址。上面代码中不正确,具体请仿真。

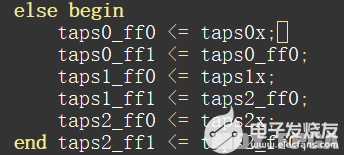

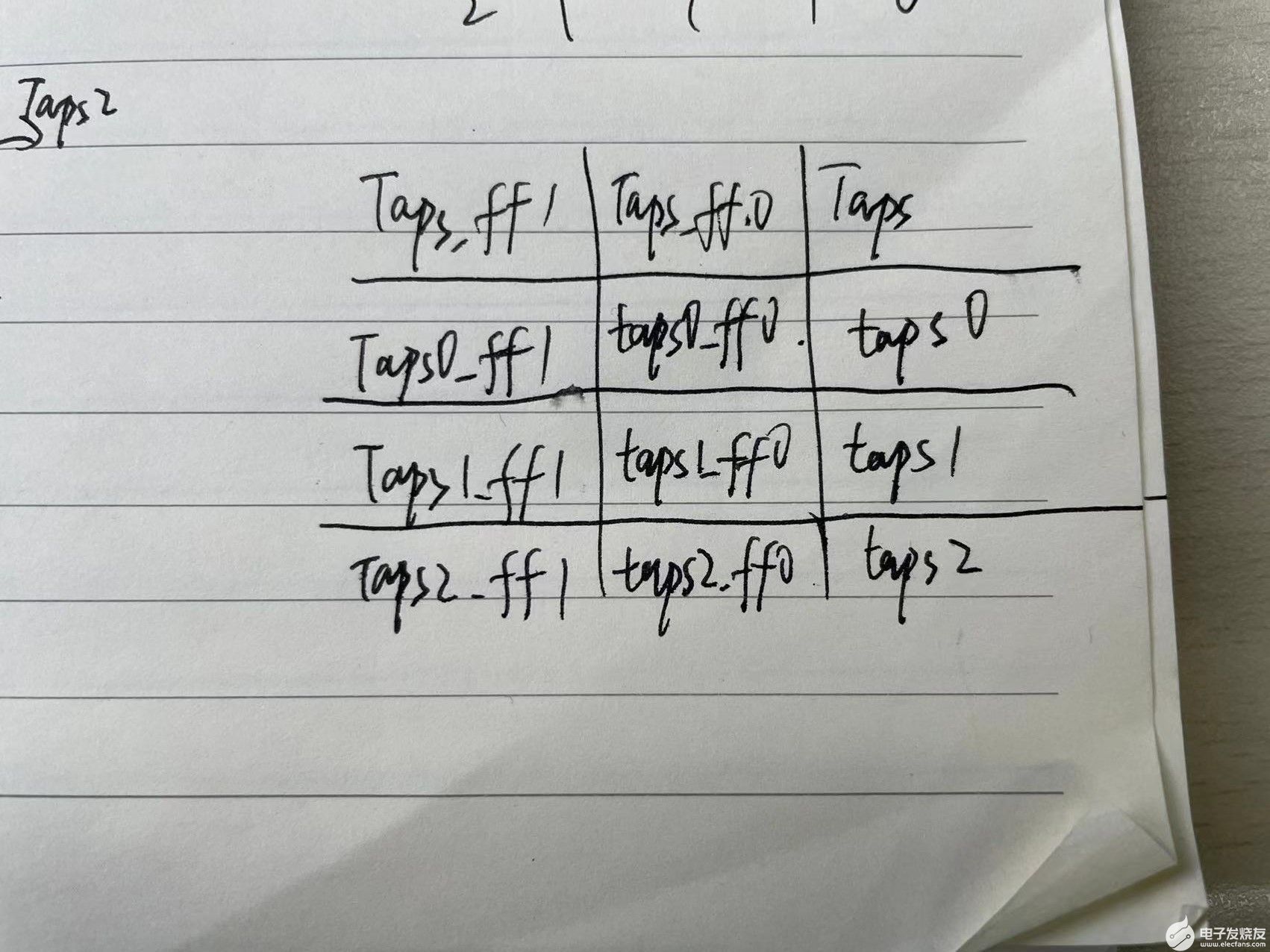

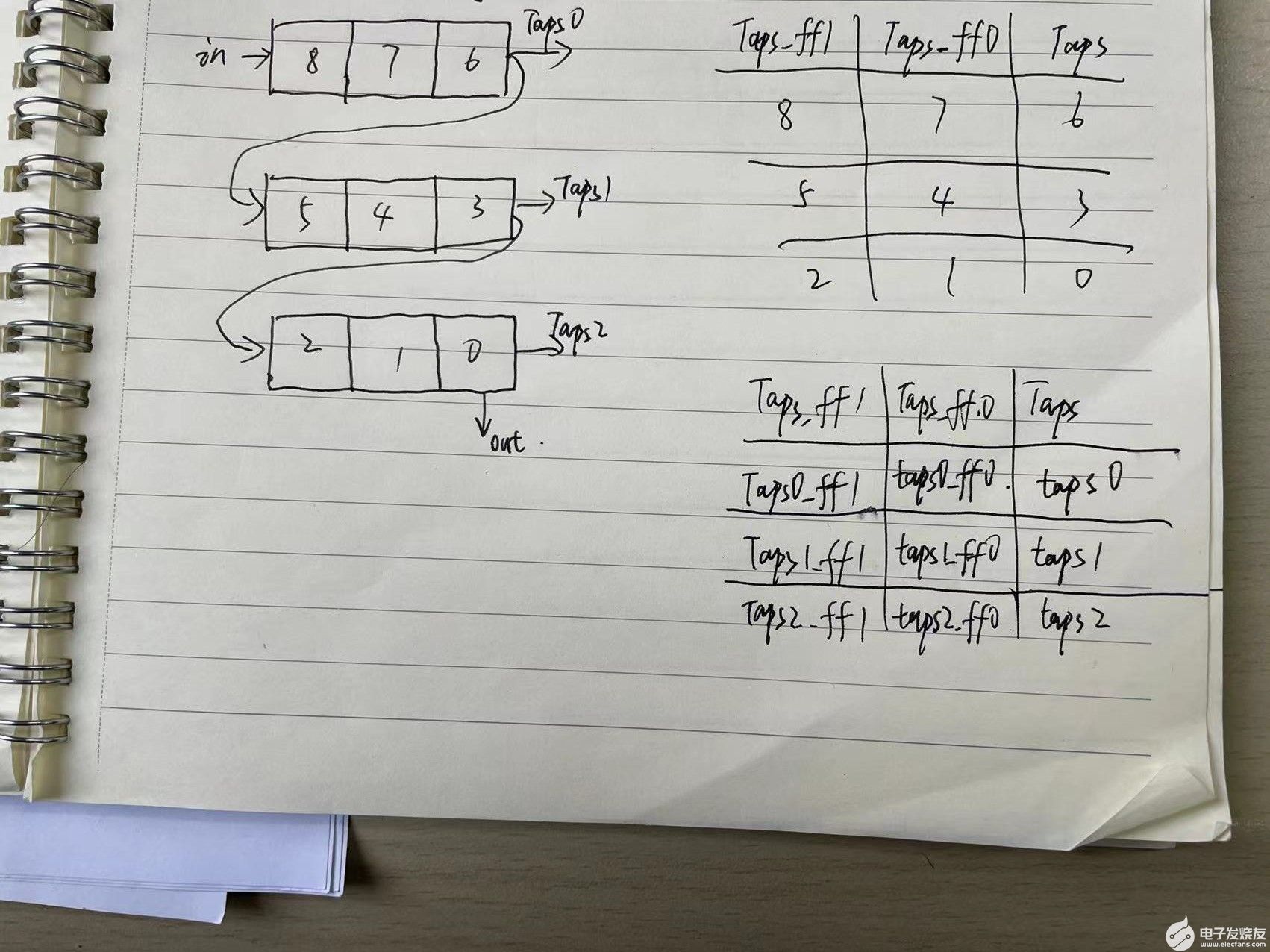

【问题6.9】这个关系怎么得到的呢?根据这个图的话 上面的关系不应该反过来吗?在下一拍的时候应该吧taps0_ff0赋值给taps0x呀?

答:没有 ff0就是表示 延时一拍的意思,taps0_ff是taps0前一时刻的值,需要得到这种结果,就是通过时序逻辑打一拍,资料提供的有直播课讲解,建议结合仿真波形去看,测试文件有提供

【问题6.10】请问这一段写在代码的哪里?我找不到,看不出

答:在SCCB代码里

审核编辑:汤梓红

-

Keystone NDK常见问题解答2024-10-11 341

-

TFPxxx常见问题解答2024-09-29 356

-

关于UCC25640x LLC谐振控制器的常见问题解答2024-09-04 369

-

CLOCK常见问题解答2023-11-23 473

-

CAN总线常见问题解答2021-12-27 2449

-

关于protel 99se的60个问题解答资源下载2021-04-13 1037

-

晶闸管实用技术问题解答2017-09-12 1023

-

示波器使用者的六大常见问题解答2016-10-10 815

-

广州大彩串口屏技术文档—关于显示类问题解答2016-07-01 951

-

PC 音质常见问题解答2010-08-02 609

-

新手-iPhone/touch常见问题解答2010-02-02 556

-

惠普公司关于内存更换的问题解答2010-01-26 837

-

CCS问题解答2009-08-03 967

-

VxWorks常见问题解答2009-03-28 563

全部0条评论

快来发表一下你的评论吧 !