事务级建模使IP加速

描述

由于对更多功能、设备移动性和改进可用性的需求不断增加,片上系统 (SoC) 开发成本继续快速增长。这些新功能需要在多核硬件和其他专用加速器上执行更复杂的软件,以满足功率和性能要求。设计团队的生产力没有跟上复杂性的增长,导致开发时间延长。由于这个和其他因素,复杂 SoC 的开发成本接近 1 亿美元,要求公司销售数千万个单元才能从该投资中获得利润。

开发和集成低层硬件依赖软件的任务通常处于系统项目的关键路径上,并且具有降低项目成本的最大潜力。问题在于,软件开发通常要等到详细且经过验证的硬件模型可用后才能开始,即使这些模型也可能无法完全满足系统要求。软件/硬件集成发生在项目结束时,此时更改成本高昂且实施时间长。修复通常仅限于软件,导致硬件欠佳或忽略关键功能。

硬件和软件及其交互的功能验证是系统项目关键路径上的另一项任务。SoC 和软件中不断增加的功能范围正在提高设计复杂性,并以指数方式推高功能验证成本。此外,大多数当前的设计流程将设计捕获为寄存器传输级别 (RTL) 描述,这是一种较为详细的格式,使得更改难以实施且验证速度较慢。许多错误是在计划结束时发现的,需要昂贵的迭代来修复和重新验证系统。

业界越来越支持使用事务级建模 (TLM) 作为并行硬件和软件开发以及加快从设计到芯片的路径的一种方式。尽管业界对 TLM 产生了广泛的兴趣,但使用 TLM 开发真正可互操作的 IP 的标准方法的创建却因不同的方法而停滞不前。克服差异并为 SoC IP 互操作性定义统一的方法可以解决硬件和软件之间更紧密相互依赖的新现实,从而使半导体公司能够显着降低风险和成本。

IP 创建的自动化方法

硬件虚拟原型和高级综合为系统设计提供了显着的优势,但由于它们使用不同的硬件模型,它们在很大程度上仍然是脱节的。为虚拟原型设计、IP 综合和功能验证创建单个 TLM 模型可以消除模型不同时可能出现的重复工作和软件质量问题。

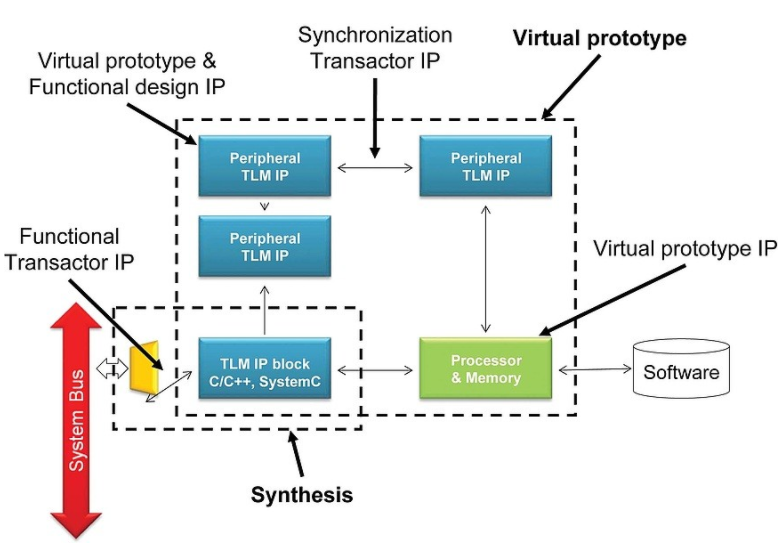

虚拟原型将专用处理器模型与设计 IP 的 TLM 模型相结合,为开发依赖于硬件的软件驱动程序提供了一个平台(如图 1 所示)。TLM IP 模型提供了硬件的准确表示,并作为 RTL 高级综合的单一来源。

图 1:虚拟原型通过将专用处理器模型与设计 IP 的 TLM 模型相结合,为开发依赖于硬件的软件驱动程序提供了一个平台。

高级综合作为一种使能技术已经成熟,现在可以支持大多数常见的硬件结构,使得使用 TLM 作为“黄金来源”开发整个 SoC 成为可能。更少的源代码行与更少的错误相关。更高抽象级别的仿真速度更快,因此功能验证计划更短,这意味着在项目中更早地发现了错误。

此外,可以为 TLM 和 RTL 构建一个单一的、可重复使用的功能验证环境。这降低了重用 IP 的成本,因为高级综合工具可以将 TLM 描述映射到新架构。此外,自动集成工程变更单的高级综合工具可以快速实施后期错误修复或较小的需求变更。

在将系统约束与高级逻辑设计源代码完全分离后,可以通过更改综合约束将 IP 重新用于新架构。抽象和自动化增加了创建逻辑的工程师的生产力。然而,高级综合的全部优势无法通过仅生成 RTL 并使用当前 RTL-to-GDSII 流程的流程来实现。TLM 实施流程必须优化整个过程,从读取 TLM 到生成结果布局。

功能验证需要一种自动化方法来探索设计的极端情况行为并提高验证工程师的工作效率,因为他们指定了范围广泛的系统操作条件。开放式验证方法 (OVM) 是适用于 TLM 和 RTL 设计的行业标准验证方法。利用 OVM,设计团队可以定义一种验证方法,最大限度地减少将验证环境从 TLM 迁移到 RTL 所需的工作量,并在整个过程中重用代码。衡量设计功能行为的指标可以将验证工作集中在那些尚未观察到的系统行为上,而不是重复以前的覆盖范围。

为了实现所有这些优势,需要一种新的 IP 建模方法来统一早期的软件开发和硬件设计。该方法必须能够创建支持早期软件开发、功能验证和高级综合的 TLM 模型,同时与现有的 RTL 方法基础设施集成。单个模型减少了工作量以及编码过程中引入的错误。随着这种方法得到更广泛的采用,它定义了在整个企业内重用 IP 并改变第三方 IP 生态系统的新机会。

新的 TLM IP 类别

基于 TLM 的虚拟原型设计、综合和功能验证解决方案的出现将定义一组新的 IP 类别。每个类别都是整体设计流程的一部分,并为公司和第三方 IP 业务的可重用性提供了机会。统一的方法必须包含以下所有 IP 类型,以实现完整的 TLM 解决方案:

功能设计 IP:计算(不是接口或总线)逻辑,通常用于综合

虚拟原型 IP:用于开发软件的计算(不是接口或总线)逻辑

综合约束 IP:综合工具的面积、时序、功耗和其他指南

SoC 估计 IP:芯片级估计的面积、时序和功率表征

功能性交易商 IP:用于虚拟原型和综合的引脚级模型的总线或接口

同步交易者 IP:两个 IP 块之间通信的可综合模型

验证 IP:模拟外部驱动程序、检查正确性和测量完整性的代码

验证计划:验证阶段和衡量成功完成的指标

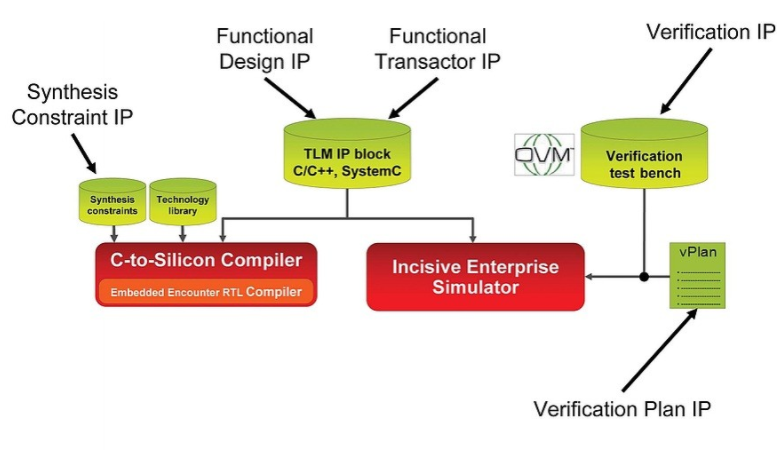

行业知识产权趋势

作为第一个关键步骤,业界正在对 TLM 进行标准化,使用 SystemC 来表示系统硬件并实现虚拟原型模型开发的广泛采用。其他新兴标准使用 TLM 对旨在用于综合的硬件进行建模,并使用标准来定义可重复使用的测试平台,以便跨多个抽象级别进行功能验证。目标是协调所有这些方法和 IP 类型,并支持创建支持早期硬件和软件开发以及更高生产率的系统集成和验证的单一硬件模型(如图 2 所示)。

图 2:单个硬件模型必须结合标准化方法和 IP 类型,以支持跨多个抽象级别的功能验证。

IP 可重用性是统一方法的主要驱动力。多年前,RTL 重用的统一定义扩大了公司围绕 IP 组建的机会。对于 TLM IP,IP 重用的目标是 RTL IP 重用的超集。IP 需要支持用于早期软件开发的事务级虚拟原型,使用高级综合来探索不同架构的高生产力设计流程,以及 TLM 和集成 TLM IP 的 SoC 的高级功能验证。

爆炸式增长的系统开发成本和缩短的时间表正在推动行业采用 TLM,这是一种新的抽象级别,可以实现更早的软件开发和更高效的硬件设计和实施。向这种新抽象的过渡将通过提供新功能和降低维护成本来加强 IP 行业。TLM 应该被视为一个为 IP 产品增加更高价值的机会。

审核编辑:郭婷

-

ESL设计的核心——事务级建模介绍2023-11-02 2975

-

Arasan发布无缝集成CANsec加速器IP的CAN-XL IP2023-08-04 1657

-

验证IP用户的期望:事务建模2023-05-29 1007

-

基于Verilog的开关级建模2023-03-30 2757

-

有什么方法可以进行IP开发及FPGA建模?2021-04-29 1074

-

什么是IP开发及FPGA建模?2019-08-01 5575

-

双11同款!阿里云发布全局事务服务GTS:每秒处理10万笔事务2018-06-05 1850

-

IP:网级协议2016-05-09 718

-

TCP-IP详解卷3:TCP事务协议,HTTP,NNTP和UNI2015-10-27 602

-

MEMS系统级的跨平台建模技术研究2011-08-23 513

-

TCP/IP详解,卷3:tcp事务协议等(pdf电子书)2009-08-06 1960

-

基于SystemC事务级的建模仿真研究2009-07-30 1085

-

《TCP-IP详解_卷3_TCP事务协议,HTTP,NNTP2006-03-24 1035

全部0条评论

快来发表一下你的评论吧 !