无线SoC设计中RF布局的最佳实践

描述

无线连接与微控制器 (MCU) 的片上系统 (SoC) 集成是整个物联网 (IoT) 中连接设备应用的支持技术。最新的无线 SoC 设备加速了高性能网络的开发,使紧凑、低功耗和具有成本效益的系统设计能够在更短的时间内投放市场。无论是可穿戴设备和智能手机之间的蓝牙连接,还是使用 ZigBee 或 Thread 作为通信协议的智能家居应用,底层技术都依赖于以高达 2.4 GHz 的频率传输和接收射频 (RF) 信号。最大化任何无线连接的性能意味着密切关注射频电路设计,尤其是电路板布局。

无线设计可能具有挑战性,因为所需的射频信号通常与不需要的射频信号非常接近,例如 MCU 时钟或开关电源产生的高频信号。因此,由不良设计实现的通信范围可能会受到损害,或者需要更高的发射功率水平来补偿,这将导致便携式设备的电池寿命缩短。更高功率的信号还会产生杂散信号,可能会对其他设备造成干扰,无法满足标准监管要求。

由于这些原因,了解有效无线通信的设计目标、电路布局如何影响这些目标以及最重要的是如何通过遵循一些简单的最佳实践从设计中提取最大射频性能是很有帮助的。我们将参考 Silicon Labs 的 EFR32 Wireless Gecko SoC 的特定电路板布局来探索这些。

影响射频性能的因素

无线设备的射频性能主要取决于印刷电路板 (PCB) 射频部分的设计和布局。匹配网络中 RF 组件的位置,就其方向和与其他组件的分离而言,会对不需要的信号的耦合产生重大影响。RF 走线的布线和尺寸与设计中使用的天线的选择同样重要。此外,接地金属化、非射频走线(尤其是电源线)的布线以及 PCB 本身的性质(如板厚、介电常数和层数)等因素都在整体设计。安装在板上的其他组件,包括 MCU 时钟电路和电源转换器,可能会在射频频谱中产生过多的杂散,从而导致灵敏度下降。因此,采用适当的滤波将高频信号与这些源隔离并防止它们到达射频路径非常重要。

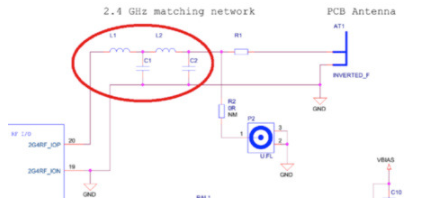

为了更好地理解如何完成这种滤波,我们首先需要了解射频电路的功能。IC内的无线电包括发射器和接收器。发射器 (Tx) 的目标是将尽可能多的有用信号驱动到天线中。在 RF IC 和负载之间使用阻抗变换旨在最大限度地提高基频的辐射功率,并最大限度地减少谐波和其他杂散频率的任何耗散损耗。这是通过由串联电感器和并联电容器组成的组合匹配和滤波网络来实现的。对于在 2.4 GHz 下以高于 13 dBm 的 Tx 功率水平运行,建议使用如图 1 所示的 4 元素梯形图。当以较低功率运行时,2 元件 LC 网络可能就足够了。在接收模式下,

【图1 | 用于 2.4 GHz 的四元发射机匹配网络]

布置 RF 部分时的注意事项

虽然无线 SoC 供应商提供的参考设计旨在提供最佳的射频性能,但由于尺寸或形状因素的限制,并不总是可以将这种设计照原样复制到终端系统设计中。显然,与参考设计的任何偏差都会影响性能。在涉及的高频下,由于电路板走线长度不同,元件之间距离的变化会引入寄生电感。不同的基板厚度或介电常数,或迹线之间的间隙,可能会引入寄生电容。改变组件相对于彼此的间距或方向会影响信号耦合,而改变推荐的组件类型或尺寸也会引入不同的组件寄生效应。

糟糕的设计选择会导致匹配和滤波网络失谐,也可能导致晶体负载失谐。这样做的可能后果是 Tx 输出功率降低、Rx 灵敏度降低、杂散发射水平增加、电流消耗增加以及不同板之间可能出现频率偏移,所有这些都可以在传导和传导和辐射信号测量。

此外,问题不一定局限于电路板的射频部分。从射频辐射的角度来看,必须考虑整个 PCB 设计,因为接地层及其尺寸等因素会影响发射信号的功率,尤其是在使用单极型天线时。接地层的屏蔽效应也会影响辐射杂散的水平,非射频走线也会如此,因此必须注意确保这些都很好地保持在 EMC 限制范围内。还应该理解,即使是按原样使用的参考设计也不是完整的应用程序,对于参考设计区域之外的板上的其他电路,也应该采取类似的谨慎措施。

遵循 RF 部分的最佳布局实践

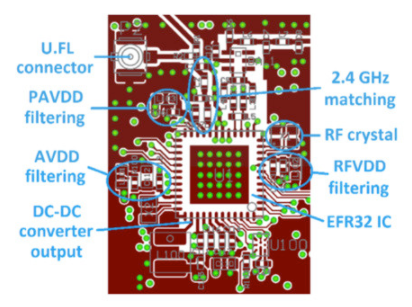

当无法完全按原样实施参考设计时,遵循一些指导原则是值得的。图 2 显示了 2.4 GHz 无线电板布局的示例指南。

从匹配网络开始,第一个组件应尽可能靠近 RF IC 的 Tx 输出引脚放置,以减少因扩展信号走线的寄生电感而产生的失谐效应。其余匹配网络组件应彼此靠近放置,以最大限度地减少任何 PCB 对地寄生电容或组件之间的进一步走线寄生电感。理想情况下,用于连接这些组件的走线宽度应与焊盘宽度相同,对于 0402 尺寸的 SMD 组件,该宽度通常为 0.5 mm。

【图2 | 显示关键电路区域的 2.4 GHz EFR32 无线电板布局]

在所有电源引脚上正确放置去耦电容至关重要。最低值的旁路电容器会滤除基本 Tx/Rx 频率附近的信号,并且需要放置在最靠近 IC 引脚的位置,并使用多个通孔连接到接地层,并具有良好的接地。值约为 100 nF 的旁路电容器将抑制数十兆赫兹范围内的时钟信号,否则这些时钟信号可能会在芯片内上变频,从而在载波频率周围产生不需要的杂散。最大值电容器旨在滤除来自开关电源的干扰,该干扰通常约为数百千赫。这些可以放置在离电源引脚更远的地方,显然在电池供电设备的情况下不需要。

晶体应尽可能靠近 RF IC 放置,以确保最小化过孔寄生电容并减少任何频率偏移。晶体的外壳应使用多个过孔连接到地,以避免来自未接地部件的辐射,因为任何未连接和浮动的金属都可能充当不需要的辐射器。在晶振和 VDD 走线之间使用隔离接地金属将避免由电源对晶振造成的任何失谐效应,并且同样可以避免晶振或时钟信号及其谐波泄漏到电源线。

良好的接地连接至关重要,并且有许多与这种做法相关的建议。电容器接地引脚附近的走线应加厚,以提高散热带的接地效果(用于冷却)并最大限度地减少接地之间的串联寄生电感(电路板的未使用区域填充有接地的铜)和接地引脚。靠近电容器接地引脚并连接到底层或内层接地层的额外过孔将进一步有助于减少这些影响。

RF IC 焊盘的裸露焊盘占位面积应使用多个过孔,以确保良好的接地以及良好的散热能力。在图 2 所示的布局中,7 mm x 7 mm 尺寸的 IC 封装有 25 个通孔,每个通孔直径为 0.25 mm。如果可能,焊盘接地应连接到顶层接地金属,以进一步改善射频接地。这可以通过通过 IC 封装角落的对角迹线连接来实现。信号,尤其是高频谐波,有时会耦合在附近滤波电容器的接地连接之间。通过将这些电容器连接到传输线两侧的地,可以避免问题。

在匹配网络区域,建议确保走线或焊盘与相邻接地浇注之间的距离至少为 0.5 mm。这将最大限度地减少任何寄生电容并减少失谐效应。对于 4 层 PCB,顶层下方的第一个内层应在 RF IC 和匹配网络下方填充连续的接地金属。这种技术将确保到 RF IC 接地的良好低阻抗信号路径,并且通过不在该区域放置任何布线,将防止与匹配网络的任何耦合效应。还建议不要以任何方式阻塞 Tx/Rx 匹配网络的接地过孔和 RF IC 焊盘的接地过孔之间的接地返回路径。返回电流应该有一条清晰、畅通无阻的路径,通过接地层返回 RF IC。

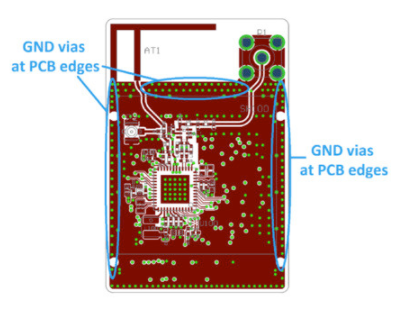

最后,关于射频部分,应使用 50 欧姆接地共面传输线连接到远处的射频组件,例如板载天线或天线连接器。这将降低对 PCB 引起的任何信号变化的敏感度,还将减少不需要的辐射和耦合效应。耦合器线附近的多个接地通孔可以进一步减少辐射。传输线的使用如图 3 所示。

整个 PCB 的最佳实践布局设计

虽然作为最低要求,最好在 PCB 的 RF 部分区域周围有一个大的连续接地金属化,但通过将这种技术应用于整个 PCB 可以获得更好的性能。为了实现良好的射频接地,整个接地区域的射频电压电位应相等。这有助于保持适当的 VDD 滤波,并为单极型天线提供良好的接地层。间隙应该用接地金属填充,顶层和底层的结果部分应该用尽可能多的过孔连接。

为了减少边缘场引起的谐波辐射,应在任何接地金属区域的边缘部署多个接地通孔,尤其是在 PCB 边缘和电源走线周围,如图 3 所示。在具有两个以上的电路板设计中层,所有的导线或走线都应放置在内层之一中,尤其是电源走线,并且整个顶层和底层应包含尽可能多的连续接地金属化,以减少来自这些走线的任何辐射。还建议避免将电源走线放置在靠近 PCB 边缘的位置。

【图3 | 显示传输线和 PCB 边缘接地过孔的整个电路板布局]

结论

我们都欣赏无线连接的好处,无论是在我们的消费技术小工具与我们的智能手机、平板电脑和笔记本电脑之间,还是在不断发展的物联网的更广泛领域中。这一承诺的实现取决于将各种“东西”连接在一起并连接到互联网,其中许多需要在合理距离内进行无线通信,同时在电池必须更换或充电之前长时间运行。

实现物联网的承诺还需要可靠、经济高效的连接解决方案,该解决方案基于可轻松集成到最终产品设计中的无线 SoC。然而,RF 设计从来都不是一件容易的事,从 RF 电路布局中获得最佳性能可能具有挑战性。使用无线 SoC 供应商的参考设计可能是一个不错的方法,但有时这是不可能的。遵循良好的 RF 设计实践始终很重要,以确保满足通信范围和功耗的目标,而不会产生不必要的干扰问题和不符合监管标准要求。

审核编辑:郭婷

-

2.4 GHz RF SoC的音频应用:从原理到实践2026-01-06 650

-

TMCS110x 布局挑战和最佳实践2024-09-12 428

-

电机驱动器电路板布局的最佳实践2024-09-05 1467

-

SoC布局中各种IC简介2024-07-17 1411

-

加快部署 5G 基站的最佳实践:RF 前端大规模 MIMO 入门2022-12-26 2929

-

网格着色器的最佳实践2022-04-01 2228

-

什么是FPGA、AD9371、AD9009、RF SOC2021-07-27 1183

-

天线设计和射频布局指南资料免费下载2020-11-20 1600

-

七种PCB布局最佳实践2020-11-05 2783

-

怎样进行RF和混合信号PCB的布局2020-10-13 931

-

采用RFMD的无线SoC RF6505 / 6575/6555的参考设计2020-05-27 2116

-

Dockerfile的最佳实践2019-07-11 1539

-

最佳天线实践、布局指南以及天线调试程序2019-05-21 3428

-

RF和混合信号PCB布局最佳指南(专家应用笔记)2018-03-15 17303

全部0条评论

快来发表一下你的评论吧 !