基于Xilinx KV26的立体视觉匹配方案

描述

PhiGent Heimdallr - 基于Xilinx KV26的立体视觉匹配方案

概要:

立体视觉匹配的目标是从不同视点图像中找到匹配的对应点,最终输出RGBD的深度图像。

在本文中,我们将首先对基于AI 的双目立体匹配算法进行介绍,接着会对本方案中使用的 Xilinx Vitis AI Tools 和 Xilinx Vitis Flow 开发流程进行介绍。

目标及原因:

深度估算是自动驾驶领域的一项关键技术。作为自动驾驶中最常用的传感器,摄像头能够获取全面、丰富又密集的信息。基于立体视觉的深度估算技术可以准确识别和定位运动与静止目标以及路面对象。随着深度学习技术的迅猛发展以及大规模立体数据集的问世,基于神经网络的立体视觉匹配算法得以快速发展,计算精度与效率均超过了传统算法。借助强大的特征提取功能,基于深度学习的端到端双目立体匹配技术能确保具有弱纹理和重复纹理的对象仍然可以输出有效的高精度深度信息,从而满足智能驾驶系统在各种场景下的感测需求。

本方案使用了最新的基于卷积神经网络的立体视觉匹配算法,并通过Xilinx VitisAI 工具包,将该算法中的卷积网络部分部署至赛灵思深度学习处理器(DPU)上进行加速。同时,算法中无法使用 DPU 加速的部分,如相关层操作则使用了专用的定制IP 进行加速。除此之外,本方案还定制了专用的图像预处理 IP 用来进行输入图像的预处理操作。

本方案可以部署至赛灵思 KV260 开发板或者基于 KV26 核心板的专用定制开发板Heimdallr-DEB。

基于 KV260 开发的方案由于受限于双目立体视觉模组的硬件接口限制,仅能使用数据回灌方式验证深度估计效果。基于本方案定制的 Heimdallr-DEB 开发板方案则能使用配套的双目立体视觉模组,将本方案部署至汽车上,在车辆行驶过程中实时展示立体匹配效果。

技术方案介绍

本方案将从以下几个部分进行介绍:

模型的选择及调优;

FPGA PL侧开发流程;

软件配套程序开发;

方案部署及运行。

1

模型的创建及调优

模型选择:

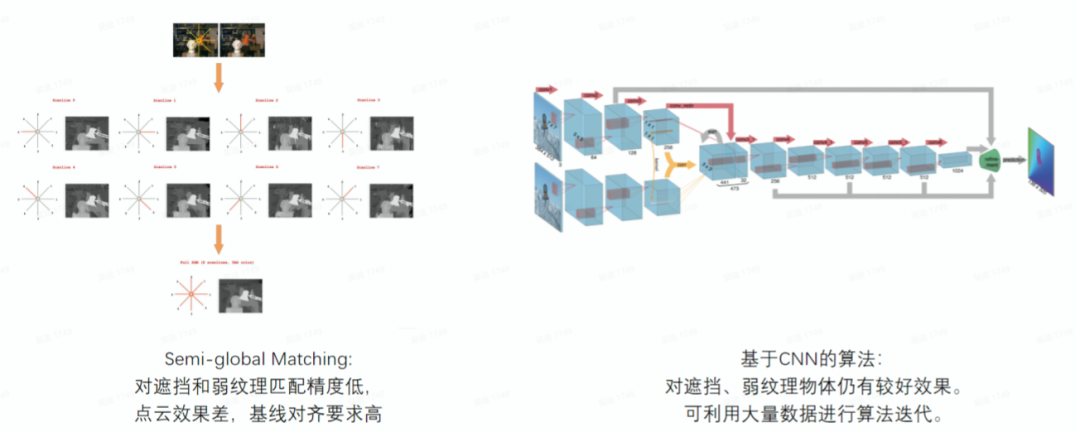

基于神经网络的双目立体视觉方案首先需要选定算法。在深度学习大火之前,研究者们都使用基于规则的方法去进行视差匹配,这些典型的传统算法有:SGM,SGBM等。在卷积神经网络迅速发展后,有大量学者使用基于 CNN 的方法进行立体视觉匹配算法的研究。目前,根据在 Kitti 2015 测试数据集上准确率较高的几种 CNN 算法,有 Raft-Stereo, GA-Net, FADNet 等。基于神经网络的匹配算法在遮挡、弱纹理区域仍能获得非常好的效果,同时可以利用持续更新的数据集对算法进行迭代。

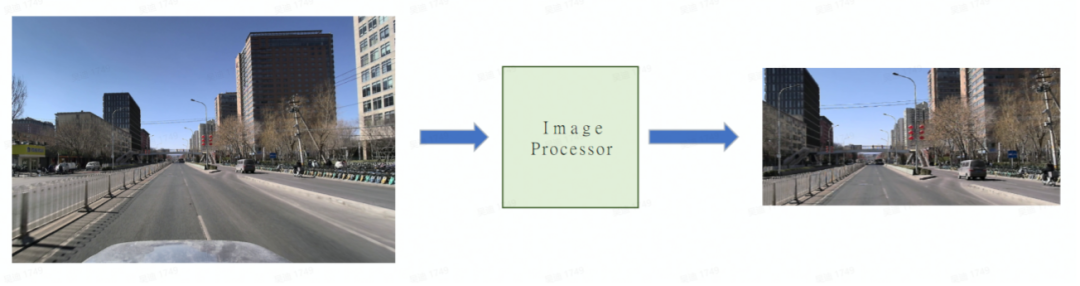

图1:传统匹配算法与基于CNN匹配算法的对比

但同时,这些基于神经网络的算法或者计算量太大,或者使用了特殊的操作导致不适合部署到 FPGA 上实现。我们针对 FPGA 器件的特点,为充分利用 FPGA 的计算特性,提高计算效率,结合了几种主流神经网络算法的特点,创造出适合部署在 FPGA 器件上的网络模型 PhiFADNet - PhiGent Fast and Accurate Disparity Network。PhiFADNet 计算量小,网络结构简单但保留了双目神经网络算法中最重要的 correlation 层,使得该算法在低算力的同时还能报错不错的准确率。

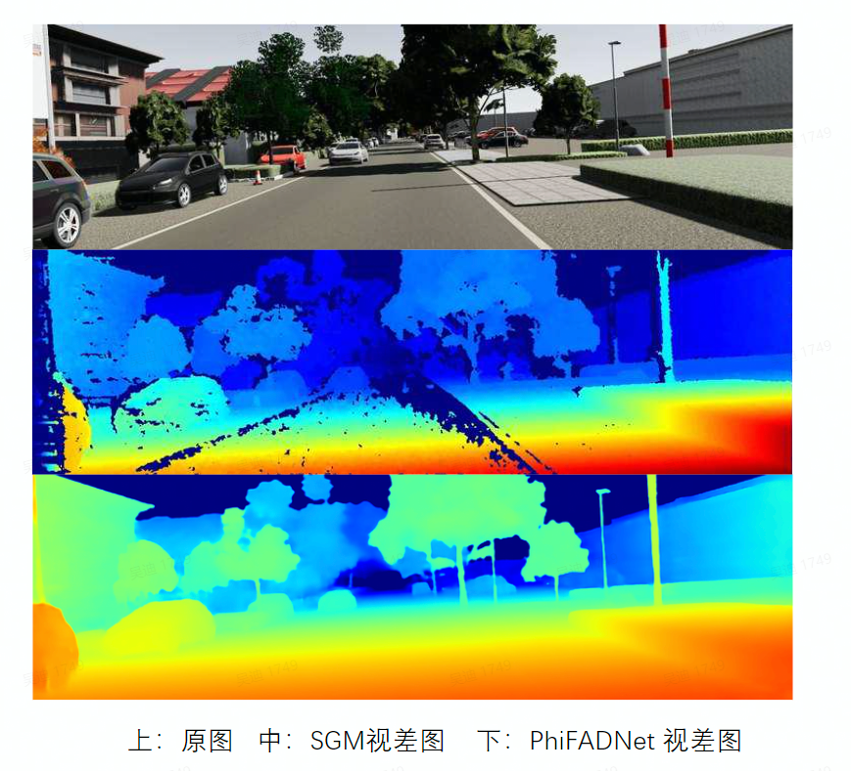

我们挑选了 Kitti 数据集中公开的一张图片,并分别使用了SGM 和 PhiFADNet 进行视差匹配,发现使用 PhiFADNet 的视差结果,在地面等弱纹理区域有更好的连续视差结果,同时在细小物体出的检测更加准确,整体的视差图噪声和飞点较少。

图:SGM与 PhiFADNet 视差图对比

模型量化和编译:

Xilinx Vitis AI 提供了整套的工具用来对用户自定义网络进行 裁剪、量化和训练。Vitis AI 软件可作为 Docker 镜像使用并且可从 Docker hub (xilinx/vitis-ai Tags | Docker Hub)下载。Vitis AI 用户指南(Vitis AI User Guide)则提供了详细的分步说明。我们使用 Xilinx Vitis AI Tools 对这三个网络进行 Quantization-aware training (QAT). Xilinx Vitis AI Tools 包括AI Optimizer, AI Quantizer, AI Compiler和 AI Profiler。

模型测试效果:

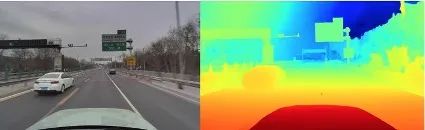

我们使用双目模组在实车高速公路场景上采集了大量数据并进行了训练,训练后的模型效果在实际场景中的表现如下。

图:PhiFADNet 实车路段视差图展示

2

FPGA PL 侧开发

Correlation Accelerator:

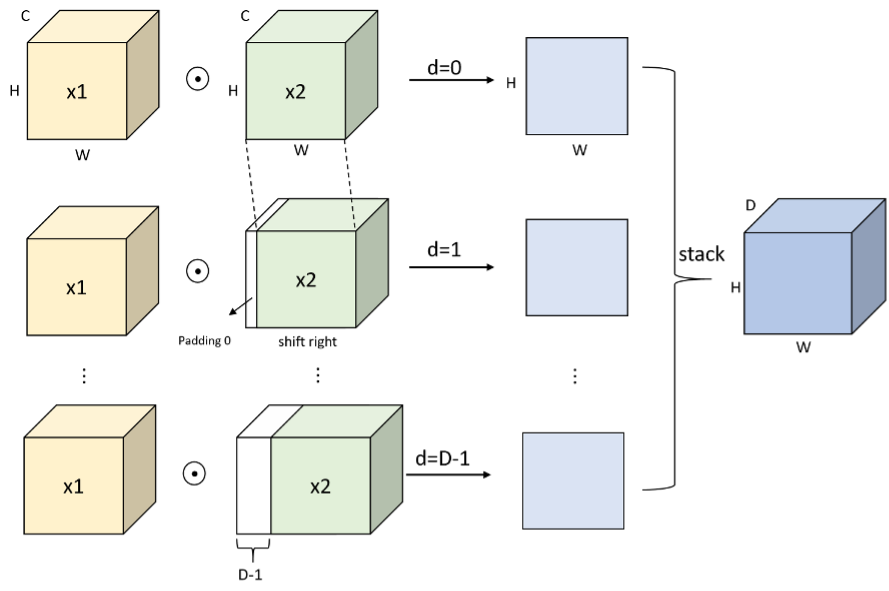

FADNet 结构中的相关层操作-correlation 并不能直接部署到 Xilinx DPU上,因此我们需要单独把 correlation 操作提取出来进行运算。根据测试结果,如果使用 ZU5 芯片上的 4核 ARM-A53 进行correlation操作,共耗时80ms,而整个神经网络其他部分使用DPU 运行的时间加起来也就80ms。使用 ARM 完成 correlation极大的增加了整个网络的延时,而自动驾驶场景对延时有着严格的要求。因此我们考虑使用 FPGA 对 correlation 进行操作。

根据 correlation 操作的特点,我们定制化了一个专用 Correlation Accelerator IP 对其进行加速。由于 correlation操作的输入和输出都需要连接至 DPU,因此我们需要对改操作进行定点化操作,并支持 PS 进行 shift 移位配置。使用 FPGA 进行加速后的 Correlation 操作能获得相比与 PS 处理时间 20倍的加速比。加速后的 Correlation 操作能极大的缩短双目立体视觉的匹配延时。

比较典型的 correlation 操作示意图如下图所示:

图:Correlation 流程示例图

图像前处理:

无论是基于传统算法或者神经网络的双目立体匹配系统,对图像前处理都有着较高的要求。图像前处理通常包括 ISP、畸变矫正、极线对齐、图像下采样等。

ISP模块我们使用模组自带的 ISP 芯片或者开发板上的 ISP 处理芯片完成图像信号处理。

畸变矫正和极线对齐处理,我们可以通过标定获取双目摄像头模组的内外参数并获得矫正矩阵,通过该矫正矩阵可以同时完成图像的畸变矫正和极线对齐。由于该操作主要是将图像数据根据矫正矩阵进行重拍,使用PS 端 ARM 处理器进行该操作可以获得较高的效率,同时节省部分 PL 资源。

最后在图像输入神经网络处理前,我们需要对矫正对齐后的图像进行下采样处理。下采样处理的主要目的是去除左右图像中的无视差区域以及部分非感兴趣区域(如:自动驾驶中的天空区域),下采样后的图像尺寸为神经网络的输入尺寸。我们使用 FPGA PL 部分来对该下采样操作进行加速。加速后的下采样操作针对单幅 2M pixel 图像的处理时间缩减为 7ms,而使用 PS 部分进行该操作需要大概28ms。

图像前处理的作用:去除图像中的无视差区域;剔除图像中的非感兴趣区域(天空,车头等);根据网络尺寸动态调整输入大小。

图:图像前处理剔除非感兴趣区域

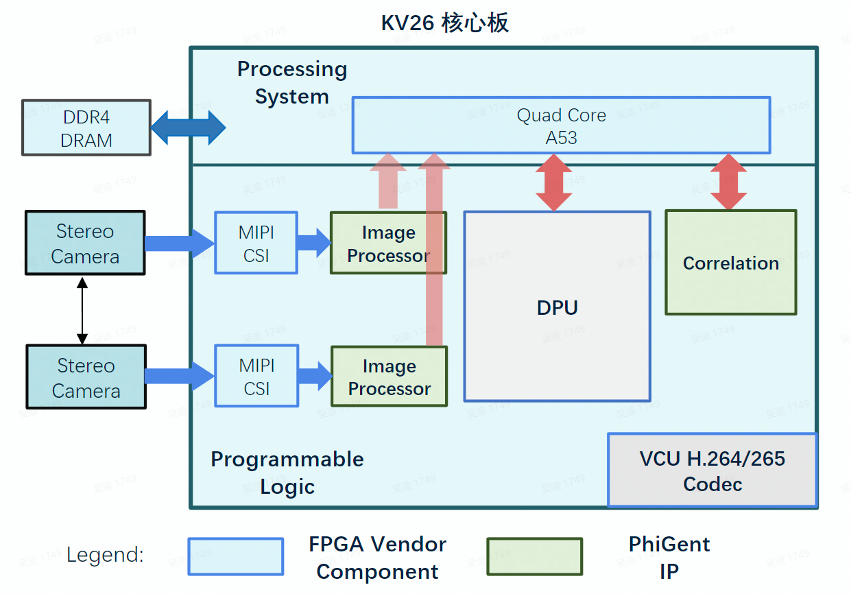

整体FPGA设计框架:

根据前文描述,整体FPGA设计框架包括双目图像前处理模块(Image Processing),神经网络加速器模块(Xilinx DPU), 相关层加速模块(Correlation IP)。本方案使用PS和PL协同工作,PS部分主要负责图像校正对齐,数据调度,流程控制等。整个方案运行时,PS和PL的使用率都能达到80%以上,同时通过流水线并行处理使得整个系统能获得最优的吞吐率。整个 FPGA 的设计框架如下所示:

图:基于kv26核心板的 FPGA 设计框架

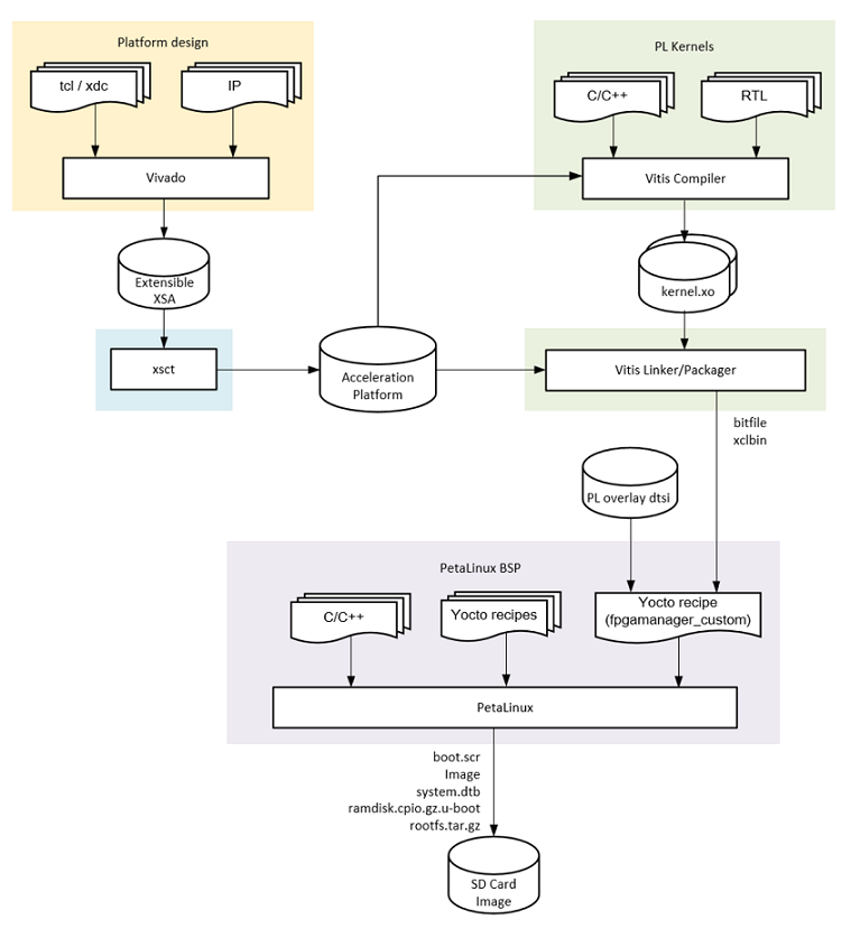

FPGA工程制作:

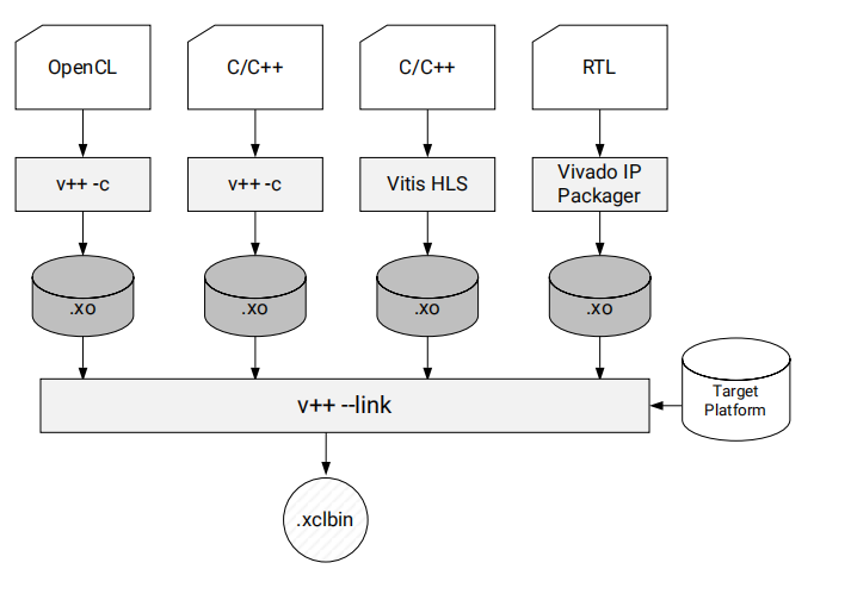

本方案使用 Xilinx Vitis Flow 完成整个 FPGA 工程的开发流程。整个 Vitis Flow 的开发流程如下图所示(注:开发环境需要安装有 Vivado 2021.1 和 Vitis 2021.1):

图:Vitis Flow 开发流程示意图

Vitis Platform Flow:

首先我们需要制作开发板对应的 platform。本方案提供了两套实现方案,分别是基于 Xilinx KV260 开发板和 Phigent Heimdallr-DEB 开发板。两套开发板的核心板都为 K26 SOM 核心板,仅在外围的 GMSL 接口上有主要不同(Phigent Heimdallr-DEB 可以接入 Phigent 定制化双目模组)。因此两套方案可以使用相同的 Vitis Platform。

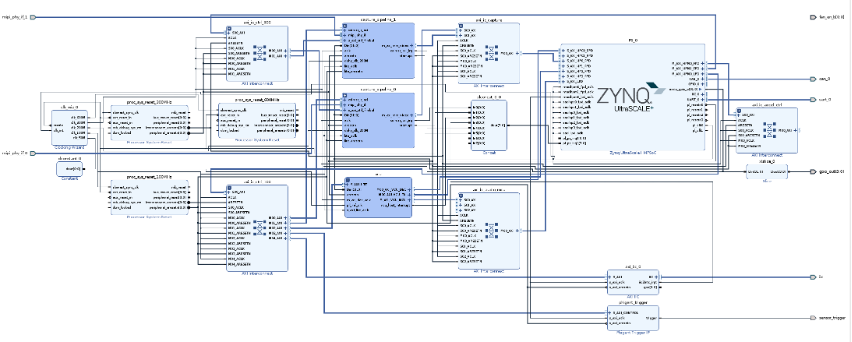

Vitis Platform Flow 首先需要使用 Vivado 生成定制化的 PL design。我们选定工程的芯片型号为 K26 SOM,然后在 vivado block design 中添加本方案需要的 platform 组件,包括 Xilinx MIPI RX Controller,VCU,Phigent Image Processor 和配套的 interconnect 等。整个 platform 的 block design 设计概览如下图所示。完成 Platform 的设计后,使用 Vivado 工具生成 .xsa 文件,该文件在后续配套的 petalinux 工程中还会进一步使用。

图:使用 Vivado 生成 Block Design

生成 .xsa 文件后,使用 vitis 提供的 xsct 命令生成 pfm 文件,该文件会在后续用于集成 HLS/RTL kernel 并生成最后的 xclbin。

PL kernels:

Vitis Flow 将 FPGA 工程分成了 platform 和 PL kernels 两个部分。其中 Platform 中用于配置工程中需要的基础功能 IP、硬件接口、硬核/软核设备等。PL kernels 为用户自定义生成的一些加速IP,如本方案中使用 correlation IP 和 Xilinx DPU 均属于 PL kernels。

开发完 Correlation IP 后,我们需要使用 Vitis Compiler 将 RTL kernel 编译成可集成进Vitis Flow 的 kernel.xo 文件。Xilinx DPU 在官方 kv260 例程中有提供生成 kernel.xo 的流程,参考链接为:https://github.com/Xilinx/kv260-vitis。

Device Build Process

图:Vitis Linker 链接 Platform 和 PL Kernels

准备好 Target Platform 和 PL kernels 后,最后使用 vitis V++ 命令将 Platform 和 PL kernel 链接起来并生成最后的 .xclbin 文件。

本方案中使用的整个Vitis Flow 流程可以参考:

https://github.com/PhigentRobotics/Phigent_Heimdallr

在该 git repository 中,已通过自动化脚本将整个 vitis flow 全部打包完成,用户使用 make overlay OVERLAY=heimdallr 命令后就能自动跑完整个 vitis flow 流程并生成上板所需的 bit 文件和 xclbin文件。

3

软件配套程序开发

软件配套开发主要包括片上 linux 系统、 PS端应用软件、PC端应用软件的开发。

Linux 系统开发:

我们使用 Xilinx 官方提供的 petalinux 工具来为开发板量身定制 uboot、kernel、rootfs。

首先我们需要创建 petalinux工程,使用如下命令,template 参数表明创建的 petalinux 工程使用的平台模板,从k26开发板bsp文件导入。

• petalinux-create -t project xilinx-k26-starterkit-v2021.1-final.bsp -n (工程名字)

接着我们需要导入 vivado 工程中生成的bit等,利用petalinux-create创建fpga app。

• petalinux-create -t apps --template fpgamanager -n

在本方案中,我们修改的主要是 device tree 和 kernel 文件。在 FPGA工程中我们使用了定制化的 image processing IP 对图像进行前处理,所以需要配置相对应的驱动文件。使用如下命令来配置 linux 内核。

• petalinux-config -c kernel

设备树文件需要修改 petalinux 工程中生成的 dtsi 文件。在该文件中加入 image processing IP 的设备描述。

配置完成后,执行如下命令进行编译:

• petalinux-build

编译完成后使用前面生成的所有文件和 bit 文件生成 BOOT.BIN 文件。

• petalinux-package --boot --fsbl --fpga --u-boot --force

最后生成镜像文件

• petalinux-package --wic --bootfiles "ramdisk.cpio.gz.u-boot boot.scr Image system.dtb BOOT.BIN" --wic-extra-args "-c xz"

镜像文件会保存在build/images/目录下,文件名为petalinux-sdimage.wic.xz

PS应用程序开发:

由于本方案采用的是 PS 和 PL 部分协同工作的模式,PS 侧需要调度 PL 侧的 MIPI Controller、Image Processor、Correlation IP 和 DPU 来完成整个双目立体视觉方案的实施。

图像获取:

基于V4L2框架接口初始化mipi、Image Processor等,分别获取两路sensor图像,通过时间戳进行双目图像同步。

算法计算:

Xilinx Vitis AI 框架下,将左右camera图像送入模型进行推理,得到视差结果。

1. 左右图像分别做图像预处理,包括图像极线对齐,从图像中切割出感兴趣区域等。

2. 然后左右图分别送入网络提取特征。

3. 再做correlation计算后送入网络进行视差预测。

Correlation IP调用:

应用程序利用xrt运行时库与correlation ip进行交互,将运算输入数据的地址和输出数据地址设置到correlation ip寄存器,等计算完毕后将输出结果送入解码网络。

PC端应用软件开发:

PC端的应用程序需要通过网口接收来自 FPGA 开发板生成的前处理后的左右原图,以及显示最后生成的深度图。

依赖三方库

1. Grpc

2. Protobuf

3. Qt5

4. OSG (Open Scene Graph)

双目设备用户开发SDK:基于grpc、protobuf与PS侧grpc server通信,从设备获取校正后图像和视差图,经过同步后同时给到应用程序。

PC端应用程序:基于Qt5设计界面程序,使用双目设备用户开发SDK从设备获取图像和结果

4

方案部署及运行

硬件准备:

• FPGA 开发板:Xilinx KV260 或者 Phigent Heimdallr-DEB (非官方开发板,如有需要请单独联系)

• TF SD 卡 及配套的读卡器

• Micro USB 线,网线

• Ubuntu 系统 PC

• 安装有 Vivado 2021.1 和 Vitis 2021.1 的服务器

SD卡文件准备:

Git 路径:

https://github.com/PhigentRobotics/Heimdallr_software

该 git repo 包含FPGA板卡上的可执行应用程序、BOOT 文件、PC端的应用程序、BSP文件、模型等。根据 git repo 里 README的描述,将镜像文件下载至 SD 卡内。同时将 boot_fs 内的文件都放入 SD 文件夹内。

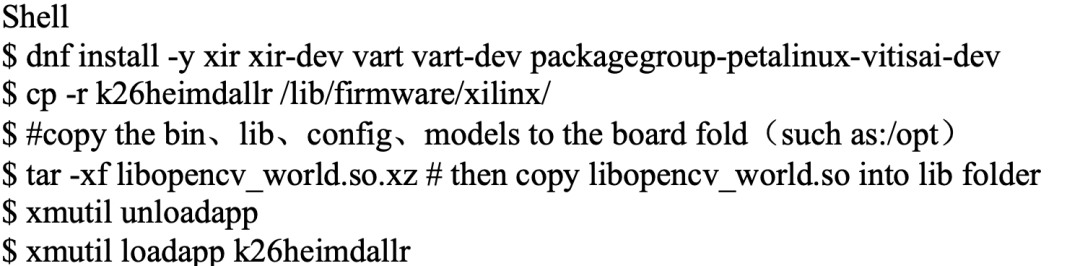

软件配置:

将 heimdallr-hmi-bin.tgz 文件解压至 Ubuntu PC 上,该应用程序用于获取左右图和最后输出的深度图的显示。

在 FPGA 的片上系统上安装 vitis ai 相关环境,将模型文件,配置文件等拷贝到相应文件夹。

程序运行:

On board(for kv260):

1.cd /opt/

2.sh bin/run_heimdallr-app_playback.sh & # kv260 development kits

On board(for heimdalr-DEB):

3.cd /opt/

4.sh bin/bin/run_heimdallr-app.sh & # Heimdallr-DEB development kits

On PC:

5. cd heimdallr-hmi-bin

6. ./AppRun.sh

审核编辑 :李倩

-

立体视觉系统的设计方案2023-11-06 480

-

双目立体视觉原理 HALCON的双目视觉系统研究2023-07-19 1241

-

Netduino上的立体视觉2022-11-08 741

-

基于Xilinx KV26的立体视觉匹配方案2022-06-01 3434

-

双目立体视觉在嵌入式中有何应用2021-12-23 1841

-

双目立体计算机视觉的立体匹配研究综述2021-04-12 1315

-

双相机立体视觉和结构光立体视觉原理及优势对比2019-05-14 9064

-

Humanplus人加为各类机器人提供立体视觉感知解决方案2018-06-07 6601

-

LABVIEW能做双目立体视觉吗2018-01-13 10105

-

图像处理基本算法-立体视觉2017-11-17 6164

-

双目立体视觉的运用2016-03-03 5483

-

基于立体视觉的变形测量2015-09-21 4694

-

双目立体视觉原理大揭秘(一)2013-11-21 3280

-

基于HALCON的双目立体视觉系统实现2011-04-08 1901

全部0条评论

快来发表一下你的评论吧 !