仿真技术嵌入式软件满足整个SoC开发周期

描述

如果有一个最大的因素推动了硬件仿真作为主要验证工具的发展,那就是片上系统 (SoC) 设计。这些设计在尺寸和功能上不断增长,需要更多的 IP 和接口。仿真技术还通过测试 SoC 设计的硬件属性并同时验证其中的嵌入式软件来满足整个 SoC 开发周期;仿真或 FPGA 原型设计工具都不能完全确保硬件/软件协同验证。

然而,事情并不总是这样。硬件仿真器在 1990 年代成为一种流行的验证工具,但当时它们是难以使用的笨重设备,需要几个月的时间来设置。而且,仿真是单用户资源,每个座位要花费数百万美元,因此只有预算大的微处理器和图形芯片公司才能买得起仿真器。

然后是可靠性差以及仿真器因运行缓慢而陷入困境的问题。对仿真器进行了彻底的改革,最终,SoC 设计运动的兴起为仿真工具提供了必要的动力,使它们更快、更便宜、更易于使用。

首先,编译流程的改进将仿真设置时间从数月缩短到数周,甚至数小时。接下来,新一代仿真引擎显着加快了设计编译周期、运行速度和调试周期时间,从而提高了整体可见性。在仿真器架构中,从昂贵的定制处理器转向更灵活的 FPGA,这使得仿真工具更加实惠。

拥有模拟器的成本已经降低,现在更多用户可以购买模拟器。此外,仿真器机箱现在可以安装在数据中心的“过道机架”内。此外,现代仿真器在编译器周期中消耗的内存更少,这进一步降低了成本并缩短了编译时间。

从 ICE 到协同仿真

硬件仿真发展的另一个重要部分是从传统的在线仿真 (ICE) 环境逐渐转变为基于事务的验证或加速等协同仿真技术。ICE 模式通常难以安装和维护,因为被测设计 (DUT) 环境映射在仿真器内部,而仿真器又通过速度适配器与芯片所在的物理系统连接。

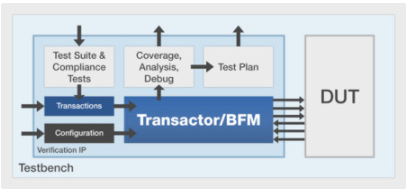

图 1. 基于事务的仿真器为 SoC 设计验证提供更灵活的测试环境。

大型多时钟 SoC 设计中功能数量的增加导致互连数量增加,这会降低仿真器速度并阻碍多个用户的远程访问。另一方面,以事务为中心的方法使用基于软件的协议接口,称为事务器。这些交易者,而不是整个 DUT 设置,被映射到仿真器内部,这不可避免地提高了验证速度。

这允许验证工程师和软件开发人员从多个位置同时访问仿真系统。此外,基于事务的验证或加速可以用更少的代码行创建更高抽象级别的测试平台,从而对抗传统 ICE 环境的不可预测性。这些测试台的执行速度比传统的 RTL 台更快。

然而,值得注意的是,在某些应用程序中仍然需要拥有硬件接口的 ICE 环境。因此,有多种仿真工具,例如 Mentor 的 Veloce 仿真平台,它提供了 ICE 和协同仿真方法的组合。

审核编辑:郭

-

嵌入式系统测试的相关资料分享2021-11-09 906

-

虚拟嵌入式设计测试环境下STM32控制器的软件仿真2021-11-03 802

-

嵌入式开发是什么意思2021-10-28 2141

-

嵌入式开发2021-10-21 1537

-

嵌入式软件的开发流程_嵌入式软件的调试2020-08-31 6942

-

开发嵌入式系统的选择2019-06-20 877

-

嵌入式软件开发编程规范介绍2019-01-01 5242

-

基于嵌入式软件开发中构件技术的研究2017-10-30 1087

-

公司招聘嵌入式软件开发,求推荐!2016-09-07 4339

-

嵌入式系统开发圣经2016-03-22 1143

-

ARM嵌入式软件开发2016-01-15 1432

-

基于SCADE的嵌入式软件开发方法研究2016-01-04 686

-

嵌入式软件仿真开发系统的研究2011-03-07 1867

-

什么是嵌入式软件开发2009-04-20 9238

全部0条评论

快来发表一下你的评论吧 !