I2C总线缓冲器ASSP可处理宽电压电平转换范围

描述

微控制器 (MCU) 和相关设备的技术趋势是更小的几何尺寸,因此需要更小的工作电压。电路设计人员面临着将低压信号连接到各种其他设备电压的挑战。I2C 总线以其定义的协议和双向信号流对这些工作提出了独特的问题。集成电平转换总线缓冲器应用特定标准产品 (ASSP) 可以解决此问题,但也有其自身的障碍。

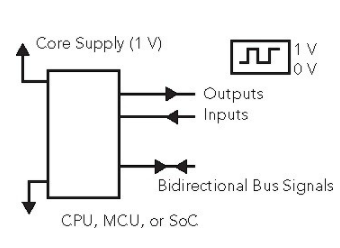

由于半导体制造技术的进步,最新的嵌入式计算设备具有较低的电源电压。这正在创造更小的晶体管几何形状,这反过来意味着更低的击穿电压。因此,信号摆幅现在比以前小得多,低至 1 V(图 1)。

图 1:缩小的晶体管几何尺寸导致击穿电压和信号摆幅比过去更低。

对于纯数字信号,有几种可用的接口设备可以将较小的信号转换为 CPU 输出端口的较高摆幅。同样,这些相同的器件可用于将现有信号降压为更小、更安全的输入,用于新的低压内核。例如,电压电平转换器 (VLT) 可以解决信号工作电压的任何不匹配问题,但双向 VLT 的设计却很棘手。特定应用标准产品 (ASSP) 解决了这个问题。

I2C 总线基础知识

I2C 总线依靠两个电气连接和两个外部电阻器来实现完整的双向信号传输。该协议是全面的,允许多个节点同时充当发送器和接收器,同时由于简单可靠的多主机仲裁而避免总线冲突。

I2C 总线上的数据流由主机控制,主机提供称为串行时钟 (SCL) 的时钟信号。数据沿称为串行数据 (SDA) 的第二个电气连接传递,并且 SDA 上的数据可能从主机流向从机,或以另一个方向流动。

I2C 总线的一个独特特性是节点的线或逻辑连接。当总线空闲时,没有节点消耗电流,总线信号被上拉电阻保持在逻辑 1(通常为 +5 V),SCL 和 SDA 各一个。信号由一个节点通过一个漏极开路驱动器拉低这些线路来断言(尽管基于双极技术的旧设备使用开路集电极设备来实现相同的结果)。主机发起每个数据事务,响应节点将 SDA 线拉低(响应设备也可能将 SCL 线拉低,但这种称为“时钟拉伸”的模式很少使用)。

双向电压电平转换器 (VLT)

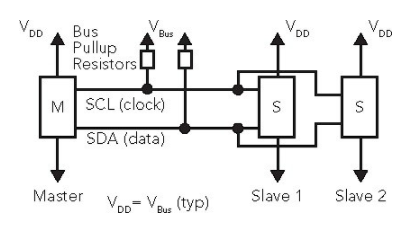

I2C 总线协议中没有硬件流控制,这使得 VLT 协议不可知,但也带来了电路设计挑战(图 2)。

图 2: I2C 总线协议中不存在硬件流控制,这给电路设计带来了挑战。

I2C 总线上的数据流向变化经常发生,实际上是在每八个时钟周期或传输一个字节数据之后。第 9 个时钟周期读取从设备以确认发送的数据已被理解。在第 9 个时钟周期期间,主机在 SDA 线上查找逻辑 0 确认(称为“ACK”)或逻辑 1 未确认(称为“NACK”)。VLT 负责可靠地来回传递这些信号。

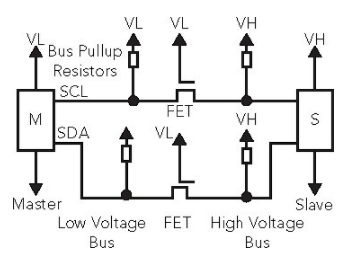

在第一代 VLT 设计中,典型的电压阶跃是从高侧的 5 V 到低侧的 3.3 V(通常是采用新技术的一侧)。一种常见的低成本转换解决方案是单个场效应晶体管 (FET) 器件(图 3)。

图 3:使用场效应晶体管 (FET) 和无源电压电平转换器 (VLT) 是一种常见的、成本相对较低的电压步进解决方案,尽管它存在局限性。

限制蔓延到这个拓扑中。虽然单个 FET 可以在两个方向上传递信号,但使用适当的 VLT 就没有隔离。一侧的负载必须由另一侧进行,从而限制了他们的吸引力。更糟糕的是,现有的低成本 FET 不太适合这些较低的总线电压。想象一下在 DDR4 RDIMM 设计(2.5 V 部件)中看到的将 CPU 内核(1 V 信号)连接到控制器所需的 1 V 至 2.5 V 接口的情况。具有较低栅极阈值的 FET 是必要且可用的(价格合理),但 I2C 总线缓冲器 ASSP 也可以解决这些较低总线电压的设计。I2C 总线缓冲器 ASSP 是基于 FET 的 VLT 的卓越解决方案。

I2C 总线缓冲器专用标准产品 (ASSP)

支持 I2C 扩展的 ASSP 已经存在了一段时间,更新的设计在一个令人印象深刻的范围内解决了 VLT,包括仅在 1 V 电源上运行的下一代 CPU 和片上系统 (SoC)。因为 ASSP 设备是缓冲器,所以它们分别加载到 I2C 总线缓冲器的每一侧。这对于不增加 CPU 或 SoC 的 I/O 引脚的负担很重要,并且允许在缓冲设备的另一侧连接更多节点;例如,新的智能手机和个人电子架构具有更多连接到 I2C 总线的传感器(节点)。

向设计中添加任何总线缓冲器时需要小心,因为这些设备必须操纵总线电压电平以避免致命的总线锁定情况。简单地说,I2C 总线缓冲器必须确定“A”侧的低电平是来自其自己的输出(即,“B”侧的缓冲低电平)还是“A”侧总线上的另一个外部设备。

总线缓冲器设计使用改变总线缓冲器输出电压的少数技术之一。在一种这样的方法中,添加了一个小偏移电压,该偏移电压足够小,不会干扰总线上的其他设备,但足以让总线缓冲器知道来自总线上另一个节点的外部(和低得多)信号之间的差异,以及它自己的逻辑0信号。典型的静态偏移仅为 90 mV。

总线速度改进

虽然早期的 I2C 总线以适中的速度移动(时钟频率为 100 kHz 或更低)并服务于当时的应用程序,但较新的应用程序需要更多的数据吞吐量,因此需要更快的时钟。当前的 I2C 规范定义了信号的时序,增加了几个高达1 MHz的新时钟速度。这些时钟速度被称为“Fm+”(快速模式加),比以前的 Fm(快速模式)速度提高了 250%,后者将时钟限制为 400 kHz。

请记住,决定总线时钟速度的是总线主控器(通常是已内置于 MCU、CPU 或 SoC 设备中的功能)的操作。从设备和总线缓冲器不产生时钟,也不关心时钟精度;一个 800 kHz 的总线时钟实际上可能以 20% 的容差运行。为了提高速度,必须降低总线负载(电容)。总线缓冲器分离总线并隔离每个段的电容。

提高时钟频率并非没有硬件挑战。无法控制的更快时钟和数据转换可能会导致振铃和下冲,因为 I2C 总线不是传输线,并且没有足够小的终端电阻来抑制快速信号边沿。I2C 规范限制了边沿的上升时间和下降时间。总线段的上升时间由系统负载电容设置,该电容是节点和互连信号走线电容的总和。板级电路设计人员只能自由选择 I2C 总线信号上拉电阻。

当 I2C 总线由现代高性能数字设备(CPU、MCU 和 SoC 类型)驱动时,需要注意减慢这些快如闪电的设备生成的时钟和数据总线信号的下降沿。如有必要,应添加一个外部串联电阻与杂散电容一起工作,以创建受控的下降时间并抑制 I2C 总线段上的任何振铃。或者,这可以通过添加一个小电容器来实现。

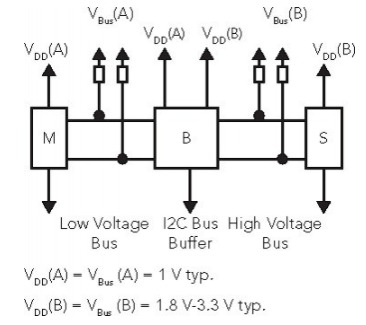

如果设计需要更高的数据吞吐量和在较低电源电压下运行的更新技术组件,则希望在您的设计中添加一个 I2C 总线缓冲器(图 4)。将 I2C 总线缓冲器的两侧视为单独的总线,并选择适合的上拉电阻。

图 4:需要更高数据吞吐量和更新技术组件的设计可能需要集成 I2C 总线缓冲器电压电平转换器 (VLT)。此处显示的是 NXP Semiconductors 的 PCA9617A 总线缓冲器,具有 Fm+ 速度和低至 1 V 的 VLT。

审核编辑:郭婷

-

SGM4551:双路双向 I2C 总线和 SMBus 电压电平转换器的深度解析2026-03-16 297

-

TCA39306双向I2C总线和SMBus电压电平转换器技术解析2025-12-17 520

-

TCA9803电平转换I2C总线缓冲器/中继器数据表2024-07-03 697

-

TCA9800电平转换I2C总线缓冲器/中继器数据表2024-07-02 482

-

TCA9801电平转换I2C总线缓冲器/中继器数据表2024-07-01 450

-

TCA4311热插拔I2C总线缓冲器数据表2024-06-29 485

-

TCA39306-Q1双路双向I3C、I2C总线和SMBus电压电平转换器数据表2024-06-21 615

-

ISL33001MSOPEVAL1Z I2C总线缓冲器评估板2024-06-07 495

-

硬件设计:接口--不同电源系统下I2C总线电平转换电路(电桥)设计2022-01-11 1015

-

LTC4301L:带低电压电平转换的热插拔2线总线缓冲器数据表2021-05-24 923

-

I2C总线:何时使用I2C缓冲器2020-09-06 4677

-

恩智浦推出世界首款无偏置电压I2C总线缓冲器2011-09-03 2241

-

电平转换在I2C总线中的应用(英)2010-07-23 802

全部0条评论

快来发表一下你的评论吧 !