SoC互连的功能和性能验证

描述

验证互连知识产权 (IP) - 将片上系统 (SoC) 中的内核和 IP 块粘合在一起的“粘合剂” - 对于高级 SoC 变得更加复杂,这需要特殊的互连 IP 来执行片上通讯功能。因此,这些 SoC 互连的功能和性能验证已经达到了新的复杂程度。已经开发了一些工具来简化验证,同时使设计工程师能够在设计周期的早期发现和修复互连问题。

还记得工程师过去可以依靠总线在芯片中执行片上通信功能的日子吗?那些日子显然已经成为过去,尤其是在我们日益互联的世界需要我们的芯片提供更多功能的情况下。当今先进的 SoC 需要互连来充当 SoC 内各种 IP 内核的通信中心。考虑到主机和从机的数量、不同的协议、不同类型的事务以及涉及的多层拓扑,验证 SoC 互连的功能和性能可能是一项复杂的任务。使用工具和技术的更全面的方法可以简化验证 SoC 互连功能和性能的过程。

通过功能验证防止意外

通过功能验证,设计人员希望确保多核芯片实现所需的功能,同时以相对顺畅的方式处理错误。从实际的角度来看,设计人员希望验证 SoC IP 块以及芯片的互连。这里有两个步骤。首先是通过验证 IP 验证 IP 块是否正确实现了给定的接口协议,这可以警告任何协议违规。验证 IP 监控仿真结果并根据协议规范执行极端情况测试;在此过程中,带有嵌入式断言的验证 IP 可以自动检测协议违规。此外,IP 中的测试套件和验证计划可以使验证过程快速结束。

使用互连验证 IP 块的第二步是验证命令和数据是否会以正确的格式到达正确的目的地。设计人员需要注意诸如数据拆分、扩大规模和缩小规模等问题。这很重要,因为互连子系统上的不同接口使用不同的协议;例如,作为一系列 APB 传输进入互连的数据事务可以在目标端口作为 AXI 突发输出。还应验证诸如窥探对话、窥探传播、窥探过滤器操作和跨缓存行等操作。换句话说,他们应该确保高速缓存一致性互连正确地发挥其作为一致性管理器的作用。为了节省远程内存访问时间,相干互连窥探相关主设备的缓存,并根据它们的响应,确定是从缓存中返回请求的数据还是从远程内存中返回请求的数据,并相应地更新相关主设备的缓存行状态。这种行为是由一致性协议定义的。如果互连不遵循协议,系统将很快进入非连贯状态并很可能崩溃。

通过性能验证满足带宽和延迟目标

性能验证是设计人员应确保设计满足其目标带宽和延迟水平的地方。考虑具有多个互连的 SoC 设计,以防止局部流量影响设备的其余子系统。互连 IP 在这里发挥着重要作用,因为它可以调整每个端口以获得独特的总线宽度、地址映射和时钟速度。通常,还有一些机制可以调整带宽和延迟,以调整每个域中的互连 IP。

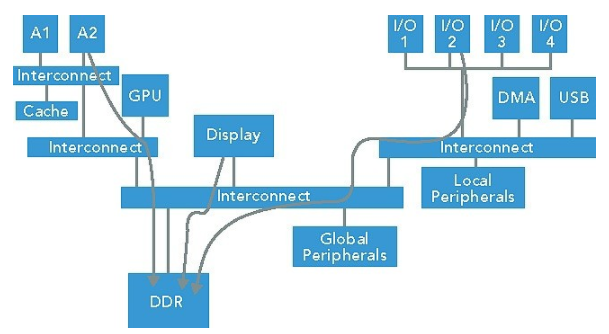

但是,仍然存在会发生流量冲突的情况,如图 1所示。在这些情况下如何平衡流量?大多数系统没有足够的主存带宽来容纳同时处于活动状态的所有 IP 块。重要的是防止一个 IP 块支配和压倒其他 IP 块;否则,系统性能会下降。在这种情况下,性能分析可能会有所帮助,从而最大限度地减少系统性能下降的影响。

图 1:流量管理和系统性能。在此图中,三个子系统正在尝试同时访问主存储器。性能分析有助于评估 SoC 图是否需要重新配置。

为了分析性能,设计人员需要比较来自不同 SoC 架构或不同 SoC 用例的带宽和延迟测量值。这种比较涉及对两个或多个(通常是几个)SoC 架构(或特定架构的实现)进行建模、运行仿真和测量性能,手动执行这些操作是不切实际的。毕竟,手动工作将需要围绕比较下的各种 SoC 架构构建测试平台。对于复杂的 SoC(其中性能分析和调整最为重要),对于经验丰富的工程师来说,创建必要的测试平台可能需要几天时间,而对于经验不足的工程师来说则需要更长的时间。

绩效分析的五个重点领域

为了使绩效分析尽可能有效和高效,您应该努力将五个方面整合到流程中:

周期精确建模——利用周期精确度,逻辑仿真产生与在实际芯片中看到的具有相同时序的相同事件顺序。周期精确的仿真模型包括在 SoC 设计过程中创建的 RTL 级 Verilog 或 VHDL。

自动 RTL 生成——自动生成的互连 RTL 是朝着创建完整的 SoC 周期精确模型迈出的一步。为了确定提供最佳整体性能的组合,设计人员需要能够快速生成互连 IP 的多种变体。

验证 IP – 如前所述,验证 IP 有助于发现协议违规。

测试台生成——自动生成测试台可以节省数周的时间,否则开发可能会花费数周时间来创建互连测试环境。

深入分析——收集所有仿真数据(设计评估、测试台和流量)的能力对于调试性能问题和确定设计更改可能如何影响带宽和延迟是必要的。

图形互连仿真比较

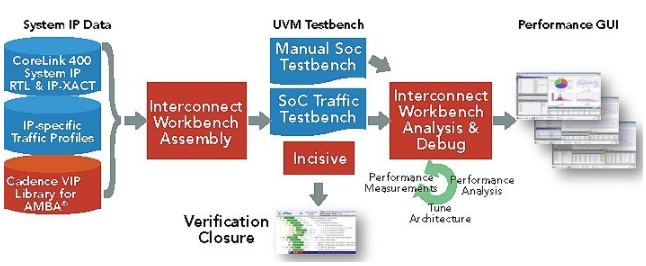

已经开发了一种工具,它提供了一种图形方式来比较互连仿真运行,以便快速准确地评估互连性能。Cadence Interconnect Workbench 有助于在设计周期的早期发现和修复互连问题,以达到 SoC 所需的带宽和延迟水平。使用该工具,其流程如图 2 所示,工程师可以抛开繁琐的电子表格,利用带有内置过滤器的 GUI 来选择主设备和/或从设备以及评估和执行“假设”分析的路径。GUI 可以让您快速轻松地了解设计更改如何影响感兴趣的仿真结果的带宽和延迟。例如,工程师可以比较并找到特定用例或在单个配置上运行的多个用例的理想配置。他们可以快速查看到每个从站的流量比例以及它们的延迟分布情况。实时过滤和分析功能消除了电子表格可能非常繁琐的过程。

Interconnect Workbench 与 Cadence Interconnect Validator 集成,这是一个验证 IP 组件,可收集所有事务并在数据通过 SoC 互连结构时验证数据的正确性和完整性。互连验证器连接到所有接口级验证 IP 实例(它们正在监视 IP 块的正确协议行为),因此对进出互连的数据和命令有深入的了解。通过匹配这些数据,该工具可以验证数据是否被传送到正确的目的地。如果互连不遵循协议,则会发出错误。

图 2:通过 Cadence Interconnect Workbench 的数据流。在左侧,RTL、验证 IP 和流量模式描述移至工具中,该工具会自动生成用于仿真的测试平台。当生成 SoC 的其他变体时,该工具还会生成其他测试平台。性能 GUI 提供了模拟结果的概览。

高效且有效的互连验证

面对持续不断的上市时间压力和日益复杂的 SoC 设计,很难找到不想从设计周期中缩短时间的工程师。特别是在高级节点,验证 SoC 互连已成为一个耗时的步骤。但是,工具现在可以高效且有效地执行周期精确的性能分析和互连验证。

作者:Nick Heaton,Avi Behar

审核编辑:郭婷

-

移动SoC的时钟验证2023-07-17 1854

-

HBM性能验证变得简单2023-05-26 1559

-

验证SoC功能、时序和功耗的最快解决方案2022-07-26 1607

-

设计和验证技术如何确保汽车SoC的功能安全2022-06-13 2398

-

一个优秀的SOC验证环境应该具备哪些功能呢2022-05-31 2371

-

SoC验证平台的FPGA综合怎么实现?2019-10-11 1670

-

SoC设计中的互连验证中遇到的问题2019-08-12 3703

-

SoC互连有必要自己动手吗2019-08-10 1027

-

基于FPGA的验证平台及有效的SoC验证过程和方法2017-11-17 22926

-

如何设计和验证SoC2017-04-05 6921

-

Incisive 12.2版本融入Cadence验证IP,SoC验证效率提高50%2013-01-27 1980

-

一种基于事务的SoC功能验证方法2010-02-24 820

-

在SoC设计中采用ESL设计和验证方法2009-11-30 768

-

SoC芯片验证技术的研究2009-08-31 811

全部0条评论

快来发表一下你的评论吧 !