PCB布线怎么才不会影响到信号的波形

电子说

描述

在高速数字信号中,PCB布线的目的,就是保证接收端能够正确接收到发射端的信号。正确体现在两个方面:

(1)如果设计到时钟的话,需要保证时序的正确性;

(2)波形幅度需要符合要求,因为数字信号一般对大于VIH的电平判别为高,低于VIL的电平判别为地。所以,当幅度处于VIL~VIH之间的话,则无法判断。

总之,我们希望PCB布线不会影响到信号的波形。

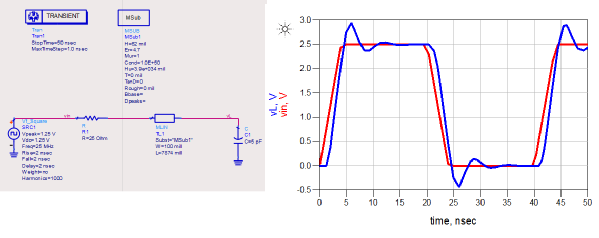

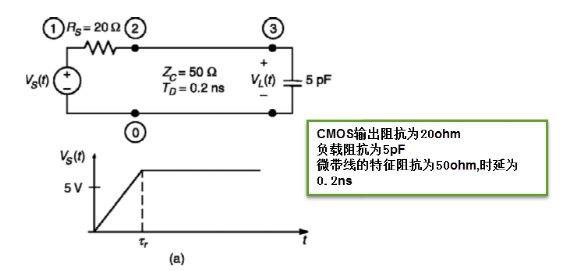

微带线失配,会产生反射,导致波形失真,如下图所示。蓝线为负载端输出信号,红线为源输出信号。接收端信号产生振铃。

以下例子是比较合理的假设,因为一般CMOS的输出阻抗为10~30ohm,而CMOS的输入一般呈容性,容值为5~15pF。

微带线终端负载对信号波形的影响

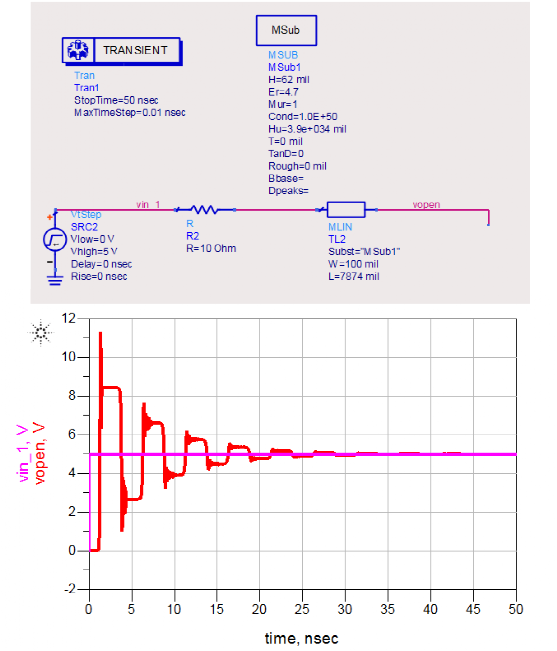

终端负载为开路

如下图所示,可以看到,当负载为开路时,其接收端的信号,会先产生振铃,然后再稳定在5V。而在振铃处,最高电压能到11V,最低值在1V左右,高压可能导致芯片的损坏,低压可能导致芯片的误判。

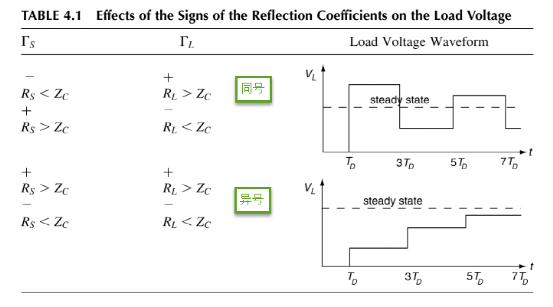

这些振铃的产生,是因为信号在负载端和源端不断地来回反射,叠加产生的。所以,Γs和ΓL的符号的不同,还会影响叠加信号的波形。

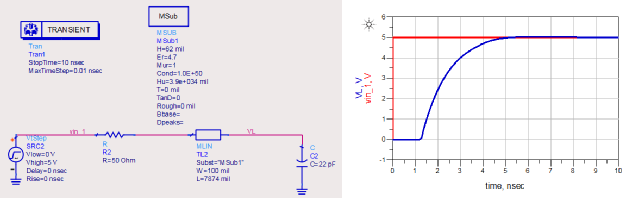

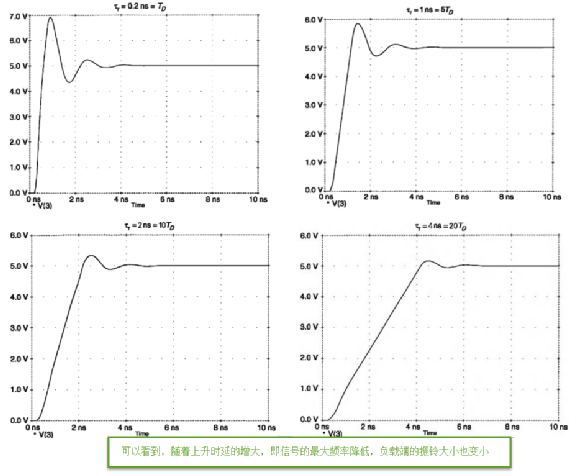

终端负载为容性负载

假设源端做了串联匹配。源端信号为0上升时间的理想阶跃信号,电容在刚开始时,看上去为短路,然后缓慢地变成开路。电容会引入额外的时延。

匹配策略

反射会引起信号失真,而源端和终端的失配会引起反射。那想缓解信号的失真,有效的手段,就是进行匹配。

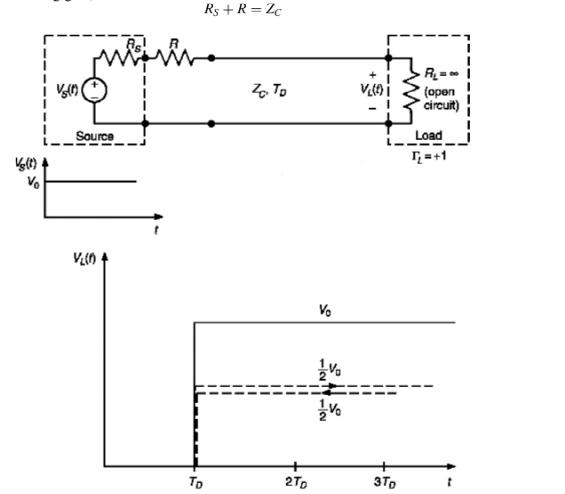

串联匹配

一般来说,典型的CMOS的输出阻抗都小于PCB的特征阻抗,所以可以在PCB线上加一个电阻,使得Rs+R=Zc,这样,在源端没有反射。

这种匹配方式,即为串联匹配。

在串联匹配的情况下,源端输出到微带线的电压为V0/2,而终端负载一般为开路或者类似开路,所以负载反射系数为1,因此在负载处的电压为V0/2+V0/2=V0,信号完整性很好。

而且,对于开路负载,没有电流流入该电阻,所以不额外耗散功率。

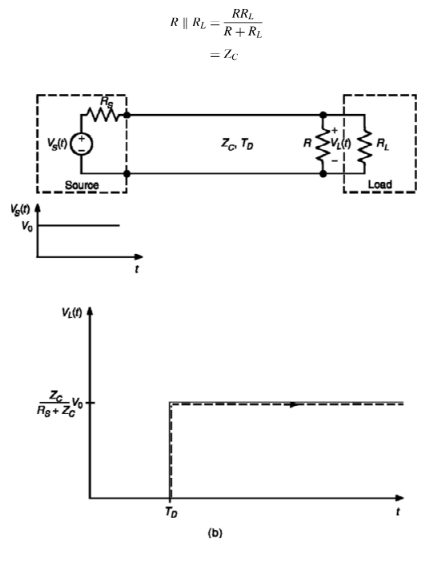

并联匹配

并联匹配,即在负载端并联一电阻R,使得负载阻抗为Zc。

并联匹配下,接收到的电压会比发射端的电压小,因为并联匹配时,没有负载反射来提高输入波形的电压。而且,即使对于开路负载,并联电阻上也会有电流,因此匹配负载会消耗功率。

那什么时候,可以不care微带线的长度,而且不需要做匹配呢?

假设脉冲信号的上升时间为τr,则该脉冲对应的主要频谱带宽为

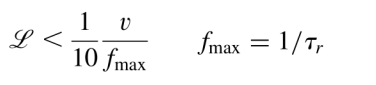

想要微带线的尺寸可以忽略,则需要其长度小于传输信号最大频率时对应波长的十分之一。

即

所以,当微带线的长度和传输信号的上升沿时间有如下关系时,微带线上的任意失配基本不会造成信号的失真。

参考文献:

CLAYTON R. PAUL Introduction to electromagnetic compatibility

审核编辑 :李倩

-

ADS8568 采样会影响到输入信号问题,求答疑2025-01-21 287

-

104条关于PCB布局布线的小技巧2025-01-07 1881

-

pcb电源布线规则分享 PCB电源布线的六大技巧2024-05-16 3799

-

关于PCB布局布线技巧的104的问题2024-01-02 1649

-

PCB布线对模拟信号传输的影响如何分析2023-10-31 1650

-

PCB布线技巧升级:高速信号篇2023-08-01 3916

-

PCB布局布线技巧104问2023-05-05 1045

-

浅谈PCB关键信号的布线要求2023-01-13 2513

-

如何实现混合信号PCB的分区设计2020-05-05 2806

-

pcb关键信号如何去布线2020-01-01 3922

-

混合信号PCB怎样做到分区设计2019-10-23 2106

-

PCB走线会影响到已经布完的线吗?2019-09-25 1715

-

混合信号PCB分区设计指南2009-01-23 673

-

混合信号PCB的分区设计2006-04-16 647

全部0条评论

快来发表一下你的评论吧 !