使用QorIQ多核处理器管理机器安全和生产力

描述

在北美和欧洲,UL 或 CE 标志是大多数家庭熟悉的景象。鲜为人知的是这些标志所代表的含义,以及制造商必须遵循的严格流程才能获得这些标志的资格。这些严格流程背后的一个关键动机是安全性,它适用于设备和机械,从手持电动工具、电梯、铁路系统和工厂车间的机器人到核能、石油和天然气设施。安全在后一组中至关重要,但人们日常使用的设备也受到了类似的关注和关注。

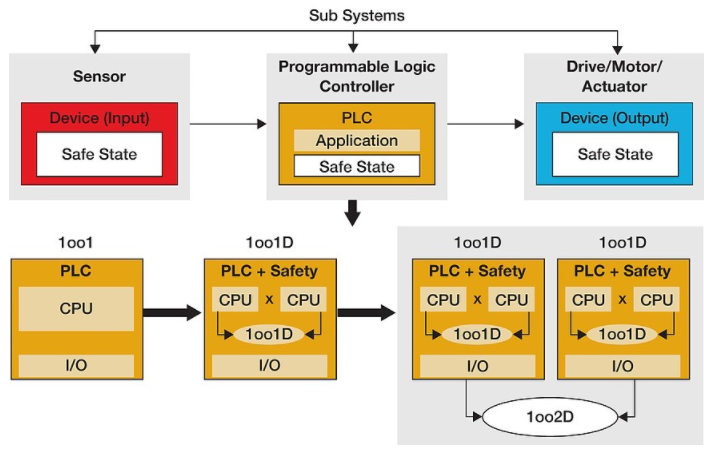

业界所谓的“功能安全”背后的目标是限制对操作或使用设备和机械的人员造成身体伤害或健康影响的风险。设备不仅必须正确运行以响应输入,而且还必须安全地管理任何操作员错误、硬件故障或环境变化。虽然功能安全涵盖端到端系统,但控制子系统侧重于传感器、可编程逻辑控制功能和驱动子系统。以下内容涵盖了对控制子系统架构的功能安全影响,以及 QorIQ 多核处理解决方案如何通过提高机器生产力来更有效地满足安全要求。

让机器安全

涵盖功能安全的标准由每个国家的管理机构指定。对于欧盟国家,基准是 IEC 61508。在北美,执行 ISO 13849 规范。获得认证的过程涉及确定所需的安全功能、潜在危险和所需的任何降低风险的许多步骤。这有助于确定 ICE 61508 所需的安全完整性等级 (SIL) 或 ISO 13849 的性能等级 (PL)。该过程中的其他关键因素包括硬件容错 (HFT) 或故障设备的数量可以容忍,以及安全故障分数 (SFF),它是系统在安全状态下发生故障的概率。这些方面的责任在于具有适当技能的工程师,他们喜欢标准,

HFT 和 SFF 很重要,因为它们是子系统冗余和诊断能力的量度。HFT 取决于系统中使用的冗余量和投票策略。SFF 是衡量内置诊断的故障安全设计和质量的指标。

图 1 显示了具有两种投票架构和诊断功能之一的双冗余系统(2 个中的 1 个带有诊断功能,或 1oo2D)。1oo2D 意味着两个通道将处理相同的输入并请求某个动作。投票者将比较来自两个通道的请求,但仅使用来自具有良好诊断的通道的数据。此实现还提供了对 1oo1D 的冗余回退。

图 1:确保系统安全需要额外/重复的硬件资源。这里展示的是双冗余系统的 1oo2D 架构。1oo2D 架构允许投票者从两个诊断通道中的任何一个中比较和选择最佳输入数据。

诊断将报告软件或随机故障、不正确的操作员输入或由环境影响引起的常见故障(由 EMC、振动、温度或压力变化引起的内存或数据总线损坏)。在 QorIQ 多核处理器的情况下,可以在使用本地高速缓存/内存的内核上实现通道。此处将使用的基本硬件功能是纠错码 (ECC) 和内存奇偶校验。确保系统安全需要额外的处理性能来提供实时计算和诊断。复制硬件资源提供了必要的冗余,以增加系统在发生故障时达到安全状态的可能性。

冗余和实时诊断

这就是设备或机器制造商面临的挑战:添加冗余对硬件成本有直接影响,因为它传统上涉及复制控制器模块或处理器组件。这导致两个问题:

可以在不复制硬件的情况下提供功能安全吗?

更智能、更集成的诊断能否同时帮助管理功能安全和生产力?

为了更详细地说明第二个问题,请考虑装配线上的机器人。机器人由光幕保护。

2a和2b之间有明显的区别。第一个说明了操作员有受伤风险并且机器人应该断电或停止的事件。在第二个插图中,情况并非如此,也许放慢机器人的速度就足够了。一个可以区分的系统将提高生产力,因为它可以保持安全,也可以保持生产线的运转。在这种情况下,可以使用额外的光幕来指定“缓冲区”和“操作”区域,或者基于视觉的系统可能是答案。在这两种情况下,控制器现在都需要考虑额外的传感器输入以及必须实时执行的额外处理。

考虑 QorIQ 多核处理器

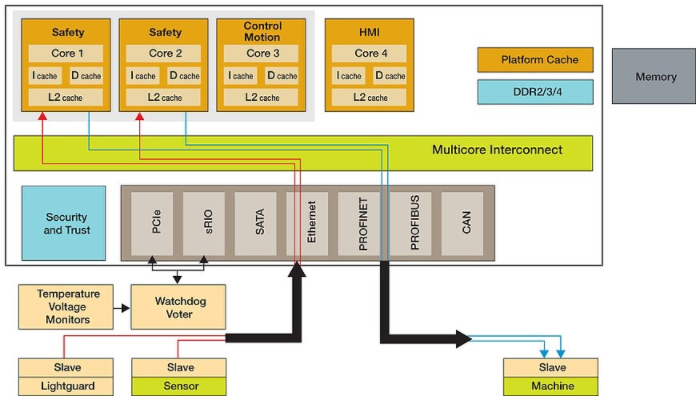

这两个问题的部分解决方案在于 QorIQ 多核处理器,这是一系列处理平台,从单核、双核和四核到多核,均基于集成双精度浮点的 32 位或 64 位 Power Architecture 内核观点。图 3(第 16 页)显示了可编程控制和安全功能如何在单个 QorIQ 多核处理器上共存。不同的功能可以使用共享或专用互连、内存和 I/O 资源在此架构上运行。硬件强制允许不同的功能在不受其他内核或外部主机上的其他功能干扰的情况下运行。

图 3: QorIQ 多核平台上的硬件实施允许可编程控制功能和安全功能存在于同一处理器上而不会受到干扰。注意:共享内存和排队系统也可通过 PCIe 和 sRIO 供外部实体使用。

安全应用中的主要元素是通道。在这里,实现通道的硬件需要提供某种形式的隔离。在 QorIQ 多核处理器中,通道将由在设备上物理实例化的核心复合体构建。核心复合体有两层缓存(第 1 层(I/D 缓存)和第 2 层(L2 缓存)),以不同的模式使用允许本地存储。这与单个内核的内存管理单元 (MMU)、硬件管理程序和虚拟化支持以及外围访问管理单元 (PAMU) 相结合,确保赋予软件任务的权限对硬件可见,从而允许强制执行隔离。

硬件管理程序和虚拟化支持隔离逻辑容器

PAMU 在处理器中隔离智能外围设备,如以太网控制器、加密加速和其他设备。这有效地允许将 QorIQ 多核处理器视为一组具有自己智能 I/O 和内存的独立 CPU。

与任何 CPU 一样,内核会收到内核复合体中硬件检测到的异常通知;例如,核心定时器或看门狗定时器中的单个或多个 ECC 错误。内核还可以了解内核复合体之外的设备异常,例如内部和外部存储器的 ECC 错误或存储器违规。对设备的所有外部存储器映射访问也受到 PAMU 的监控,这将阻止和标记未经授权的访问尝试。异常可以路由到设备中的任意数量的内核,并且可以在外部进行标记。因此,使用核心复合体的通道可能会将与其相关的异常路由到其自身和/或另一个内部监视器(另一个核心),或外部监视器,例如 PCI Express (PCIe) 或串行 RapidIO 块上的主控。

除了检测上述标准硬件错误的设备外,QorIQ 信任架构还提供了从通电开始建立安全可信节点的能力,也称为加密启动。这使硬件能够验证设备上任何地方的内存代码或静态数据块,以便在设备的正常运行时间期间进行更改,从而创建一种硬件方法来补充通常在软件中运行的诊断例程之一。

内部处理器通信支持集成诊断

在安全应用中,通道之间的通信很可能通过黑色通道实现,在多核平台的情况下,黑色通道位于处理器内部。为了帮助 QorIQ 多核处理器内部的通信,内核之间存在三个独立的通信路径:

受 MMU/PAMU 保护的共享内存

将各个物理端口链接到每个核心复合体的硬件排队系统

内核间消息寄存器*

这种多核方法与离散解决方案相比具有许多优势,允许多个安全通道和组件或模块的整合。该集成提高了诊断能力,进而支持更好的机器可用性和生产力。

审核编辑:郭婷

-

QorIQ®T1042多核处理器2025-01-10 4011

-

新质生产力是指什么2024-02-28 12705

-

新质生产力哪些行业发展最好 如何提升新质生产力2024-02-22 6696

-

为什么底噪的好坏关乎着示波器的生产力?2021-05-10 2525

-

如何提高FPGA设计生产力?2021-05-06 1078

-

浅议多核处理器技术2021-03-29 1279

-

飞思卡尔的QorIQ通信平台功能如何?2019-07-30 1931

-

多核处理器的优点2019-06-20 5143

-

请问TI的多核处理器生产工艺达到多少nm,主要产品型号是什么?2019-01-14 2715

-

关于QorIQ处理器中trust架构的介绍(一)2018-06-28 4214

-

处理器关于多核概念与区别 多核处理器工作原理及优缺点2017-12-08 33027

-

多核处理器设计九大要素2011-04-13 3308

-

QorIQ通信处理器飞思卡尔2009-12-09 977

-

飞思卡尔推出8内核 QorIQ P4080 处理器样品2009-11-10 1335

全部0条评论

快来发表一下你的评论吧 !