可配置的A/D外设克服了SoC器件的缺点

描述

对于嵌入式系统设计人员来说,最令人沮丧的情况之一发生在当他们完成许多设计里程碑后,他们发现最初选择的嵌入式设备不符合当前的设计要求。在开发周期过程中,会出现需求变化和其他不可预见的挑战,尤其是在新产品设计中。

已开发出片上系统 (SoC) 设备,尤其是混合信号 SoC 设备,以克服这些困难。虽然不同的 SoC 公司有不同的方式来描述他们的 SoC,但归根结底,SoC 本质上是一个微控制器(无论是低功耗 8 位还是高功率 32 位),具有大量集成的模拟和/或数字外围设备。此外,SoC 设备引入了自定义、配置和编程这些资源的能力。

可配置性使客户能够灵活地决定如何将比较器和运算放大器等外设路由到引脚。这些组件的静态引脚位置与传统的固定功能微控制器不同。使用设备上的一系列寄存器,客户可以根据他们的特定应用需求配置设备。此外,混合信号 SoC 设备还可能包含在不同级别上可编程的数字资源,从基本的可配置逻辑到更大的可编程逻辑设备 (PLD) 资源,可以使用诸如 Verilog 之类的硬件描述语言进行配置。使用这些可编程数字资源,开发人员可以轻松创建状态机和其他复杂电路,例如在硬件中对数字信号执行 FFT。

虽然具有这种高水平的可配置性允许开发人员适应开发过程中可能发生的设计更改,但仍有一些情况会达到所选 SoC 的限制。这些限制可能是由于设计要求超出了部件的能力,或者是由于需要在器件芯片上实现没有固定功能组件的特性或特定功能。通过利用使混合信号 SoC 如此有用的可配置性和灵活路由,开发人员可以克服设备架构本身可能存在的许多缺点。探索其中的几个设计挑战和几个关于 SoC 设备如何克服这些问题的实际示例可以提供洞察力。

克服模拟 SoC 挑战

克服模拟设计挑战可能是嵌入式混合信号开发中最困难的事情之一。与被认为更“通用”且更像构建块的数字外围设备不同,模拟外围设备的功能“相当固定”,因为它们本质上是一个组件系统,而不是构建块。工程师将可以使用模拟外设,例如模数转换器 (ADC)、比较器和数模转换器 (DAC),所有这些都可以配置到某种级别。

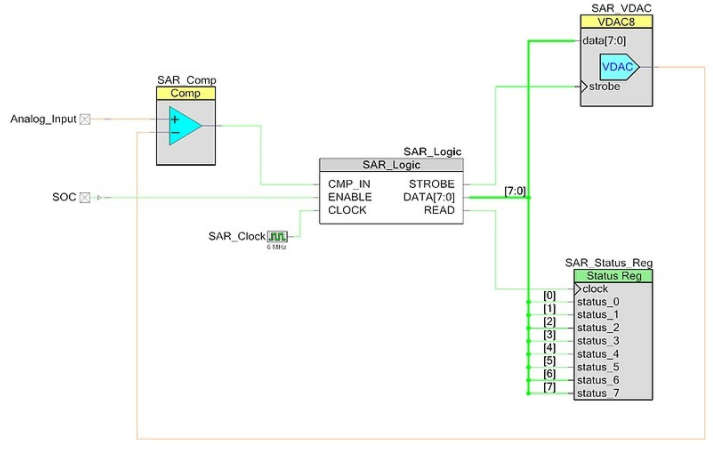

一个普遍面临的设计挑战是设计中需要额外的 ADC。如果客户不想多路复用 ADC 输入或想要实现特定类型的 ADC,例如仅包含 Delta Sigma ADC 的设备中的逐次逼近寄存器 (SAR) ADC,则可能会遇到这种情况。要了解 SoC 如何从自身内部克服这一点,让我们从设计中需要 SAR ADC 的角度来看这个问题。构建 SAR ADC 所需的组件是比较器、DAC、状态寄存器和一些可编程数字逻辑。所有这些都是可以在 SoC 设备上找到的组件。当这些组件以类似于图 1 所示的方式排列时,可以创建功能性 SAR ADC。

图 1:使用可用资源实施 SAR

通过读取存储在状态寄存器中的内容来收集 8 位输出。各种数字功能,例如算术运算和位移,使用 Verilog 在硬件中完成。这种资源组合创造了以前不存在于 8 位 118 KSps 设备中的功能。作为一个额外的好处,只要有更多的比较器、DAC 和数字逻辑,就可以提供额外的 SAR ADC。

许多混合信号 SoC 设备还包含专用比较器和运算放大器。当这些资源耗尽时,或者在设备从一开始就没有包含这些外围设备的情况下,可以做什么?模拟电路,例如比较器、有源滤波器、可编程增益放大器和跨阻放大器,都由一个运算放大器组成,该运算放大器使用各种电阻器和/或电容器来创建特定功能。一些混合信号 SoC 包含所谓的开关电容 (SC) 外设。SC 外围设备围绕低噪声、低偏移运算放大器构建,周围环绕着模拟多路复用器,周围环绕着电容器和开关组。如果开关处于静态打开或关闭状态,则结果是一个电容器连接到电路。此外,如果开关以特定频率交替打开和关闭,则开关电容器开始表现得像一个无损电阻器。

包含开关电容器的器件,例如 Cypress Semiconductor 的 PSoC 系列器件,使用寄存器配置来控制开关电容器拓扑中的开关,以产生各种电路,从最基本的运算放大器到更高级的电路,例如混合器、积分器或粘性和保持。

克服数字 SoC 挑战

开发人员面临着 SoC 架构的重大数字设计挑战。考虑到传统的微控制器,它将包含一些固定功能的数字外设,例如脉冲宽度调制器 (PWM) 和定时器。SoC 设备包含数字逻辑,例如可编程逻辑设备、算术逻辑单元 (ALU) 和状态/控制电阻器。使用诸如 Verilog 之类的硬件描述语言,可以将这些硬件资源配置为协同工作以创建许多可能的功能组件。

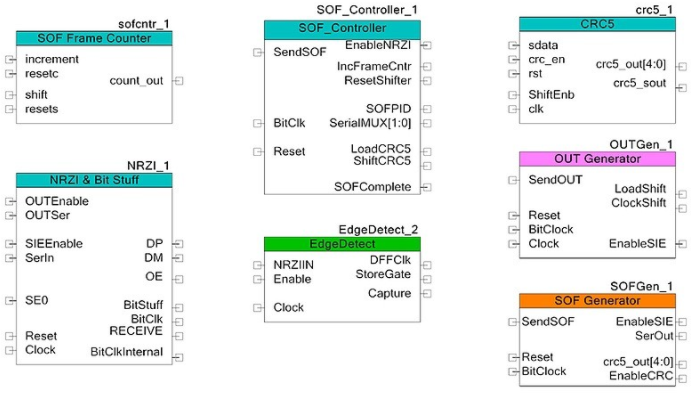

考虑一个包含外围 USB 接口的 SoC 设备。在设计周期的后期,我们决定还支持主机 USB 功能以实现诸如允许连接 USB 闪存驱动器以进行数据记录或现场可编程固件更新等功能。问题是正在使用的设备不包含实现主机功能所需的硬件。然而,使用可配置的数字资源,SoC 设备可以克服这种数字设计限制。

要了解需要合并的内容,请考虑处理 USB 通信需要什么。有差分信号,然后是 SOF 生成、不归零反转 (NRZI) 编码/解码、循环冗余校验 (CRC) 计算、位填充和 IN/OUT 数据包解析。如果设计人员阅读 USB 规范,他们会发现所需的一切实际上都可以在 PLD 中实现,并借助一些附加组件。通过一些广泛的 Verilog 编码来利用前面描述的数字资源,可以制作用于主机 USB 通信的各个组件,如图 2 所示。这里,所示的每个块代表具有各种数字输入和输出的 Verilog 实现。通过将这些组件与一些粘合逻辑连接在一起,

图 2:使用可编程硬件实现 USB 主机

这种可配置性意味着,如果为包含例如两个 PWM、两个比较器、两个 DAC 和一个 Delta Sigma ADC 的设计选择混合信号 SoC,则这些外设并不是其硬件功能的终点。可以重新利用和修改资源,以将资源扩展到与最初可能需要的功能不同的功能。这样,工程师无需迁移到新的嵌入式设备,就可以增加产品的价值并减少新产品设计的开发时间;该决定通常会导致新的固件开发和 PCB 布局,从而导致时间和金钱的损失。通过调用在早期电气工程课程中学到的技能以及混合信号 SoC 设备的灵活性

审核编辑:郭婷

-

怎么设置蜂鸟E203 soc外设的可配置寄存器读写属性?2024-01-10 762

-

外设SPI在SOC设计中的应用2023-09-24 1990

-

印刷电路板(PCB)可配置逻辑功能2023-08-29 1103

-

SAM L10/L11系列可配置定制逻辑外设实现2021-03-31 1137

-

Dialog最新可配置IC扩展电机驱动应用2020-09-02 5029

-

新的纳米化学体系克服了医疗领域里的种种难题2019-12-03 1211

-

新外设的技巧与诀窍之互补波形发生器和可配置逻辑单元及数控振荡器2018-06-27 1261

-

可配置逻辑单元(CLC)2018-06-07 5644

-

可配置技术影响SoC(系统级芯片)的设计2018-02-08 1875

-

用于SOC或块级时钟的可配置分频器2013-01-09 8283

-

可配置处理器开发原理2011-04-19 2560

-

飞兆半导体多功能可配置74AUP系列TinyLogic器件2011-01-13 930

-

SoC设计链中的可配置IP2009-12-14 501

全部0条评论

快来发表一下你的评论吧 !