生产和验证高质量的FPGA IP

描述

验证 IP 不仅仅是功能。功能的交互、时间的可变性和测试策略都成为更广泛的验证策略的因素。

FPGA 在过去十年中不断发展,变得更大、更复杂。为 FPGA 开发的知识产权 (IP) 在尺寸和复杂性方面同样有所增加。为了应对这种日益增加的复杂性,IP 开发人员采用了一流的验证方法。即使使用这些方法,为 FPGA 开发 IP 仍然会带来典型 ASIC 设计人员可能不会遇到的独特挑战。

FPGA 开发提出了三个关键挑战。一是 FPGA IP 通常是高度参数化的,这会产生大量的设计变体来进行测试。另一个问题是 FPGA IP 开发人员需要验证一旦集成到用户设计中就可以满足时序要求。最后,为 FPGA 开发的 IP 比为其他平台开发的 IP 更容易受到架构变化的影响。验证环境以尽可能少的工作量适应这些架构更改非常重要。

参数化特征

FPGA 的每门成本高于相应的 ASIC,因此以 FPGA 为目标的设计人员有动力创建不消耗任何不必要资源的 IP。ASIC 将实现所有支持的功能,而 FPGA 可以选择仅实现客户需要的功能。因此,FPGA IP 可以而且应该进行参数化,以便综合去除不需要的逻辑。例如,如果不需要以太网统计收集功能,Xilinx 10 GbE MAC 内核的大小将缩小约 25%,从而为其他逻辑释放 FPGA 资源。

在确定将要参数化的内容时,数据总线宽度、流水线级数和可选功能等因素是很好的考虑因素,因为它们允许设计人员或客户在性能和消耗的资源之间进行权衡。可以通过参数化特定于平台的功能(如 Block RAM 和 DSP 块)来进行进一步的权衡,而不是使用结构逻辑。

缺点是每个添加的参数都会创建另一个必须测试的排列。验证工程师如何知道参数已针对所有值执行?最好的方法是收集覆盖率统计数据并分析模拟器生成的覆盖率报告。例如,如果设计具有控制 IP 是使用 32 位还是 64 位数据路径的数据宽度 (DW) 参数和控制是否使用额外流水线来帮助满足时序要求的流水线 (PL) 参数,带有简单覆盖点的基本覆盖率报告可能会显示 DW 和 PL 的值都被执行了。但是,它不会显示是否在没有额外流水线的情况下测试了 64 位数据路径。为了实现这一点,

对于大量参数,很快就会发现,如果允许随机设置每个参数,那么命中每个排列将永远持续下去。验证工程师必须定义相关的参数排列子集,并且对最终客户更有可能使用的参数排列权重很大。此外,应该选择更好地执行设计的排列,例如那些导致完全 FIFO 条件或很少使用的状态转换的排列。约束随机验证非常适合此目的,因为它允许工具根据验证者的约束随机化参数值,并使用覆盖率度量来查看是否命中了重要的排列。如果不是,则验证者可以运行更多测试或更改约束值分布的权重。

验证时间

FPGA IP 开发人员面临的挑战之一是确保 IP 一旦集成到客户设计中就能够满足时序要求。由于难以对具有大参数空间的设计进行功能验证,因此同样难以理解参数对满足时序能力的影响。开发人员面临的另一个障碍是 IP 可能会与用户设计的其他部分竞争 FPGA 架构资源,这会使满足时序要求变得更加困难。

开发人员可以采用多种技术来帮助确保 IP 将继续满足时序要求,即使集成到用户设计中也是如此。有代表性的示例设计很不错,但不是必需的。如果示例设计不可用,请双重注册将进入 FPGA 架构的所有 I/O。芯片上或关闭的 I/O 应连接到适当的位置。

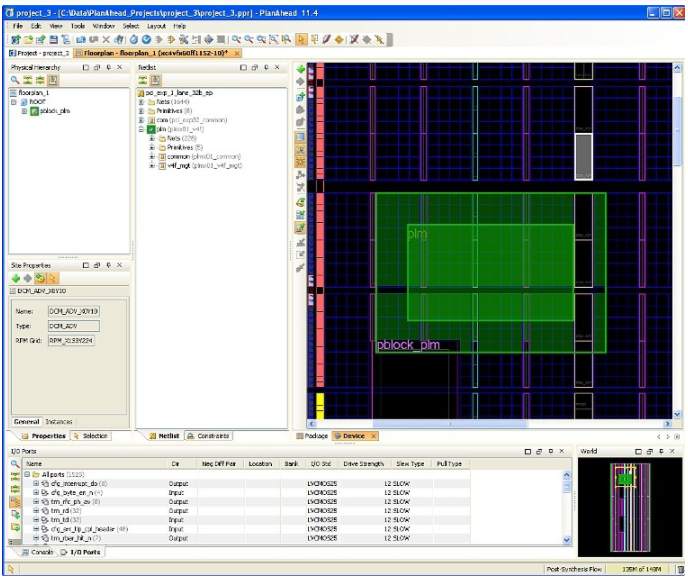

一旦设计到位,下一步就是在目标 FPGA 架构中实现设计。作为测试过程的一部分,将 IP 时钟频率过度约束 15%。此外,向 IP 添加一个区域约束,使其被约束到 FPGA 架构的一个区域,该区域不会比其最小布局需求大很多,如图 1 所示。这将模拟 IP 集成到用户设计。

图 1: Xilinx PlanAhead 工具中的 IP 块被限制在芯片的一个小区域内,以在将 IP 集成到设计中时模拟拥塞。

最后一步是确保不同的参数设置不会对满足时序的能力产生不利影响。确定最有可能对时序收敛产生影响的关键参数。随机化识别的参数,以区域约束和更高的时钟频率运行,并确保在 IP 目标的所有 FPGA 器件中仍然可以满足时序要求。开发人员运行的参数组合越多,他们对 IP 即使在最困难的客户环境中也能满足时序要求的信心就越大。

将测试场景与实现分离

设计人员可能需要在设计周期后期更改内核的延迟或数据路径宽度,作为对布局和布线的响应,表明设计将难以满足时序要求,或者利用更快、更快速的 FPGA /或具有不同数量的资源。如果验证工程师没有预料到这种变化(例如,测试场景假定一个固定的延迟),那么可能需要更改大量测试来编写新的预期。一个设计良好的验证环境将需要很少的更改来响应这一点。

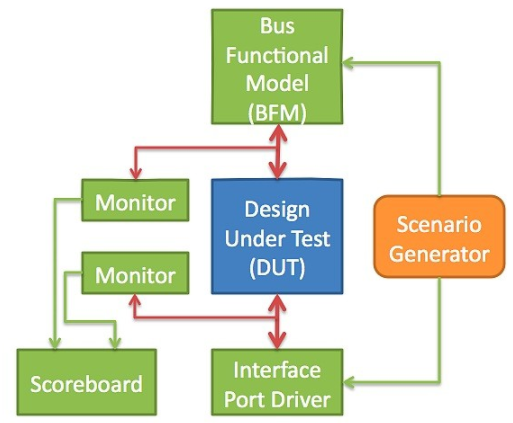

将测试台环境与被测设备 (DUT) 实现细节分离的最佳方法之一是使用记分板,如图 2 所示。测试场景将预期结果(例如,数据包)推送到记分板中,当 DUT 生成数据时,测试台会自动将其与记分板版本进行比较。当 DUT 产生数据时,不需要关心测试场景,只需要关心它产生了什么数据。

图 2:使用记分板是将测试台环境与被测设备分离的最佳方法之一。

此外,如果数据路径的宽度发生变化,并且 DUT 产生的数据被划分为几个额外的周期(或统一为更少的周期),那么记分板会在测试台中提供一个点,其中与该预期的比较可以是改变了。在测试场景中对期望进行硬编码的替代方法要求在 DUT 的数据宽度或数据格式发生变化时更新每个场景。

需要对端口驱动程序和监视器进行编码以预测接口变化。当需要快速适应时,允许这些模块连接到不同数据宽度的端口和接口的前期工作可以在设计和验证周期的后期获得回报。

FPGA IP,已验证

在过去几年中,可用于 FPGA 的 IP 数量大幅增加。为了具有竞争力,供应商必须始终如一地满足对质量的期望。由于 FPGA IP 的上市时间需求变得越来越迫切,供应商必须尽一切可能防止交付的内核出现可能拖慢客户速度的问题。这意味着必须采用经过深思熟虑的、能够快速适应的验证策略。

作者:Jason Lawley,Jeremy Goolsby

审核编辑:郭婷

-

protel输出高质量gerber2011-12-12 26158

-

高质量C++、C编程指南2012-08-06 5073

-

高质量C&C++2012-08-16 2723

-

高质量C++&C 编程指南2012-08-19 2485

-

原版PIC实战项目-C(高质量PDF版本)2013-07-10 13690

-

高质量C语言编程2013-07-22 13849

-

编写高质量C语言代码2013-07-31 4703

-

林锐《高质量C语言编程》2013-08-17 2442

-

高质量C++与C编程指南2014-03-09 5426

-

高质量编程2016-02-27 7149

-

【下载】高质量干货-22本高质量EMC电磁兼容性设计资料2020-03-20 5853

-

请问怎么才能设计出高质量的印制线路板?2021-04-23 1507

-

双目测宽仪高质量生产利器 测宽仪价格2023-12-04 3121

-

基于FPGA的高速高质量图像旋转2016-08-30 633

-

新思科技与GLOBALFOUNDRIES持续合作 推出高质量DesignWare IP2019-06-29 3759

全部0条评论

快来发表一下你的评论吧 !