通过利用现代处理器架构的并行性提高SDR的性能

描述

软件定义无线电 (SDR) 将是各种移动设备的绝佳选择,如果它不是那么耗电的话。SDR 可以安装在更节能的芯片组中吗?这是重新考虑架构以适应低功耗实现的案例。

对于许多已经在使用 SDR 实施的公司来说,使用汇编代码在低级别对处理器进行编程已被证明对于实现所需的性能水平至关重要。但是,使用汇编编程有两个主要影响:

1. 为一个处理器编写的代码在没有完全重写的情况下不能轻易地转移到同一处理器的另一个或未来几代。即使使用交叉汇编器也会导致翻译性能不佳。这对大型软件组件的可移植性有重大影响,导致成本和竞争力问题。

2. 这些汇编代码程序的创建需要大量的专家工程时间,并且对正在实施的处理器和算法都有深入的了解。这反过来又使该方法既昂贵又耗时,从而延迟了上市时间。

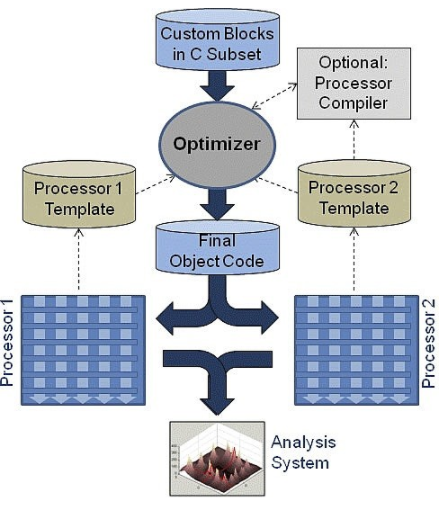

只有解决了可移植性和可编程性问题,MVR 才能在商业上运行。新兴的优化技术,包括 Sigmatix 的新技术,包括在其 MVR 基带平台中(如图 2 所示),以高性能方式打开了高级语言的使用。该技术利用对通常与综合技术相关的处理器硬件的理解,并将此信息用于并行化算法并将算法紧密映射到处理器架构上。使用 C++ 模板系统将算法描述编码为可以利用处理器提供的功能的形式,从而实现高性能的可移植性。

图 2: Sigmatix 的 MVR 基带平台支持实现更高性能和可移植性的方法。

在这种方法中,协议或基带设计工程师可以使用 C 代码来描述他们的算法元素,而无需考虑处理器架构。处理器工程师推动模板的构建,这些模板在处理器上提供原始数据,并酌情利用部分或全部随附的编译器技术。优化器结合了这两个代码库,修改输入代码以充分利用目标处理器架构来生成原始汇编代码或包含内在函数的已处理 C 代码,以指导进一步的编译步骤。然后针对处理器的周期近似模型运行二进制代码,并执行分析以检查可能导致代码库改进的常见性能问题。

下一代 MVR

SDR 已被证明对军事和商业无线基带实施很有价值,因为它的使用提供了更高的易用性、多模应用和控制多功能性。然而,与定制硬件相比,它的低性能水平阻碍了其在商用蜂窝手机等功率敏感应用中的普及。此外,高性能汇编代码实现缺乏可编程性和可移植性,这有损于它在更通用的基础设施应用程序中的使用。

MVR 通过利用现代处理器架构提供的多维并行性来解决这个问题,从而在不降低基于软件的设备的积极优势的情况下推动性能提升一个数量级。通过利用一种以便携和可编程方式保持性能的方法,MVR 代表了下一代基带设计的未来。

作者:Dave Kelf,Phil Moorby

审核编辑:郭婷

-

利用NI LabVIEW的并行化技术来提高测试的吞吐量2014-12-12 4666

-

怎么利用FPGA协处理器提高无线子系统的性能?2019-08-15 1500

-

Linux系统下超线程技术怎么提高处理器的性能?2019-09-19 2506

-

Python中的并行性和并发性分析2020-08-21 3364

-

阻止任务级别并行性的常见情况2021-03-09 11087

-

总线可重配置的多处理器架构2009-06-13 543

-

算法隐含并行性的物理模型2009-10-21 488

-

英特尔架构中的多线程优化和扩展并行性的编程技术2018-11-01 3296

-

英特尔至强融核处理器的基础知识2018-11-09 4447

-

矢量化数据并行性的程序方面的作用2018-11-06 3021

-

HPEC应用子程序线程推测并行性实验分析2021-03-30 944

-

浅析HLS的任务级并行性2023-07-27 1822

-

Vitis HLS:使用任务级并行性的高性能设计2023-09-13 530

-

现代处理器的主要指令集架构2023-12-11 6794

-

如何提高处理器的性能2024-01-24 4583

全部0条评论

快来发表一下你的评论吧 !