通过PCI Express桥接优化PCI读取性能

描述

PCI Express (PCIe) 现在是 PC 芯片组和嵌入式处理器上普遍存在的互连标准。尽管使用桥接器可以为现有 PCI 设备提供一种经济高效的 PCIe 升级路径,但由此产生的 PCI 读取会产生额外的延迟,从而严重影响系统性能。Craig 探讨了实施 PCIe 桥接器如何解决由 PCI 读取引起的性能问题。

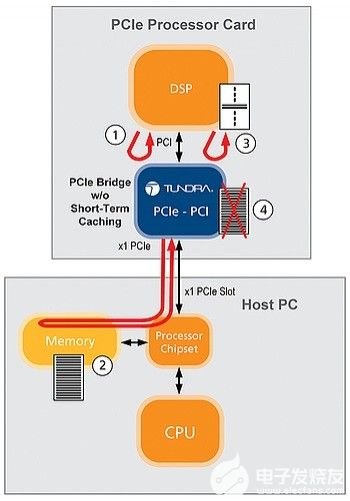

虽然 PCIe 正在取代原来的 PCI 总线标准,但许多外围设备和设备(例如 FPGA 和 I/O 模块)仍在使用 PCI。没有集成 PCIe 接口的组件需要从 PCI 总线到 PCIe 的桥接器。两个需要桥接的应用示例包括一个 PCIe 附加处理器卡,它使用基于 PCI 的 DSP 进行通信应用,以及一个嵌入式视频录像机,它使用带有 PCI 的 I/O 设备连接到带有 PCIe 端口的嵌入式处理器。

在这些系统和其他系统中,添加总线桥会带来设计挑战。性能通常取决于网桥的 PCI 读取性能。由于旧 PCI 协议的限制,一旦引入网桥,就会出现性能问题。使用市售的总线桥可以消除这些问题,从而最大限度地提高系统性能。

PCI 设备的繁重读取负担

PCI 总线上的设备通常严重依赖于从主机处理器读取大量数据。PCI I/O 设备通常控制系统中的数据移动,并启动对主机内存的读取和写入周期。例如,主机处理器可能通过写入外设上的寄存器来组织和协调数据移动,以在外设中设置 DMA 传输,但它会将自己从数据移动中移除以专注于其他任务。然后外围设备将读取或写入数据以服务于 DMA请求。在其他时候,处理器可能会读取状态信息并写入寄存器以进行控制。这种流量通常不涉及高带宽或显着有助于整体系统性能。

在处理器附加卡的情况下,它的 DSP 必须从主机 PC 内存中读取数据以进行数据处理或压缩任务。同样,诸如安全 DVR 之类的嵌入式处理系统将捕获和压缩将通过磁盘控制器写入磁盘存储的视频。 磁盘控制器通过PCI 总线从主机的内存中读取数据来实现这一点。

从 PCI 外设到桥接器的写入通常发布在内部写缓冲区中,以克服桥接器带来的固有性能损失。然而,PCI 读取会带来一些问题,因为 PCIe 桥必须重试外围设备,直到它从主机的内存中获得请求的数据。这通常涉及尝试读取许多小的 PCIe 数据包,从而增加延迟。

虽然 PCI-X 协议通过拆分事务绕过了这个问题,但传统的 PCI 协议并没有实现这个特性。 此外,一些 PCI 设备被设计为在接收到一到两条高速缓存行数据后自动释放总线,这加剧了 PCI 读取的性能挑战。

以 DSP 处理器卡应用为例。这个特殊的 DSP 使用 32 位 PCI 接口。与许多 PCI 设备一样,它会在释放 PCI 总线之前读取一到两条高速缓存行数据。在这种情况下,高速缓存行由 16 到 128 个字节组成,具体取决于系统设计和设备功能。

该卡将读取大量原始数据进行处理,例如在电信应用程序中处理的音频比特流。在DSP 直接通过 PCI 总线与主机处理器通信的传统系统中,读取性能将比添加桥之后更好,因为每个事务都有额外的延迟。

桥接引起的性能恶化

引入 PCIe 桥接器可能会对性能造成重大影响。这种读取性能下降可能通过以下过程发生(图 1):

1.DSP 将启动从 PC 主存储器的读取。网桥将锁定事务并继续重试,直到网桥接收到数据。

2.网桥将从内存中预取数据并将其存储在内部缓冲区中。

3.DSP 将读取一部分数据(一个或两个高速缓存行),然后断开连接,释放 PCI 总线。

4.一旦断开连接,网桥将丢弃其缓冲区中的所有剩余数据。随着DSP 启动下一次读取,桥将需要再次获取数据,重试直到数据可供 DSP 使用。

图1

在此示例中,步骤 4 在读取事务之间引入了显着延迟,这极大地影响了读取性能。 因此,与直接使用 PCI 总线相比,使用 PCIe 桥对读取性能的影响会大大降低系统性能。

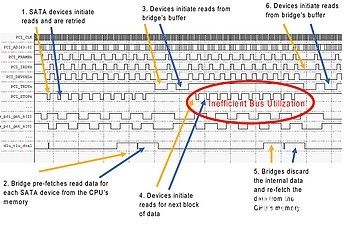

考虑另一种使用嵌入式 DVR 的常见情况。在这种情况下,系统必须将压缩视频数据的连续流写入磁盘以供存储和以后检索或分析。在这个系统中,一个或多个SATA 磁盘控制器将从系统的主存储器中读取视频数据,以存储在附加的磁盘阵列中。这些类型的系统可能包含额外的外围设备,例如共享 PCI 总线的以太网控制器。

与前面的示例一样,嵌入式 DVR 中的总线效率受到连续数据读取、总线断开以及多次重试和预取的严重影响,如图 2 所示。

图 2: DVR 系统中的 PCI 总线利用率

正如

指示正在读取数据的位置的 PCI_TRDYn(PCI 目标就绪)跟踪所证明的那样,第一次读取(步骤 3)和下一次读取(步骤 6)之间存在很大差距。这意味着将视频数据写入磁盘的最大速度显着降低,从而限制了系统性能。在这种情况下,最大限度地提高视频数据的写入速度对于最终产品至关重要,因为它能够存储监控所需的尽可能多的高质量视频通道。

解决问题:短期缓存

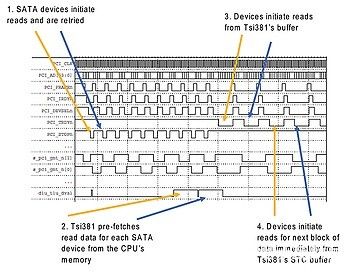

Tundra 的 PCIe 桥接器(Tsi381、Tsi382 和 Tsi384)集成了一种称为短期缓存 (STC)的功能,以帮助克服这一性能挑战。STC允许在初始 PCI 读取周期期间从连接的 PCIe 设备中预取数据,并临时存储在桥接器中,以便在后续读取周期期间快速周转。当请求的设备停止事务时,将在后续读取中读取的数据不会立即丢弃。

与最初的桥接情况相比,STC 对性能的影响可能是巨大的。以前面的嵌入式 DVR 为例,但系统中添加了 Tsi381 桥接器。通过启用 STC,后续读取不会因为它们保留在缓存中而延迟。此外,桥接器不必在第一次读取后从内存中重新读取数据,从而确保有效地使用总线(参见图 3)。

图 3:使用 Tsi381 和短期缓存的嵌入式 DVR 系统

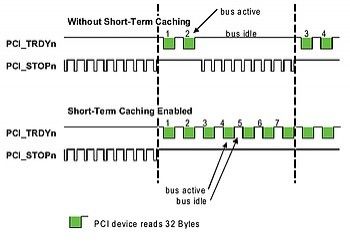

为了演示性能差异,请比较启用 STC 之前和之后的 PCI 总线时序(参见图 4)。在这个系统对每个设备执行 32 位读取的示例中,两个设备可以在没有 STC的情况下仅执行两次读取的同一时间段内执行七次读取。 因此,使用 STC可以将整体系统吞吐量提高三倍以上。对于具有执行此类读取的单个设备的系统,改进将更大。

图 4:启用短期缓存之前和之后的 PCI 总线时序

PCIe 桥接器允许开发人员通过调整以下参数来进一步修改系统:

数据保存在缓存中的时间。这允许设计人员确保陈旧数据一旦陈旧就被丢弃和预取。

PCI 读取预取长度。理想情况下,桥接器预取的数据不应超过 PCI 外设通常需要的数据,因此设计人员可以根据预期的典型传输长度设置此参数。

根据系统设计和设备行为,设计人员可以 通过调整预取长度和短期缓存丢弃定时器来提高整体性能或关键功能的性能。

桥接选项有助于消除瓶颈

使用 PCIe 桥接器将设计从 PCI 迁移到PCIe 的设计人员面临着相当大的设计挑战。PCI 外围设备启动的读取会引入额外的延迟,这对 整体系统性能有很大贡献。

Tundra 的 Tsi381 等 PCIe 桥接器为设计人员提供了调整桥接器的选项,从而提供最佳系统性能。使用 STC,这些桥接器可以轻松消除与 PCI 读取相关的性能瓶颈。

审核编辑:郭婷

-

PC通过PCI Express与FPGA通信2019-05-28 2865

-

PCI Express的基本工作原理2009-10-23 1644

-

PCI Express 至PCI 桥设计原理及应用2010-03-06 820

-

pci express总线概念2006-12-25 2325

-

PCI Express交换及桥接芯片的展望2009-02-09 6754

-

PCI Express插槽,什么是PCI Express插槽2009-04-26 5593

-

什么是PCI Express接口2009-12-25 3048

-

PCI Express总线2010-01-22 859

-

PCI-PCI桥在线读写EEPROM的技巧2011-06-03 2132

-

从PCI、PCI-X到PCI-Express之间的连接2012-06-05 4150

-

如何让PCIExpress至PCI接口TMS320DM646x通过XIO2000A桥接2018-04-18 1658

-

FPGA中实施PCI Express桥接解决方案2023-05-11 2100

-

PCI Express桥:指南上游内存读取性能优化2023-07-24 663

-

通过PLX PCI9080桥接芯片实现TMS320C6000扩展总线与PCI总线的接口2024-10-26 479

-

深入剖析XIO2001:PCI Express到PCI总线转换桥的卓越之选2026-01-08 372

全部0条评论

快来发表一下你的评论吧 !