FPGA设计满足可重新配置的计算需求

描述

可重构性——在系统部署后改变系统功能的能力——不仅可以帮助设计人员对最后一刻的设计变更做出反应,还可以让他们在实施之前对想法进行原型设计,并在现场升级设计。在当今瞬息万变的环境中,这种能力提供了巨大的竞争优势,并且通常每瓦系统功率可以完成更多的计算。Tom 探讨了 FPGA 设计的当前趋势如何提供更大的灵活性并满足即使是最苛刻的应用程序的要求。

随着应用程序变得越来越复杂,可重构计算必须不断发展,以满足行业不断变化的需求。灵活性对于满足不断变化的客户需求变得越来越重要,并且要求系统比以往任何时候都更强大。例如,信号处理应用程序必须继续跟踪和解释来自更远距离的信号,并合并来自多种类型传感器(如红外线和紫外线)的数据。

这些应用程序将需要不断提高的图像压缩水平和计算能力以及用于评估数据的增强智能。当然,天气建模和计算化学等传统性能计算应用也需要更多的计算能力。而且,随着电源和冷却问题越来越受到关注,图形处理单元 (GPU) 所需的 100 W 或更多功率在传统计算中心可能会出现问题,而在包括卫星和无人驾驶飞机在内的其他应用中可能会令人望而却步。

FPGA 通过提供可与新兴标准保持同步的灵活平台,直接满足可重新配置的计算需求。知识产权 (IP) 功能和可配置处理器加快了开发速度,而强大的新软件工具可减少延迟、增加带宽并减少门的使用。FPGA 实现了所有这一切,在低功耗运行和散热方面比其替代品具有显着优势。

提升性能的 IP 内核

今天,实现可重构计算的最简单途径之一是使用 IP 内核,例如可配置处理器,它可以提供可调整的缓存大小、乘法器、除法器、硬逻辑和自定义指令。一些可配置处理器还支持可自动转换为硬件的加速器,从而提高生产力并显着提高嵌入式软件性能。设计人员可以简单地添加外围设备或处理器来创建适合他们需求的精确设计。

这些处理器具有过时证明的额外好处;即使设备过时,设计也可以移植到新的芯片上,从而保护设计人员对软件的投资。然而,这些可配置的处理器从来都不是用来处理大量计算的。它们通常作为控制器为可重构计算应用程序增加价值,协调具有专用计算功能的专用块之间的交互。

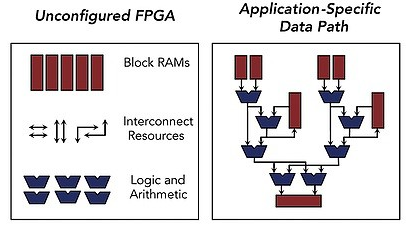

其他 IP 的开发正在进行中,例如可扩展、可配置处理和高性能计算架构,可满足定制数据路径、协议处理、数字信号处理和图像处理的需求(参见图 1)。这些功能允许工程师用定制的管道和并行数据路径代替顺序计算,以获得更高的性能和效率。软向量处理器目前也在开发中。

图1

通过并行加速

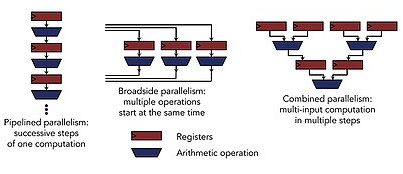

此外,与其他解决方案相比,FPGA 现在提供了更多的计算能力,而功耗却大大降低。可重构计算的关键是从传统的计算算法模型转变为在可配置计算结构中空间分布算法。速度不是来自快速连续执行许多操作,而是来自使用流水线、宽边并行或两者的组合并行执行操作(参见图 2)。FPGA 还允许设计人员定制流水线和内存访问模型,这些功能是 GPU 所不具备的。较高的带宽是通信应用中流数据的理想选择。

图 2

FPGA 加速器中的应用程序通常运行在 100 MHz 附近,但通过更多的设计工作可以达到更高的时钟速度。通过优化,FPGA 可以为利用其优势的应用实现令人印象深刻的加速,包括:

1000多个独立的硬件乘法器和算术单元的细粒度并行,所有这些都可以并发运行

低计算开销,索引和提取可以流水线化,操作数可以存储在独立的内存库中,终止测试可以与算术函数并行进行

具有 1,000 多个独立可寻址 RAM 缓冲区的内存并发性

快速、细粒度的通信以及以全芯片速度运行的片上通信,通常只有几个周期的延迟

浮点编译器提高效率

除了硬件,新工具现在解决了在设计中使用可编程逻辑的一些挑战。FPGA 始终在数据流架构中提供几乎无限的灵活性,因此提供了一种理想的方法来实现算术功能或通过卸载无法在处理器中最佳实现的数据路径来加速系统。然而,FPGA 以前在实现浮点运算的复杂性和精度方面遇到了困难,特别是对于双精度应用。

已开发出一种新的浮点编译器,可有效地将浮点数据路径映射到通用 FPGA 架构。这种浮点编译器通过将数据路径的大子部分融合在一起、对类似操作进行聚类以及优化连续运算符集群之间的接口来提高效率。

这允许多个精度(整数、单精度和双精度)存在于单个数据路径中,从而使通用 FPGA 与简单的基于组件的系统相比具有显着的效率优势。通用 FPGA 可在逻辑利用率上节省 50% 的典型逻辑,并类似地减少延迟,因此可以轻松支持浮点功能,并灵活地实现更广泛的运算符混合(例如加法器/减法器与乘法器的更大比例) ,同时保持处理能力以支持使用数据路径的应用程序。

可重构的优势

在当今技术和客户需求瞬息万变的世界中,在现场部署设计后增强功能的能力至关重要。借助最新的技术进步,包括更高的计算能力、更高的带宽、更低的延迟和更少的门使用,加上持续的双精度 GFLOPS/W,目前最高可达 1.5,可重新配置使用 FPGA 进行计算可以在竞争之前进入市场,并最终确保产品的成功。

审核编辑:郭婷

-

固化FPGA配置芯片的方式2024-10-24 2375

-

利用可采用电子方式重新配置的GaN功率放大器彻底改变雷达设计2023-02-22 1369

-

如何在xilinx FPGA中执行运行时重新配置?2020-07-16 1844

-

如何重新配置FPGA?2020-06-04 3289

-

如何使用GZip的比特流完成重新配置?2020-05-29 1278

-

测量部分重新配置的时间2020-04-02 1534

-

如何启用planAhead部分重新配置?2019-11-05 1370

-

如何重新配置执行ML555板?2019-08-22 1905

-

是否可以完全重新配置具有不同硬件门的FPGA?2019-04-11 1166

-

怎么使用内部配置访问端口来重新配置FPGA2019-03-26 3829

-

如何使用PowerPC或Microblaze重新配置FPGA?2019-01-22 2205

-

使用LabVIEW FPGA模块和可重新配置I/O设备开发测2009-07-23 742

-

[分享]用LabVIEW FPGA 模块和可重新配置IO 设备开发测量与控制应用 吗?2009-05-30 9194

全部0条评论

快来发表一下你的评论吧 !