富昌电子SiC设计分享(二):碳化硅器件驱动设计之寄生导通问题探讨

电源/新能源

3646人已加入

描述

作者:富昌电子 星空 校稿:富昌电子 萧峰

富昌电子(Future Electronics)一直致力于以专业的技术服务,为客户打造个性化的解决方案,并缩短产品设计周期。在第三代半导体的实际应用领域,富昌电子结合自身的技术积累和项目经验,落笔于SiC相关设计的系列文章。希望以此给到大家一定的设计参考,并期待与您进一步的交流。

上一篇我们先就SiC MOSFET的驱动电压做了一定的分析及探讨(SiC设计分享(一):SiC MOSFET驱动电压的分析及探讨)。本文作为系列文章的第二篇,将针对SiC MOS产品在驱动设计时遇到的寄生导通问题做出详细的分析,从元器件以及应用层面给出一些设计建议,并结合阈值电压的漂移问题做出简单的说明。设计者在实际应用时,需要根据产品的本身定位在二者之间做一个平衡。

1. 寄生导通产生机理

以下主要探讨关于SiC器件驱动回路设计的要点,而如何选择合适的门极驱动电压也是整个驱动器设计的关键。对于开通来说,通常选择门极15V或18V作为门限值,从而可以配置为具有较好的载流能力或者具有很好的短路耐用性。对于关断来说,通常使用负电压关断最为保险,可以有效的保证可靠关断,减少误触发的机率。

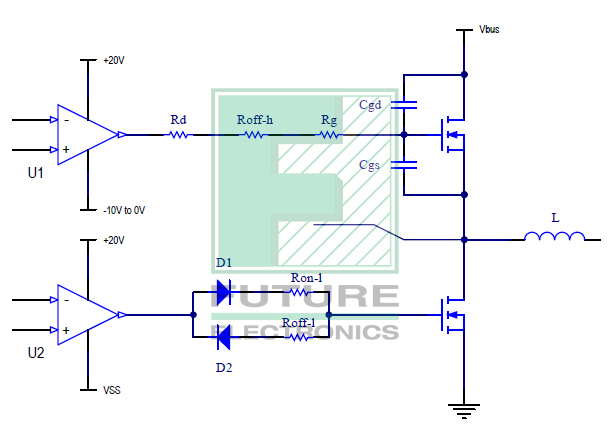

对门极的电容反馈有可能会导致半导体器件产生误导通动作。而如果使用的是SiC器件,那么通常需要考虑米勒电容所带来的电容反馈。由米勒效应带来的电容反馈可能会导致管子的误动作,更有甚者可能导致上下管直通,引起短路现象的发生,以至损坏功率器件,其产生的具体机理可参考下图:

在半桥电路拓扑应用中,当低边开关Q2导通时,高边开关Q1的电压变化dVDS/dt。因此,形成了对上管的寄生电容Cgd的充电电流iT。该电流通过米勒电梯Cgd,门极电阻以及电容Cgs形成回路,并对Cgd进行充电 (电容Cgd和Cgs形成一个对VDS进行分压的电容分压器)。当在门极电阻上的电压降超过了上管Q1的阈值开启电压,这时候就发生了所谓的米勒导通或者米勒效应。在此过程中,不断上升的漏极电位通过米勒电容Cgd 上拉Q2的门极电压。然而,门极关断电阻试图抵消且拉低电压。但是如果电阻值不足以降低电压,那么电压可能会超过管子的阈值电压,从而致使误触发的可能性,进而导致故障发生。甚至可能损坏SiC器件。

由误触发导致事件发生的风险和严重程度主要取决于特定的操作条件和测试硬件。高母线电压,电压快速上升以及高结温是比较关键的点。这些条件不仅会严重地上拉门极电压,而且会降低阈值。硬件相关的主要影响包括:MOS管内部寄生电容Cgd,Cgs以及门极关断电阻等。

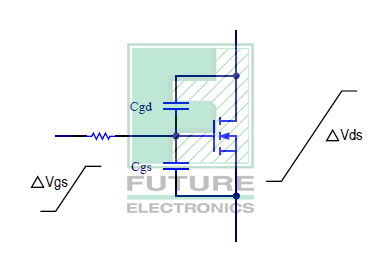

由Cgd和Cgs电容所引起的寄生电压会导致门极误开通的可能性,进而增加整个开关损耗,造成器件损坏风险。参考下图:

2. 如何减少寄生导通带来的误触发

为了减少器件误差发的概率,提升产品的可靠性,我们可以从器件层面和应用层面触发,考虑对应的措施和方法。

A. 从应用层面上考虑

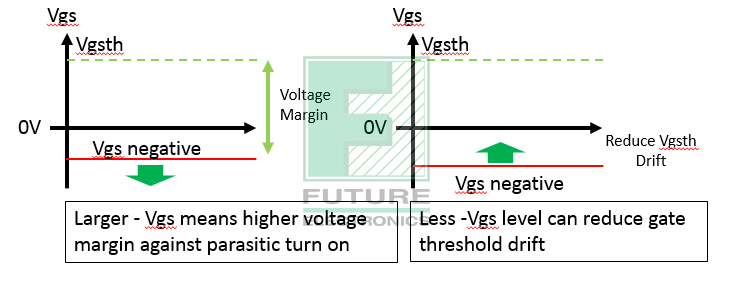

1. 增加负压关断电压Vgs off

即使有寄生电容带来的电压△Vgs,当使用负压Vgs off来驱动时,可以抵消部分△Vgs ,从而使得△Vgs小于门限电压Vgs(th)。从而避免误差发的可能性。

富昌设计小建议: 需要综合考虑MOS管的寄生参数以Vgs 裕量来选择合适的电压,以确保产品的可靠性。

2. 使用带米勒(miller)钳位的驱动

在设计驱动时,可以考虑采用带米勒钳位的驱动产品,从而可以有效钳制门极电压,使门极电压不超过开通阈值电压,避免误触发的风险。

富昌设计小建议:可以根据实际应用需求,选择带有米勒钳位或Desat保护的驱动芯片,从而简化系统设计。

B.从器件选型上考虑

1. 采用较高开通门限值Vgsth的器件

使用较高开通阈值门限电压的器件,可以有效低降低误差发的可能性。

2. 使用合适变容比Cgd/Cgs的器件

通常来说,在器件选型时,可以根据寄生参数,选择合适变容比的SiC产品,可以有效地降低误触发的风险。

一条粗略估算VGS 裕量的经验方法可供参考,对于600V的SiC产品,最好是选择变容比大于150。即Cgd/Cgs>150。此时可计算出△Vgs<4V。(注,由于各家工艺技术的不同,门限电压也不尽相同,所以并不适合所有的产品。此处仅参考英飞凌的产品)

富昌设计小贴士:此处参考的是英飞凌SiC产品,其门限电压通常在4.5V左右。

3. VGS 裕量与VGSTH 漂移的平衡

通过上面的计算和分析可知,虽然增加Vgs off负压可以降低误触发的风险,但是也不是越大越好,因为这会带来门限电压的漂移,且负压越大,由此带来的VGSTH漂移也越大。所以在设计时需要综合考虑二者,寻求一个合理的平衡点。以下示意图描述了这一点。

富昌电子在本文中,主要针对驱动设计时的寄生导通问题做了详尽的分析和探讨。并从器件选型和应用层面上分别给了几点建议。最后就VGS裕量以及VGSTH漂移做了简单的阐述,由于二者是对立的,实际应用中需要综合考虑两者之间的利弊关系,做出平衡选择,这样既能充分发挥SiC器件的特性,又能保证整个产品的可靠性。

如您对碳化硅(SiC)产品/系统的设计存有任何疑问,欢迎您点击以下链接,或是扫描二维码,与富昌电子的技术团队取得联系:

https://www.jsform.com/web/formview/6286e84a75a03c5d1e0da67b

参考文献:

【1】分立式CoolSiC Mosfet 的寄生导通行为 Klaus Sobe, 英飞凌科技有限公司(奥地利).

【2】1200 V SiC MOSFET and N-off SiC JFET performances and driving in high power-high frequency power converter – Bettina Rubino, Luigi Abbatelli, Giuseppe Catalisano, Simone Buonomo, PCIM Europe 2013.

【3】Direct Comparison among different technologies in Silicon Carbide - Bettina Rubino, Michele Macauda, Massimo Nania, Simone Buonomo.

【4】Direct Comparison of Silicon and Silicon Carbide Power Transistors in High-Frequency Hard-Switched Applications - John S. Glaser, Jeffrey J. Nasadoski, Peter A. Losee, Avinash S. Kashyap, Kevin S. Matocha, Jerome L.

【5】CoolSiC Mosfet 1200V TTA 2020

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 富昌电子

- SiC

- 驱动设计

- 碳化硅

- SiC MOSFET

-

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?2025-01-04 2654

-

SIC碳化硅二极管2016-11-04 5623

-

碳化硅(SiC)肖特基二极管的特点2019-01-11 8365

-

碳化硅的历史与应用介绍2019-07-02 5072

-

碳化硅深层的特性2019-07-04 6123

-

碳化硅二极管选型表2019-10-24 1924

-

碳化硅半导体器件有哪些?2020-06-28 4462

-

碳化硅基板——三代半导体的领军者2021-01-12 4457

-

什么是碳化硅(SiC)?它有哪些用途?2021-06-18 9427

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6185

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2973

-

碳化硅MOSFET是如何制造的?如何驱动碳化硅场效应管?2023-02-24 12602

-

碳化硅SiC技术导入应用的最大痛点2023-02-27 1896

-

在开关电源转换器中充分利用碳化硅器件的性能优势2023-03-14 2897

-

碳化硅SiC MOSFET:低导通电阻和高可靠性的肖特基势垒二极管2023-04-11 2296

全部0条评论

快来发表一下你的评论吧 !