基于ADF4111的数字锁相式可调频率源实现

通信设计应用

描述

频率合成技术是指能由一个高稳定度和准确度的标准参考频率,经过一系列的处理,产生大量离散的具有同一稳定度和准确度的信号频率输出,并且输出信号的频率可由数字信号控制改变,它主要的应用是为上/下变频的中频或射频信号提供本振。频率合成的基本方法有三种:直接频率合成、锁相式频率合成以及直接数字频率合成。锁相式频率综合器是现今应用最为广泛的一种频率综合器,它具有输出频率范围大,杂散抑制特性好的特点。

在短波数字接收系统中,从天线端接收到的短波信号与本振信号混频得到70 MHz中频,之后对中频信号进行带通采样。本振信号的稳定性和准确度对系统性能有着重要和直接的影响。本文采用频率合成技术,应用ADl公司的频率综合器ADF4111和Altera公司的FLEXlOKE系列FPGA实现频率稳定,精度高,范围为70~90 MHz,步进间隔1 MHz的数字锁相式频率源本振。

1 锁相环基本原理

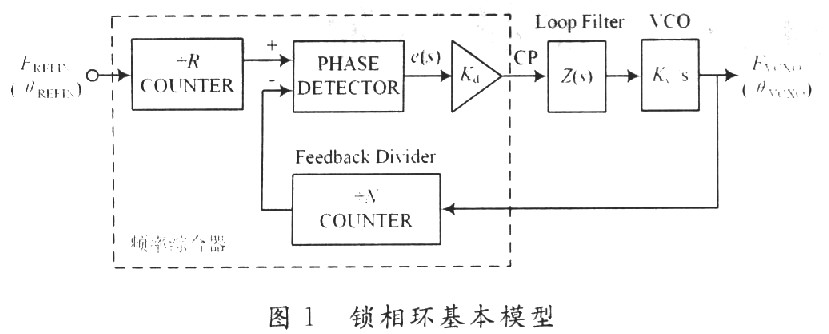

锁相环(PLL)是一种建立在相位负反馈基础上的循环控制系统,如图1所示。一个锁相环由以下四部分组成:

(1)R分频因子,鉴相器(Phase Detector),充电泵(Charge Pump)。

(2)环路滤波器,一般是低通滤波器,其作用是对充电泵的电流输出进行滤波,以驱动压控振荡器,其传输因子为Z(s);

(3)压控振荡器,有一个频率灵敏度Kv/s;

(4)反馈分频因子N。

它以一个高准确度,稳定度的晶体振荡器的R分频作为输入参考频率,该输入参考频率作为鉴相器的基准与压控振荡器输出的进行比较,产生一个对应于两个信号相位差的电流脉冲。该电流脉冲经环路滤波器积分产生一个控制电压,并滤除其中的高频分量和噪声,这个电压驱动压控振荡器(VCO)的输出频率增加或减少。当环路锁定时输入参考频率与压控振荡器输出的N分频的频差为零,相位差不再随时间变化。这时控制电压为一固定值,环路进入锁定状态。

当输入的参考时钟fREFIN,压控振荡器的输出fVCXO两个频率分别经R和N分频后的频率和相位均相同时,鉴相器的输出e(s)为O,此时环路将处于锁定状态。由方程e(s)=FREFIN/R-FVCXO/N可以推导出,当e(s)=0时,fREFIN/R=FVCXO/N,即FVCXO=NFREIN/R。

锁相式频率综合器将R,N分频因子、鉴相器、充电泵集成于一个芯片内,对相位噪声和杂散等具有很好的抑制作用,而且调试简单。它作为通信、雷达、遥测遥控、电子侦察等系统中的核心部件,是保证整个电子系统性能的关键因素之一,因而目前被广泛应用于电视、仪表、通信等许多领域。

2 数字锁相式频率源设计方案

根据系统需求,数字锁相式频率源设计指标主要为:输出频率为70~90 MHz;步进间隔为1 MHz;输出功率为9 dBm。为了满足这三个主要指标,设计从以下三方面考虑方案的设计和器件的选用。

2.1 输出频率

为了得到输出范围为70~90 MHz的高精度频率,设计中采用ADI公司推出的高性能锁相频率综合器芯片ADF4111,其RF回馈输入的最高频率为1.2 GHz,即为锁相环路可得到的最大输出频率,满足本设计频率输出范围要求。该芯片可用于无线射频通信系统基站、无线局域网、手机,以及通信检测设备中。它主要由四部分构成:

(1)低噪声鉴频相器(PFD)。

(2)精密充电泵(Charge Pump)。

(3)可编程预置分频器。主要由三个可编程计数器组成:A计数器(6位)、B计数器(13位)、双模预置分频器(P/(P+1),P为预置分频器的模),这三类计数器执行VCO输出频率到PFD的N分频,实现N=BP+A的运算;其中双模预置分频器有四种工作模式:8/9,16/17,32/33,64/65;

(4)参考分频器(R计数器,14位)。

使用时需要配置寄存器,寄存器配置除了配置芯片工作方式外,主要是设置输入时钟分频因子R和VCXO输入分频比A,B,使鉴相器的两个输入时钟相等。VCXO输出的时钟与输入时钟关系为:FVCXO=[(P×B)+A]FREFIN/R。式中:P为prescaler因子;FREFIN和FVCXO分别是输入的参考时钟频率和压控振荡器的输出频率。

寄存器的配置可采用FPGA控制的方法。FPGA因其集成度高、功能强大、用户可编程、体积小等特点被应用得越来越广泛。在该设计中其对寄存器的配置也显得灵活而方便。设计中选用Altera公司的0.25μmCMOS ROM工艺规程的结构的FLEX系列芯片EPFlOK50EQC240-3,FLEX系列的芯片是一种中等密度的器件,基于查找表结构,性能高,功耗低。FPGA的程序开发使用的是Altera公司的QuartusⅡ软件实现的,用AHDL硬件描述语言编写ADF4111的寄存器配置程序。

与频率综合器ADF4111构成锁相环的压控振荡器选用了Mini-circuit公司POS-100,它是一款性能优良的压控振荡器,其调谐电压范围是0~16 V,对应的输出频率范围为45~110 MHz,电压调节灵敏度为4.2~4.8 MHz/V,输出功率的典型值为8.3 dBm,从其电压一频率关系得知,当输出频率为90 MHz时,对应的输入电压在11.5~12 V之间,而当给ADF4111的模拟和数字供电端加3.3 V电压,电荷泵供电端加5 V电压时,电荷泵输出经环路滤波器后的电压最高为5 V,该5 V电压若不放大,显然无法驱动压控振荡器产生90 MHz的频率。为此,在环路滤波器后需要添置一个放大器,OP191是AD公司一款供电电压为2.7~12 V的放大器,主要应用在工业控制,电讯,远程感应等领域,将它的供电电压设计为12 V,可以使其输出电压最高达到12 V,能够满足压控振荡器输出频率为90 MHz的调谐电压输入要求。

2.2 频率步进

实现频率步进的方法是通过改变频率综合器ADF411l的寄存器配置值,从而调整压控振荡器的输出频率以达到环路的锁定,最终实现压控振荡器输出频率的步进。

频率的步进既要使VCO输出频率升高又能使其降低,故设计中,采用两个按键分别发起升高和降低的指令要求,并通过FPGA用AHDL编程实现相应的对ADF411l寄存器配置的指令。

2.3 输出功率

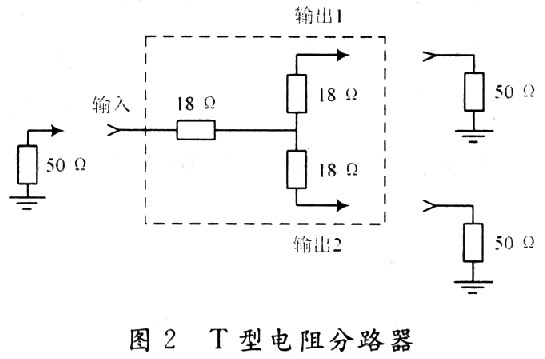

根据信号流程,压控振荡器POS-100的输出分为两路:一路反馈于ADF4111,另一路作为本振输出。此时,压控振荡器的输出需要经过一个T型网络分成两路,这里T型网络是一个电阻分路器,如图2所示。它广泛应用于一个源需要驱动两个负载的情况,其目的是进行电路的阻抗匹配。常用三个18 Ω的电阻值连成Y型。如果其中的一个负载为50 Ω,它就相当于衰减6.3 dB的T型网络。

压控振荡器POS-100输出功率的典型值为8.3 dBm,经过T型网络后,作为本振输出的信号功率为8.3-6.3=2 dBm,显然2 dBm的信号需要放大,因此设计中采用Mini-circuits公司的单块集成电路放大器ERA-4。它能够放大的信号频率范围为0~4 GHz,对0~1 GHz信号的放大增益为14 dB。为确保ERA-4的本振输入信号不饱和,设计中将2 dBm的本振信号经过了一个4 dB的衰减器后再输入ERA-4。此时,从ERA-4输出的本振信号功率为2-4+14=12 dBm。最终,为得到9 dBm的本振输出,需要再将ERA-4输出的信号衰减3 dB。衰减器的设计采用兀型电阻匹配网络。

系统中,FPGA的工作时钟和频率综合器ADF4111输入参考时钟由美国WINTRON公司的40 MHz的TCXO时钟提供。

3 数字锁相式频率源硬件设计

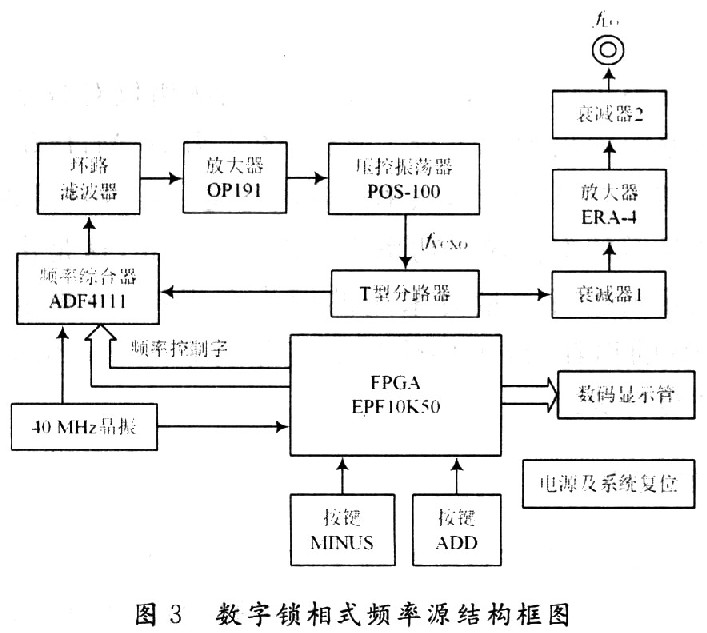

根据数字锁相式频率源设计方案,设计的硬件结构如图3所示。

作为系统的逻辑控制中心,FLEXlOK50E芯片内部集成有50 000个门,2 880个逻辑单元(Logicelements),其RAM容量为40 960 b,它完成的功能主要有:

(1)接收按键的对输出频率fVCXO增减要求的指令;

(2)配置频率综合器ADF4111;

(3)控制数码显示管以显示锁定后的fVCXO值。

锁相环路的设计是保证系统能够产生稳定,高精度的本振输出的关键。从压控振荡器输出的本振必须经过衰减器和放大器,以确保最终的本振输出功率符合指标要求,下面重点阐述这两部分的电路设计。

3.1 锁相环电路设计

锁相环电路设计主要有两部分:ADF4111设计和环路滤波器的设计,下面分别对这两方面进行阐述。

3.1.1 ADF4111设计

ADF4111内部的四个24位控制字寄存器,分别为R分频器、N分频器、功能寄存器和初始化寄存器,FPGA对锁相环的控制通过设置这四个控制寄存器的控制字来实现。

ADF4111从外部输入的信号有标准频率源信号(40 MHz)和FPGA输出的控制信号。标准频率源信号输入到ADF4111后,经14位的R分频器得到鉴相基准频率并送至鉴相器。控制信号由时钟信号CLK、数据信号DATA和使能信号LE组成。在CLK的控制下,由DATA信号端输入24位数据信号,暂时存放在24位输入寄存器中。在接收到LE后,先前输入的24位数据根据地址位到达对应的锁存器。当ADF4111接收到反馈回来的输出频率后,首先通过预分频比例因子P,经A,B分频器,得到分频以后的回馈信号,之后输入到锁相器。与分频以后的标准频率源信号在鉴相器中比较,输出低频控制信号以控制外部VCO的频率,使其锁定在参考频率的稳定度上。

设计中采用40 MHz晶振作标准频率源信号。为了得到1 MHz的步进量。ADF4111的PFD输入频率为l MHz。所以将参考时钟分频器R设置为40,此外,设置P=8。由关系式:FVCXO=[(P×B)+A]FREFIN/R知,当FVCXO=70 MHz时,可以设置计数器A为6,计数器B为8,则4个控制寄存器的控制字分别设置为R分频器6200AOH,N分频器200819H,功能寄存器003092H,初始化寄存器003093H。当按键发出指令,要求升高或降低本振输出频率时,改变计数器A和B的值,并重新加载ADF411l的控制寄存器,最终实现本振输出频率的改变。

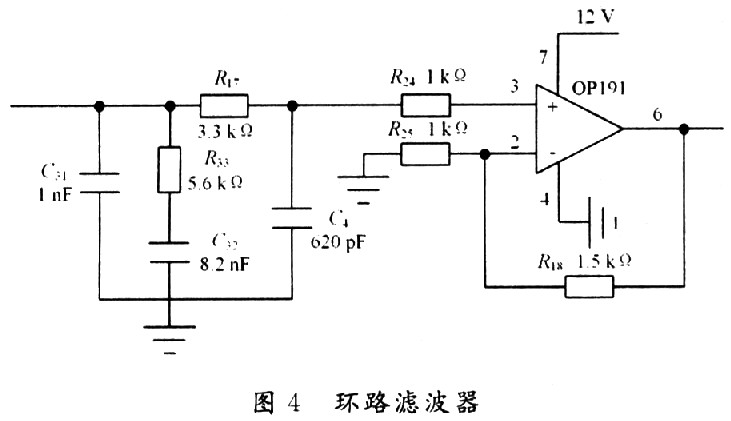

3.1.2 环路滤波器设计

环路滤波器的设计要求比较严格,其优劣直接影响锁相环的稳定性,可以利用AD公司提供的专用软件ADI simPLL 3.0进行了滤波器的设计,仿真软件提供了ADF系列频率合成器的集成环境,它包含了ADI频率合成器模型,VCO和TCXO的模型。可以选择相应的参数来设计所需要的环路滤波器。它同时给出参考相位噪声,输出杂散及锁定的过程。

环路滤波器的带宽越宽,锁定时间越短,但杂散噪声增加。环路滤波器的带宽越窄,杂散噪声减小,但锁定时间增长。因此环路滤波器的带宽选择需在这两者之间折中。设计中带宽选为鉴相器参考频率的1/10即能兼顾这两个因素。环路滤波器还需考虑的一个因素是相位余量,相位余量太小会导致系统不稳定,相位余量太大会使整个系统变慢,40°~55°是比较理想的选择,在这个范围内,一定的杂散度下,能使锁定时间达到最小。设计中设定滤波带宽为100 kHz,相位余量45°,用ADI SimPLL 3.O仿真软件可以得到环路滤波器的设计和仿真结果,电阻值和电容值根据最终的调试做了相应调整。设计的电路如图4所示。

3.2 衰减器设计

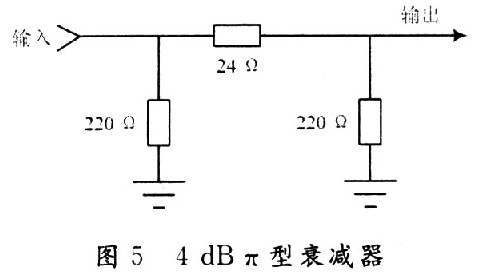

为确保最终的本振输出功率符合指标要求,进行衰减和放大电路部分的设计。该设计中衰减器采用了π型电阻网络,该电阻网络既要满足功率分配要求。又要满足阻抗匹配要求,在衰减器的输入和输出阻抗均为50 Ω时,利用CASCADE(Comptlter Aided ScientificAmplitier Design Element)软件设计的4 dB衰减器如图5所示。

4 数字锁相式频率源硬件和软件调试

在完成频率源的软硬件设计之后。需要进行系统调试。调试包括硬件调试和软件调试两部分。

4.1 系统硬件调试

在完成系统硬件电路设计和PCB制作后,需要利用万用表、示波器、频谱仪等工具对系统进行调试,来验证设计是否达到系统设计的要求,有无电路方面错误等。硬件调试主要包括数字锁相环调试,上电前检测、上电后检测和模块各组成部分工作状态调试等。

在设计中,通过USB-Blaster下载电缆采用JTAG配置方式将数据下载到FPGA。下载配置是验证系统中其他电路部分的第一步,方法是通过QutartusⅡ软件设计一些简单的逻辑电路,然后下载到FPGA中,通过示波器等工具检测输出的波形是否正确。

4.2 系统软件调试

该设计中,在FPGA内用AHDL硬件编程语言实现了软件设计部分,主要分为两部分:一是对ADF4111寄存器的配置;二是实现按键对锁相频率升高和降低的要求。该设计中,利用数字示波器的触发采样功能来捕获FPGA配置ADF4111寄存器的各个管脚的时序逻辑。

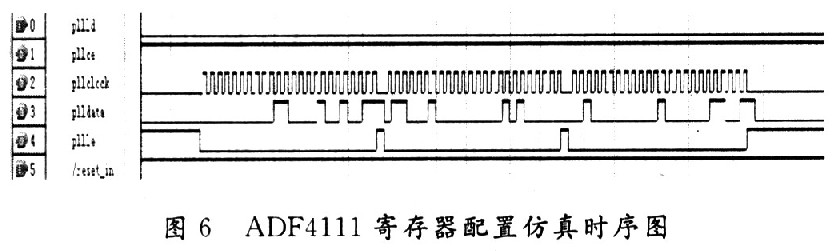

ADF4111需要配置的寄存器为3个24 b的寄存器,在Altera公司的QuartusⅡ平台上用AHDL进行编程配置的仿真时序如图6所示。其中,R=40,A=6,B=8,P=8。

ADF4111有一个复用输出管脚(muxout),通过该管脚可以查看寄存器配置是否正确。设计中设置该引脚输出为PLl锁定指示,并连接到发光二极管。配置完后,若指示灯亮,则说明配置正确,PLL锁定在输入时钟上。调试中配置完ADF4111后,PLL成功锁定设置的频率上。

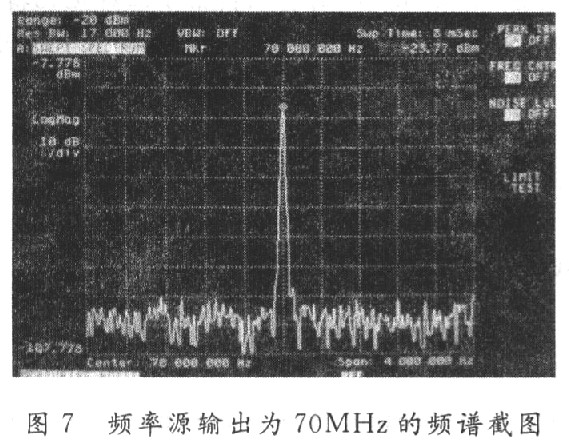

在整个设计和调试完成之后,用频谱仪对数字锁相式频率源输出频率进行了测试,图7为70 MHz输出时的频谱图,可以看出,频率源输出稳定。需要注意的是,截图显示的本振输出功率为-23.77 dBm,这是由于对本振输出进行测量时采用的探头有损耗,经测量约有33 dB的损耗,故本振输出的实际功率为9 dBm,达到系统设计要求。

5 结语

本文采用FPGA与频率综合器ADF4111相结合的方法进行了数字锁相式频率源的设计,在FPGA内用AHDL硬件描述语言编写频率综合器需要的频率控制字程序,产生范围为70~90 MHz的高精度频率,频率的步进采用按键控制的方法,步进的间隔为1 MHz,并通过数码显示管将锁定后的频率值显示出来。完成了PCB板制作,进行了硬件和软件调试。通过ADF4111的复用输出管脚(Muxout)看到PLL成功锁定设置的频率上,并用频谱仪测量了产生的频率,输出频率稳定,精度高,功率符合设计指标要求。实现了PLL输出频率的步进,间隔为1 MHz。并在数码管上将锁定后的频率值显示出来。

在该系统中,由于ADF4111的控制字寄存器的控制字是通过FPGA写入的。所以可以通过软件设计的方法,改变写入的控制字来实现不同频率的本振信号输出,使锁相环具有低相位噪声,低杂散度。快速锁定的特点,电路简单,易于调试。采用这种方法能可根据实际工程需要改变输出信号的频率。步进间隔以及功率,使该类型电路设计能广泛应用于无线通信设备中,为设备的中频和射频电路提供高质量的本振。

-

ADF4110/ADF4111/ADF4112/ADF4113:高性能RF PLL频率合成器的详细解析2026-04-20 225

-

EVAL-ADF4111 EVAL-ADF4111评估板2021-07-25 216

-

ADF4110/ADF4111/ADF4112/ADF4113:RF PLL频率合成器数据表2021-04-29 940

-

如何采用ADF4111实现数字锁相式可调频率源的设计?2021-04-14 1054

-

如何使用ADF4002和ADF5355芯片实现5G毫米波通信系统的本振源设计2020-11-11 1415

-

怎么实现数字锁相式可调频率源?2019-08-16 1480

-

ADF4111 单通道、整数N分频、1.2 GHz PLL,内置可编程预分频器和电荷泵2019-02-22 640

-

采用FPGA与ADF4111实现数字锁相式频率源的设计2019-02-06 3271

-

请问ADF4351能做数字锁相环实现位同步吗2018-09-14 2644

-

基于GPS秒脉冲的频率源设计与实现2017-12-07 1427

-

数字锁相环ADF4351原理详解与合成频率源的设计2017-11-15 43673

-

关于ADF41112014-04-27 2208

-

基于ADF4111的锁相环频率合成器设计2013-01-10 1293

全部0条评论

快来发表一下你的评论吧 !