D触发器为什么能对数据延迟一个时钟周期

描述

D触发器在FPGA里用得很多,但我经常无法理解D触发器为什么能对数据延迟一个时钟周期(打一拍)。下面从信号处理的角度来谈一下我的理解。如发现理解有误,烦请留言指正。

D触发器形如:

`timescale 1ns/1ps

module d_flip_flop(

input clk,

input rst_n,

input d,

output reg q

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

q <= 1'b0;

end else begin

q <= d;

end

end

endmodule

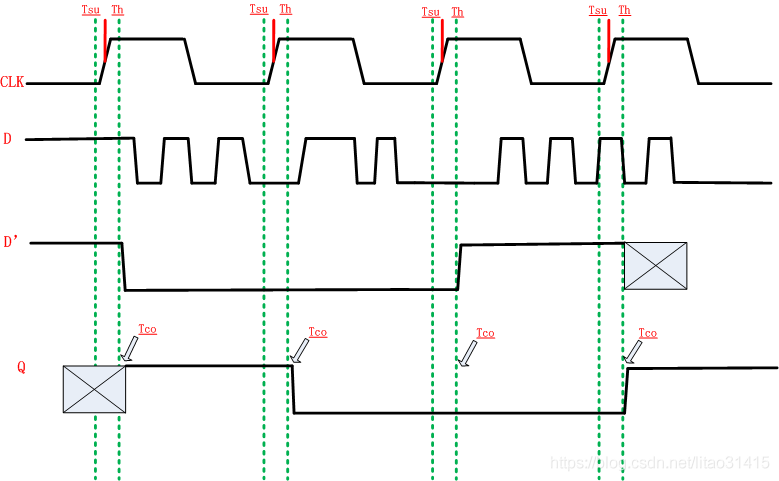

时序图如下:

解读如下:

D触发器在时钟CLK上升沿采样,数据D在建立保持时间Tsu和Th内需要稳定不变,否则出现亚稳态!我们在这个时间“窗口”内采样到的数据即为D触发器采样到的数据,经过Tco(其中Tco < Th)的时间后,D触发器就会输出上述采样到的数据D,并且该数据会保持一个时钟周期T不变。

为什么会有延迟一个时钟周期(打一拍)的效果呢?原因是,如果两个D触发器分别对D和D’这两个数据采样,则这两个触发器输出的结果将会一致的,即均为上图的Q!对比D’和Q会发现:Q比D’延迟了一个时钟,所以才会说对信号D延迟了一个时钟周期。

D触发器是无法识别数据D在时钟上升沿后肆意变化的那部分(因为D触发器在非触发沿时是保持输出不变,而不会再采样数据的),所以才导致在D触发器看来D和D’是一模一样的信号!!

最后,有如下结论:

1.数据D在建立保持时间窗口内必须保持稳定,D触发器采样到的就是该稳定数据。

2.D触发器采样后,经过Tco时间后即可输出到Q

3.保持时间过后,如果数据变化了,D触发器无法感知

4.Tco < Th,且 Th很小,均由fpga器件型号决定

根据前3条,我们可以在仿真时认为,D触发器一直对CLK上升沿左边的信号进行采样,并保持一个时钟周期T的时间,因为一直采样的是前一刻(上一个T)数据D的值,并且保持T,所以长远来看,D触发器对数据D延迟了一个时间周期!

原文标题:如何理解D触发器延迟一拍

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

d与rs触发器间功能的转换2024-08-28 3358

-

d触发器和jk触发器的区别是什么2024-08-22 5723

-

d触发器的功能 d触发器的状态方程2024-02-18 18425

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 6365

-

D触发器,请查收!2023-12-04 4281

-

用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器?2023-08-24 6350

-

rs触发器r和s分别是什么意思 基本RS触发器的四种状态2023-08-17 21851

-

什么是D触发器,D触发器如何工作的?2023-06-29 52257

-

D触发器不同应用下的电路图详解2023-01-06 10241

-

D触发器的结构特点、工作原理及主要应用2022-10-11 177708

-

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?2022-01-25 10700

-

图文并茂:D型触发器电路设计教程2021-02-03 14131

-

D触发器,D触发器是什么意思2010-03-08 5401

-

D触发器2008-10-20 3210

全部0条评论

快来发表一下你的评论吧 !