计数器分频怎么个不稳定法 FPGA生成的DDS数据如何导出到matlab中

电子说

描述

【问题1】如何知道ddr3里不空,可以读取了?

答:DR3和RAM一样,是一个存储器件,它的每个内部单元都存储了当前的数据状态值。

但DDR3和RAM本身,是没有“空”、“存有数据”,“数据满”等概念的。只要给地址,它就会把当前地址的数据给到总线上,而且这个地址可以读很多次。

在设计的时候,是由设计师用自己写逻辑来判断DDR3是否为空。

【问题2】SPI多字节发送是多个字节连在一起发还是分成单字节来进行发送?

答:每款芯片的数据手册,都会有时序图的介绍,需要按照芯片数据手册的要求进行通信。每款芯片的要求都是不同的。所以,您需要查阅数据手册。

【问题3】如何避免竞争和冒险的情况?

答: 竞争和冒险是由于组合电路中计算的延迟不一致而导致的。它是天然的、不可克服的现象。虽然它不可克服,但在FPGA设计里,它根本就不是一个问题。

因为FPGA都是在D触发器的时钟上升沿对电路进行采样,只要时钟上升沿前,电路计算结果已经确定,竞争和冒险已经没有了,那就不会有问题。

那设计时,如何确认时钟上升沿前,计算结果已经确定了呢?

这就靠时序报告了:时序报告会告诉任何两个D触发器之间,它们电路延时之和,从而确认在上升沿之前计算结果确定。

总而言之,设计时不用考虑竞争和冒险;设计完看,看时序报告;没有问题,那就正常;如果时序报告有问题,就解决时序问题。

【问题4】计数器分频怎么个不稳定法?

答:1. 时钟在FPGA里是非常重要的,所有的寄存器都是统一在时钟的节拍下工作。这个时钟就相当于一个军队的司令部,寄存器都听从司令部的命令下工作。

2. 一个稳定的系统,时钟是越少越好。就相当于,一个军队,司令部越少越好。如果司令部越多,那么部队之间的协作必须要增加流程和成本。

3. 计数器分频的时钟,无形中增加了时钟个数,另一方面,就相当于弄一个自己独立的王国,自然就不稳定。

【问题5】仿真是正确的,但为什么上板就不行?

答:首先要明确,仿真可以而上板不行,这是属于研发过程中,非常非常之正常的现象,可以说仿真通过后,上板一次性就成功的概率,小之又小。

原因是:仿真只是用电脑模拟运行的情况,它与真实情况可能有所差别。例如:

1. 输入激励是您想象出来的,事实上是不是这样输入?

2. 您的代码是否可以综合出电路?

3. 您的仿真是否测试完所有的情况?

以上都表示了仿真和实际是有差距的,所以不能认为“仿真正确了,上板就正确”。

【问题6】:管脚未分配的现象,老师,我把CPLD的一个引脚接到了LED灯,但是程序中没有分配这个管脚,第一个版本的程序上电后这个LED灯一直是亮的。

第二个版本上电后LED一直是灭的。这两个版本的程序,都没有对这个管脚分配,是什么原因导致的呢?

答:管脚如果未分配,则管脚电平值可认为是不可控,也就是随机。

【问题7】:FPGA资源不足问题当程序所使用的资源,超出FPGA芯片资源时,如何处理?

答:

1. 按照错误提示,判断是哪种资源不足,如管脚数、RAM、寄存器等。

2. 阅读资源QUARTUS、ISE和VIVADO的资源报告,查看是哪些模块占用了哪些资源。

3. 分析该项目程序中各个模块的资源占用情况,分析代码,综合运用多种方法,以求减少资源的使用,如速度换资源;去除冗余的逻辑;降低设计精度;速度换资源等方法。

注意,这些都需要 花费大量时间,一点一点去抠资源。

4. 如果资源依然不足,可以考虑换更高级的芯片;或者改变功能需求等。

【问题8】 就是lvds恢复出数据和时钟,对齐是需要手动调节时钟相位,还是写代码自动调节?serdes

答:我们做法是手动调节相位对齐。理论上,任何功能都可以使用代码来调节,只是有没有必要以及复杂度而已。

【问题9】FPGA生成的DDS数据如何导出到matlab中

答:

1. 可以通过串口、千兆网等接口,传送到电脑上;

2. 可以采用在线调试工具,如SIGNALTAP、CHIPSCOPE、VIVADO等,捕捉到信号,然后保存的方式得到数据。

【问题10】通常情况下rtl代码module里面的输入信号,值是哪里来的呢?

答:

1. 来源于其他模块的输出

2. 来源于FPGA外部的管脚,例如按键、其他芯片的输出信号等

【问题11】if(counter<8)请问这句代码是什么意思呢,按理来说/的优先级高于左移运算符呀?

答:不清楚它要表达的含义。串并转换的方法,可以参考至简设设计原理与应用书籍, 串口案例。

FPGA至简设计原理与应用】书籍连载13 第三篇FPGA至简设计项目实践 第四章 串口通信

http://www.fpgabbs.cn/forum.php? ... 13&fromuid=9396

(出处: 明德扬论坛)

【问题12】老师,怎么将信号实现准确的ns级别的延时呢,有什么好思路吗?[color=rgba(17, 31, 44, 0.56)]

答:正规的做法,就是采用寄存器打拍来延迟,精度为一个时钟周期

【问题13】lvds和lvds_25有什么区别?

答:主要区别在于内部buffer的供电电源情况,在电气方面,两者是等效的(参见数据手册规格)但是内部的I/O电路配置不同

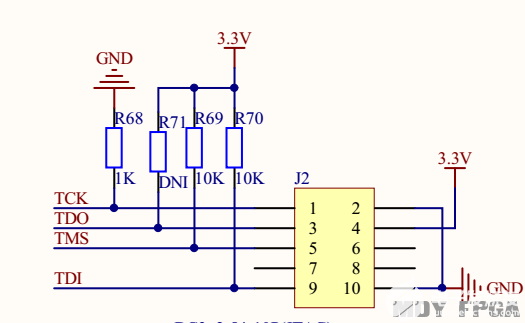

【问题14】xilinx,spartan6的jtag引脚,tck,tms,tdi,tdo需要做上拉处理吗?

答:这个是ALTERA EP4C的JTAG电路,仅供参考

【问题15】用FPGA输出0->1或者1->0的信号,我现在想把上升沿或者下降沿的时间拉长到10ms左右,用FPGA的输出管脚可以实现吗?

答:FPGA直接输出的数字信号,上升沿和下降沿都是很快就完成变化的。如果要控制变慢,其实就是输出固定电平的信号,那么这个需要外置DAC来实现。

【问题16】我们的TFT显示屏是工作在DE模式,是吧?

答:我们的案例默认使用的是DE模式,如果需要非DE模式,可以手动修改底板硬件实现。

【问题17】很多的数字电子元件的引脚都是要求有明确的电平(0/1),但是有个别的器件引脚链接时,可以处于悬空状态

【但很多的教材上写的 引脚不能悬空,因为可能导致数字逻辑电路的状态不确定】,这一点如何理解呢~?

答:对于这种引脚,需要去看对应芯片的数据手册,一般里面都会有介绍说明的。

【问题18】CPLD是没有IP核可以使用吗?

答:看要使用的ip核是什么类型,像RAM、FIFO等固有资源都是有IP核的

【问题19】实质的时钟周期与仿真时钟周期有差别,这个差别会累积起来吗?

答:仿真的时候使用的是理想时钟,例如50M时钟,在实质的板上不可能完全等于50M的,一定有差别。

这种差别的积累,可能会对“总时间”有影响,例如计算1秒时钟,那么就有可能有差别了。

但这种差别的积累,不会产生时序的混乱:因为FPGA内,所有D触发器,都是在一个时钟周期内计算完的,只要满足时序要求,不关心实际频率是多少,总之上升沿来就计算一次。

如不清楚,请仿真,尝试用不同周期的时钟来对同一个电路仿真。

【问题20】如果扇出很大,high fanout 到了4000多,要怎么优化?

答: 扇出是指一个信号驱动了很多其他信号(即这个信号是其他很多信号的产生条件),FPGA对扇出数量有要求,不能扇出太多。

如果扇出太多了,该怎么优化呢?现举例如下:

假设信号A,驱动了信号BCDEFG,即扇出数为6。优化思路是:让A用寄存器分别产生信号A1和A2,再用A1驱动信号BCD,用A2驱动信号EFG。这样扇出数减少为3。

【问题21】如果FPGA芯片没有时钟晶振,其他IO口是不是就不能输入数据呀。晶振影响输入数据不?

答:要看输入是否需要时钟。

例如:使用串口的时候,在电路上就接收和发送两根线,没有用到时钟,所以晶振不影响。而摄像头输出图像的时候,需要先给摄像头一个时钟,再进行相关的配置,这时晶振就有影响。

【问题22】异步信号慢时钟域采集到快时钟域的方法有吗?

答:1、使用FIFO进行跨时钟域处理

2、慢时钟域的信号到快时钟域,是可以被采集到的,跨时钟域之后进行打拍,使其同步化即可

【问题23】工程中经常使用的sop表示第一个有效数据、eop表示最后一个有效数据、mty表示无效字节数等,这些都是那些单词的缩写?

答:习惯性引用了华为项目时的缩写,具体不清楚。

温馨提示:明德扬除了培训学习还有元器件一站式配单业务,人工服务的模式采购,采购**人员联系方式:明德扬元器件一站式配单服务咨询:易老师13112063618(微信同号)

审核编辑:汤梓红

-

【Z-turn Board试用体验】时钟切换、计数器分频都造成门时钟问题2015-06-16 4486

-

FPGA提高篇——禁止使用分频时钟、计数器时钟2018-08-08 8824

-

输出波形对称的奇次分频计数器2009-04-11 864

-

用多级2进计数器的分频电路2009-06-12 1533

-

计数器2009-09-30 1996

-

计数器,计数器的工作原理是什么?2010-03-08 62510

-

由TTL十进制计数器构成的分频器2018-10-03 4180

-

计数器电路设计中分频电路的作用解析2020-11-06 11649

-

计数器与分频电路实验课件下载2021-05-25 1405

-

实时计数器(RTC)技术简介2022-01-26 6984

-

机械不稳定与共振2022-07-08 2291

-

诊断和稳定不稳定开关电源的快速提示2022-08-05 4462

-

基于FPGA的十进制计数器2022-12-20 1131

-

编码器供电电压不稳定怎么办2024-05-29 2709

-

电压不稳定对伺服电机有影响吗2024-06-14 3971

全部0条评论

快来发表一下你的评论吧 !