系统存储器层次结构——高速缓存详解

系统存储器层次结构——高速缓存详解

描述

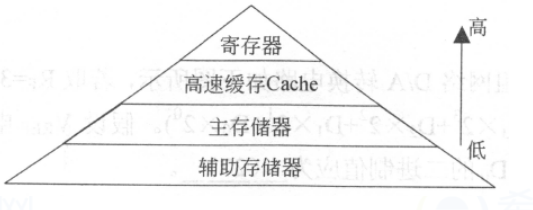

存储系统的层次化结构可以分为5级:寄存器组、高速缓存Cache、主存、虚拟存储器和外部存储器。其中,寄存器组总是在CPU内部,程序员可通过寄存器名访问,无总线操作,访问速度最快;其余4级均在CPU外部,Cache和主存构成内存储系统,程序员通过总线寻址访问存储单元,访问速度较寄存器差;虚拟存储器对程序员而言是透明的 ;外部存储系统容量大,需通过I/O接口与CPU交换数据,访问速度最慢。

高速缓冲存储器

高速缓冲存储器(Cache)的原始意义是指存取速度比一般随机存取存储器(RAM)更快的一种RAM,一般而言,它不像系统主存那样使用动态随机存储器(DRAM)技术,而是使用昂贵但较快速的静态随机存储器(SRAM)技术。

高速缓冲存储器是介于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量较小但速度比主存快得多,其最重要的指标是它的命中率。高速缓冲存储器与主存储器之间信息的调度和传送是由硬件自动进行的。

组成结构

高速缓冲存储器主要由以下三大部分组成:

Cache存储体:存放由主存调入的指令与数据。

地址转换部件:建立目录表以实现主存地址到缓存地址的转换。

置换部件:在缓存已满时按一定策略进行数据替换,并修改地址转换部件中的目录表。

工作原理

高速缓冲存储器通常由高速存储器、联想存储器、置换逻辑电路和相应的控制线路组成。在有高速缓冲存储器的计算机系统中,处理器存取主存储器的地址划分为行号、列号和组内地址三个字段。于是,主存储器就在逻辑上划分为若干行:每行划分为若干的存储单元组;每组包含几个或几十个字。高速存储器也相应地划分为行和列的存储单元组。二者的列数相同,组的大小也相同,但高速存储器的行数却比主存储器的行数少得多。

联想存储器用于地址联想,有与高速存储器相同行数和列数的存储单元。当主存储器某一列某一行存储单元组调入高速存储器同一列某一空着的存储单元组时,与联想存储器对应位置的存储单元就记录调入的存储单元组在主存储器中的行号。

当处理器存取主存储器时,硬件首先自动对存取地址的列号字段进行译码,以便将联想存储器该列的全部行号与存取主存储器地址的行号字段进行比较。若有相同的,表明要存取的主存储器单元已在高速存储器中,称为命中,硬件就将存取主存储器的地址映射为高速存储器的地址并执行存取操作;若都不相同,则表明该单元不在高速存储器中,称为失效,硬件将执行存取主存储器操作并自动将该单元所在的那一主存储器单元组调入高速存储器相同列中空着的存储单元组中,同时将该组在主存储器中的行号存入联想存储器对应位置的单元内。

当出现失效而高速存储器对应列中没有空的位置时,便淘汰该列中的某一组以腾出位置存放新调入的组,这称为置换。确定替换的规则称为置换算法,常用的置换算法有最近最久未使用算法(LRU)、先进先出法(FIFO)和随机法(RAND)等。置换逻辑电路就是执行这个功能的。另外,当执行写主存储器操作时,为保持主存储器和高速存储器内容的一致性,对命中和失效分别进行处理。

审核编辑:符乾江

-

MCU存储器层次结构解析2025-05-09 973

-

浅谈存储器层次结构2024-02-19 2147

-

全面解析存储器层次结构原理2023-12-25 2698

-

高速缓存Cache介绍2023-09-07 590

-

一文搞懂计算机存储器中的高速缓存2022-07-23 6260

-

高速缓存(cache)的工作原理是什么?高速缓存可分为哪几类2021-12-23 2648

-

存储系统的层次结构2021-07-29 2221

-

高速缓存/海量缓存的设计实现2020-12-04 1684

-

非易失性MRAM存储器在各级高速缓存中的应用2020-11-09 1212

-

MRAM高速缓存的组成2020-11-06 2327

-

高速缓冲存储器基础知识详细介绍2017-12-06 11541

-

存储器和高速缓存技术2010-11-11 984

-

高速缓冲存储器部件结构及原理解析2010-04-15 5121

-

高速缓存(Cache),高速缓存(Cache)原理是什么?2010-03-26 7229

全部0条评论

快来发表一下你的评论吧 !