多级调试方法的硬件仿真

描述

芯片设计调试是一门困难的学科,而片上系统 (SoC) 设计则更是如此。这就像众所周知的大海捞针。对于 SoC 设计,它是两个大海捞针,一个用于软件,另一个用于硬件。软件开发团队经常将集体矛头指向硬件团队,声称这是一个硬件错误,而硬件团队则迅速回击,声称这是一个软件错误。如果没有有效的验证工具来查明问题,就很难知道谁是对的。这就是硬件仿真的用武之地。

硬件仿真对于调试硬件和测试 SoC 设计中硬件和软件的集成非常重要,远远早于第一个芯片。当工程组的两个不同部分(硬件设计师和软件开发人员)使用仿真时,他们能够共享相同的系统和设计表示。SoC 设计的组合软件和硬件视图使它们能够协同工作以调试硬件和软件交互。

作为大多数 SoC 验证流程的基础,硬件仿真允许工程团队更有策略地进行规划并实施基于多个抽象级别的调试方法。工程团队不必彼此独立地钻进两个干草堆。相反,他们可以跨嵌入式软件和底层硬件之间的边界跟踪错误,以确定问题出在软件还是硬件上。

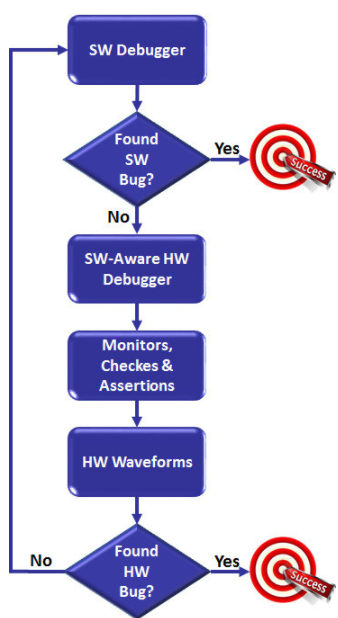

实现基于多个抽象级别的调试方法从最高级别的嵌入式软件开始,然后在抽象级别向下移动以跟踪各个硬件元素的行为。事实上,从包含数十亿个时钟周期的数据库开始,软件调试器可以将问题定位到几百万个时钟周期内。在这个级别,软件开发人员可以识别软件代码中的源代码,或者他们的硬件设计同行可以使用软件感知硬件调试方法来专注于较低的抽象级别。该方法要求通过硬件事务器实现监视器、检查器和断言,以避免速度下降并帮助将问题缩小到几千个周期。

一旦审查了这两个级别收集的数据,硬件仿真允许工程组向下移动到信号级别。它可以通过所识别时间段的寄存器传输电平(RTL)波形分析信息,并追踪其可能的来源。要么发现了硬件错误,要么清除了硬件故障。如果是后者,它会迫使决定回到软件环境。

导航多个级别的调试抽象

在不同的抽象级别之间导航——从软件到硬件再到后面——避免了长时间的模拟运行和大量的详细数据(图 1)。

【图1 | 硬件仿真为软件和硬件调试提供了一个生态系统。]

软件模拟器无法实现多级调试方法,因为它们太慢而无法有效执行嵌入式软件。实际上,它们将运行数月来处理数十亿个设计周期,这些设计的大小达到数亿个专用集成电路 (ASIC) 等效门。对于消费电子设备或任何其他电子设备的供应商来说,这是一个不可接受的时间限制。

虽然仍然被广泛使用,但在验证场景中推动其成功的原始仿真风格的在线仿真 (ICE) 模式现在在基于事务的验证中面临着可行的替代方案。从概念上讲,这个想法很简单。测试是在高级抽象上编写的,从高级命令到位级信号的转换从测试台转移到称为事务器的专用实体中。通过将事务处理器映射到硬件仿真器上,与基于仿真的验证相比,可以轻松实现 5 或 6 个数量级的加速。

工程组使用事务处理程序来构建虚拟测试环境,而不是 ICE 物理目标系统,方法是用一组等效的事务处理程序替换一组基于 I/O 协议的速度适配器(图 2)。

【图2 | 一个完整的虚拟测试环境包括通过事务建模的所有 SoC 外围接口。]

基于事务的加速简化了设计调试。通过完全控制并非由硬件测试台提供的设计时钟,调试变得更加容易和高效。通过控制时钟频率,可以停止仿真的被测设计 (DUT) 模型、读取其内存内容、强制某些寄存器或转储波形。

传统上,在 ICE 环境中调试需要由来自目标系统的不可控时钟驱动的硬件逻辑分析仪。该设置导致了不确定的行为并损害了调试 DUT 的能力。硬件仿真供应商最近通过将其转换为确定性行为的方法解决了 ICE 外围设备的随机行为。

多层次的协同验证视角

一旦软件设计人员和硬件开发人员使用硬件仿真体验了基于事务的验证,他们的整个验证视角就会发生变化。无需繁琐的 ICE 硬件即可快速设置强大的测试环境的能力意味着更容易和更有效的调试。目标可能是相同的——在更短的时间内做出更好的设计——但现在的体验可能会变得不那么具有挑战性。

工程团队发现现代硬件仿真器是测试硬件和在 SoC 设计中集成硬件和软件的必要条件。它使他们能够更有策略地进行规划并成功实施硬件/软件联合验证。

审核编辑:郭婷

-

单片机系统硬件的调试方法2025-12-03 166

-

ST-LINK硬件仿真调试2021-08-11 1450

-

电梯现场仿真调试系统的设计2009-06-18 931

-

多级放大电路的耦合方式及分析方法2010-09-16 1038

-

FPGA硬件系统的调试方法2010-02-08 3175

-

多级调谐放大器分析和调试方法(4D4型电视机的中放电路)2010-09-18 2482

-

基于单片机软硬件联合仿真解决方案2010-09-26 1073

-

计算机仿真在多级放大电路设计中的应用2015-12-24 980

-

LCD12864多级菜单仿真2016-01-13 1311

-

GOE219硬件调试常见问题及检修方法2016-12-27 949

-

ARM仿真调试技术:软件仿真和硬件仿真2020-06-20 10026

-

用于调试嵌入式系统软件的硬件仿真2022-06-19 2702

-

多级调试方法的硬件仿真2022-07-09 1246

-

STM32硬件错误的调试技巧2022-07-21 3359

-

硬件调试:JLink 驱动配置与调试技巧2025-06-12 1895

全部0条评论

快来发表一下你的评论吧 !