5G基础设施在射频芯片内部开辟新集成前沿

描述

大规模多输入多输出 (mMIMO) 的出现为基站硬件带来了新的射频挑战,而新的无线电技术促进了通向 5G 无线的道路。因此,已经面临日益复杂的射频复杂性的 5G 基础设施现在需要半导体公司进行另一轮创新,以通过更具适应性的解决方案来提高网络效率。

到目前为止,通信设备制造商势必会创建多张具有特定频率的卡,以满足无线行业对全球各种授权和非授权 5G 频段的需求。以爱立信为例,它每周创建两个电路板设计,以跟上全球所有频率计划。

那么我们如何开发一个独立于频率并且可以在多个地区使用的单一平台呢?特别是对于 mMIMO 无线电,它在面板中使用大量天线,这使得网络效率势在必行。Xilinx 声称其Zynq ® UltraScale+™ 射频片上系统 (SoC) 提供了一个单芯片自适应平台,可以针对多种 5G 标准进行重新配置。

直接射频采样

在传统的模拟方法中,射频信号链通过分立元件进行射频采样后通过 JESD204 接口连接到数字前端。它还涉及每个芯片一到两个转换器。在这里,从一个芯片到另一个芯片的数据转换可能需要高达 8 瓦的功率来传输 320 Gb 的数据。

但是,当您使用大量发射器和接收器时,例如 mMIMO 设计中的情况,您必须非常注意功耗。因此,Zynq UltraScale+ 提供了一个单芯片自适应无线电平台,可对射频信号进行直接采样。

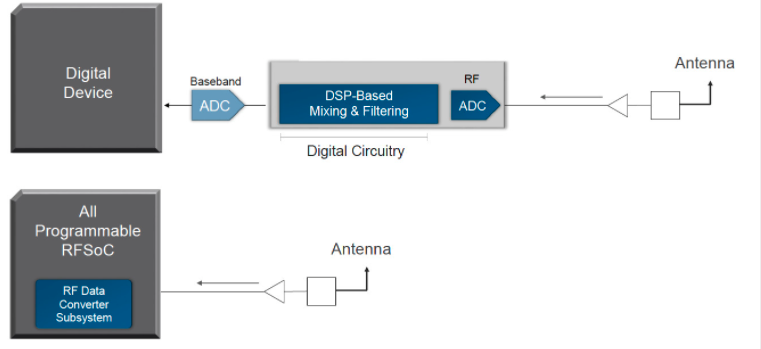

图 1:传统的基于模拟的方法(上图)和直接射频采样方法(下图)之间的比较。

直接射频采样直接处理输入信号,无需下变频为中频 (IF) 信号,并应用 DSP 技术执行数字域中的信号调节等任务。当射频电路进入下一个芯片以执行网络路由等任务时,这消除了 JESD204 瓶颈。

这反过来又简化了模数信号链并允许处理更多数据,这是 5G 系统中 mMIMO 基站的关键优势。该单芯片自适应平台集成了基带、无线电 IP、MAC、DSP 信号和滤波以及具有通用数字处理器和 DDR4 内存子系统的数据转换器。

例如,RF 数据转换器的集成为降低功耗、占地面积和物料清单 (BOM) 成本提供了宝贵的场所。Zynq ® UltraScale+ 通过 14 位模数转换器 (ADC) 支持高达 5 Giga 样本/秒的直接 RF 采样,并通过 14 位数模转换器 (DAC) 支持高达 10 G 样本/秒的直接射频采样。

在 Zynq UltraScale+ 中,RF ADC 的采样率从 4 G sample/s 提升到了 5 G sample/s,RF DAC 的采样率从 6 G sample/s 提升到了 10 G sample/s。对于时分双工 (TDD) 用例,这将 RF 数据块的功耗降低了 20%。在这里,值得一提的是,大多数 5G 无线电都是基于 TDD 技术的。

FPGA 如何赋能射频设计

以 FPGA 为中心的设计通常需要数据转换器,但直到现在,只有低性能转换器集成到 FPGA 中用于系统监控等应用。这主要是因为模拟和数字处理器是由半导体公司的不同团队甚至完全由不同的公司开发的。

数字团队致力于节点迁移以缩小节点大小,而模拟工程师使用稳定的旧处理节点。但是,它必须在要求更高集成度的现代无线电用例(例如 mMIMO)中发生变化。

Xilinx 声称,采用 16 nm FinFET 工艺制造的 Zynq UltraScale+ 是这种更高集成度的体现。它将模拟和数字域都放在一块硅片中,以通过可编程逻辑优化信号流。

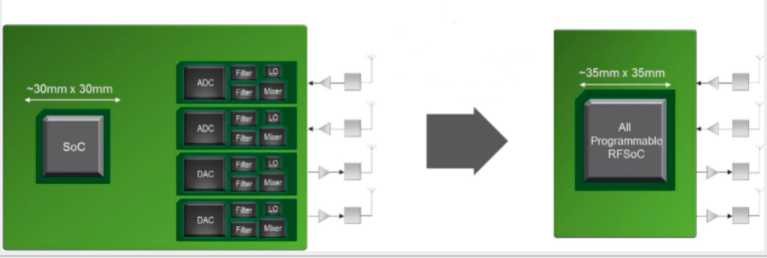

硬件和软件可编程引擎的集成消除了分立元件,可将功耗和设计尺寸降低多达 50%。例如,Zynq UltraScale+ 通过将外部 PLL 振荡器的数量从四个减少到一个来降低 BOM 成本。

图 2:集成模拟和数字部件的单芯片 RF 解决方案如何降低功耗、占用空间和 BOM 成本。

除了 5G 基站设计,Xilinx 还将这种多频段无线电芯片用于其他射频应用,例如相控阵雷达网络和天气监视系统。然后,还有用于电缆接入的远程 PHY 节点、汽车中的激光雷达系统、测试和测量以及卫星通信等用例。

适应5G世界

5G 标准将在未来几年内不断发展,这将继续改变系统要求。因此,与通信设备制造商一直在使用 ASIC 的 3G 和 4G 设计领域不同,灵活的逻辑方法更有可能应对增量的 5G 部署。

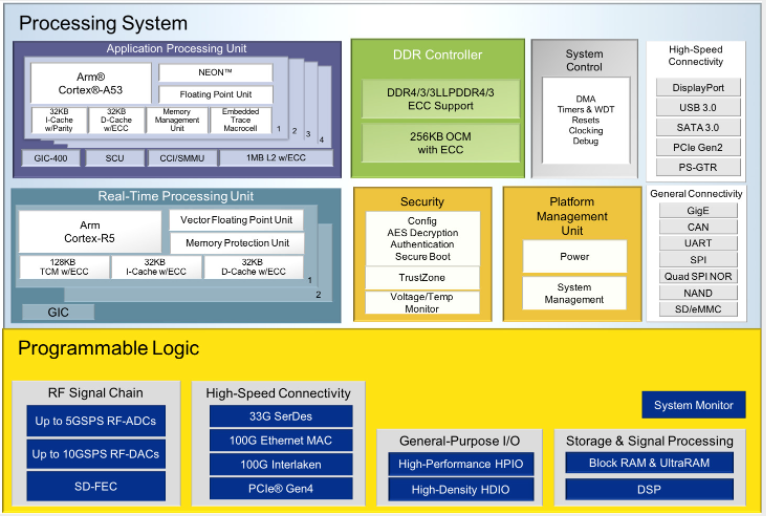

当今 5G 设计环境中的 ASIC 解决方案很可能在一年内过时。另一方面,连接模拟和数字域的可编程解决方案(图 3)可以针对各种 5G 安装进行重新配置。

图 3:显示不同子系统的 Zynq UltraScale+ RF 芯片的框图

本文介绍了一种高度集成的 RF 芯片的概况,该芯片在数字域内执行下变频过程,从而绕过涉及分立元件下变频的传统射频采样模拟方式。

审核编辑:郭婷

-

全球5G市场提速 基础设施将达260亿美元2018-11-19 2429

-

MACOM视角:5G将如何发展?2019-01-22 3104

-

低频5G与毫米波5G机遇与挑战并存2019-06-18 2906

-

5G对无线基础设施有什么要求2019-07-05 1827

-

5G无线与对集成度更高、速度更快的多功能设备有哪些新要求呢?2019-07-31 3608

-

5G基础设施发展有什么趋势?2019-08-01 2825

-

5G基础设施和对端到端可编程性的需求有哪些?2019-10-08 1923

-

5G射频芯片2021-10-17 14364

-

5G时代移动通信基础设施将迎来全面的更新2020-10-30 2870

-

如何保护5G基础设施?2020-12-24 1239

-

5G基础设施在射频芯片内部开辟集成前沿2022-06-08 1491

-

5G基础设施在射频芯片内部开辟了新的集成前沿2022-10-24 2478

-

5G基础设施开启射频芯片内部的新集成前沿2022-12-01 1636

-

Qorvo 支持 5G 基础设施2023-01-05 1769

-

Qorvo如何推动5G射频芯片升级2025-09-09 2059

全部0条评论

快来发表一下你的评论吧 !