如何在软件中实现高精度NCO

描述

在本系列的第 1 部分中,我们将了解如何基于直接数字频率合成 (DDFS) 原理设计一个非常精确的正弦波发生器,但在浮点 DSP 处理器上通过软件实现。在第 2 部分中,我们将介绍如何在软件中实现高精度 NCO。

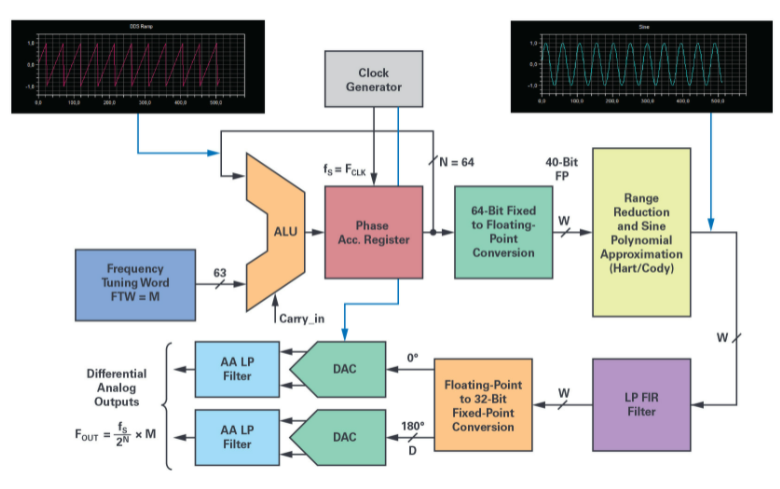

构建一个具有与最好的模拟振荡器相似或更好的失真性能的高精度交流音发生器,如最著名的惠普分析仪或应用笔记 AN-1323 中所述,即使专用于音频,也不是一件容易的事频谱(直流至 20 kHz 范围)。然而,如前所述,完整的软件实现,使用嵌入式处理器的足够算术精度执行相位计算 (ωt) 和正弦函数 (sin(ωt)) 近似,当然可以帮助最大限度地减少量化副作用、噪声、以及由此产生的马刺。这意味着图 2 中的所有 NCO 功能块都转换为代码行(没有 VHDL!

对于相位到正弦幅度转换引擎,完整的 LUT 方案或任何变化都需要过多的内存或过多的插值操作才能实现完美的正弦一致性。相反,用于正弦逼近的多项式方法通过允许使用成本非常低的通用 DSP,提供了非常好的复杂性与精度之间的折衷。多项式级数展开也非常有吸引力,因为它相对简单,并且能够在选择幂级数类型时提供充分的灵活性,并为给定的精度定制算法。它不需要大的存储空间、少于 100 行 SHARC DSP 装配线,并且只需要几个 RAM 位置来存储多项式系数和变量,因为正弦值仅在采样时刻计算。

首先,正弦逼近函数的明显选择是使用具有适当阶数的直线 Taylor/MacLaurin 幂级数来满足目标精度。然而,由于幂级数往往在端点处失效,因此在执行任何多项式评估之前,必须将参数输入范围缩小到更小的区间。在没有参数范围缩减的情况下,只有非常高阶的多项式才能支持函数域上的高精度,例如 [–π, +π]。因此,需要对初等函数应用一些变换以得到简化参数,例如 sin(|x|) = sin(f + k × π/2) 和 sin(f) = sin(x – k × π/ 2) 0≤f《π/2。因此,应特别注意三角函数以避免减法抵消,这将导致严重的精度损失并产生灾难性的结果,尤其是在算术精度较差的情况下。在我们的例子中,当相位输入较大或接近 π/2 的整数倍时,可能会发生这种情况。

除了周期性和模 2π 重复之外,sin(x) 函数的对称特性还可用于进一步减小逼近范围。鉴于正弦函数在区间 [0, 2π] 中关于点 x = π 反对称,因此可以使用以下关系:

将范围缩小到 [0, π]。以同样的方式,sin(x) 显示了关于区间 [0, π] 中由 x = π/2 定义的线的对称性,使得:

对于区间 [0, π/2] 中的 x,这进一步减小了角度输入逼近范围。进一步将参数减少到更小的区间(如 [0, π/4] 以提高准确性)效率不高,因为它需要同时评估正弦和余弦函数,这由常见的三角关系决定:sin(a+b ) = sin(a) × cos(b) + cos(a) × sin(b),值得产生正交音。

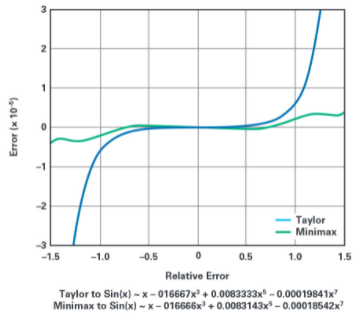

ADI 公司的 ADSP-21000 系列应用手册第 1 卷描述了一种几乎理想的(用于嵌入式系统)正弦逼近函数,该函数基于为第一个 ADI DSP 浮点处理器(即 ADSP-21020)编写的优化幂级数,它基本上是一个SHARC核心。sin(x) 的这种实现依赖于 Hart 等人 4 发表并由 Cody 和 Waite5 改进的极小极大多项式近似,用于浮点运算,以减少舍入误差并避免如前所述的取消的发生。minimax 方法依赖于 Chebyshev 多项式和 Remez 交换算法来确定所需最大相对误差的系数。如图 3 中的 MATLAB 所示,

图 3. 与定义在 0 附近的 Taylor-MacLaurin 方法不同,极小极大正弦近似方法在 [–π/2 到 +π/2] 区间内最小化和均衡最大相对误差。

虽然所有计算都可以使用 32 位定点算术执行,但多年来,最常见和最方便的数学计算格式一直是 IEEE 754 浮点标准,尤其是在处理长数时。当时根本没有单片浮点DSP处理器,只有ADSP-3212和ADSP-3222等简单的浮点乘法器和ALU计算IC。这种格式取代了计算机行业的大多数专有格式,并成为所有 SHARC DSP 处理器的原生格式,包括单精度 32 位、扩展精度 40 位以及最近用于 ADSP-SC589 的双精度 64 位和 ADSP-SC573。

SHARC 40 位扩展单精度浮点格式及其 32 位尾数为该正弦波生成应用提供了足够的精度 (u 2–32) 并保持相等,Cody 和 Waite 表明 15 阶多项式是合适的对于 32 位的整体精度,在 [0 到 +π/2] 输入域上具有均匀分布的误差。最小化运算次数并保持准确性的最后调整是实现多项式计算的霍纳规则,这是一种在一个点上计算多项式的快速取幂方法,例如:

R1 到 R7 是多项式级数的 Cody 和 Waite 系数,只需 8 次乘法和 7 次加法即可计算任何输入参数 ε[0, π/2] 的正弦函数。以汇编子程序形式编写的完整 sin(x) 近似代码在 SHARC 处理器上大约需要 22 个内核周期执行。原始汇编子程序被修改为在获取 40 位多项式浮点系数时同时执行双内存访问,以节省六个周期。

图 4. 软件 DDS 简化框图给出了数据算术格式和处理元件之间各种量化步骤的位置。

NCO 64 位相位累加器本身使用双精度二进制补码小数格式的 SHARC 32 位 ALU 来执行。具有内存更新的完整相位累加器执行需要 11 个内核周期,因此,每个 NCO 输出样本在大约 33 个内核周期内生成。

图 4 中的图表显示了基于软件 DSP 的 NCO 的功能块实现,其中参考了每个阶段的算术格式精度。此外,信号模拟重构还需要一个或两个 DAC 及其模拟抗混叠滤波器电路,以实现完整的 DDFS。处理链的关键要素是:

64位相位累加器(SHARC ALU双精度加法溢出);

64 位小数定点到 40 位 FP 转换块;

范围缩减块 [0 到 + π/2] 和象限选择(Cody 和 Waite);

用于相位幅度转换的正弦逼近算法 (Hart);

–1.0 到 +1.0 范围内的 sin(x) 重建和归一化阶段;

必要时进行 LP FIR 滤波器和 sin(x)/x 补偿;

以及 40 位 FP 到 D 位定点转换和缩放功能,以适应 DAC 数字输入。

可以在 NCO 的输出端放置一个可选的数字低通滤波器,以消除可能折叠在感兴趣频带中的任何杂散和噪声。可选地,该滤波器可以根据为模拟重建选择的 DAC 提供插值和/或逆 sin(x)/x 频率响应补偿。这种低通 FIR 滤波器可以使用 MATLAB 滤波器设计器工具来设计。例如,假设采样频率为 48 kSPS,直流至 20 kHz 带宽,带内纹波为 0.0001 dB,带外衰减为 –150 dB,则可以使用 40 位浮点实现高质量等纹波滤波器系数。只有 99 个滤波器系数,它的总执行时间将在单指令、单数据 (SISD) 单计算单元模式下消耗大约 120 个 SHARC 内核周期。数字滤波后,DMA 使用其中一个 DSP 同步串行端口将计算的样本对发送到 DAC。为了获得更好的速度性能,链接 DMA 操作也可以与大型乒乓存储器缓冲区一起支持按块操作进行处理。例如,块数据大小可以等于 FIR 数据延迟线的长度。

NCO 的最终调整以获得最佳 SFDR

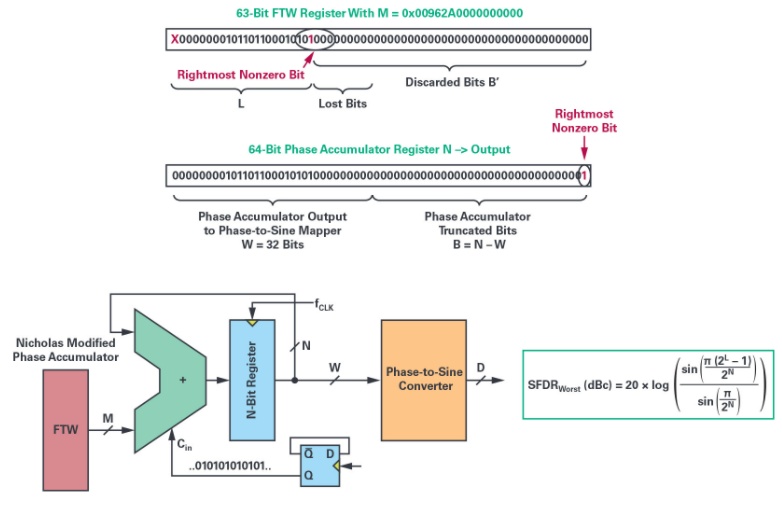

如前所述,NCO 受到杂散的影响主要是由于相位累加器输出的截断,并且在较小程度上,来自对通过计算或制表获得的正弦值进行的幅度量化。相位截断导致的误差通过相位调制(锯齿波)在载波频率附近产生杂散,而正弦幅度量化导致谐波相关的杂散,尽管长期以来被认为是随机误差和噪声。今天,如 Henry T. Nicholas 和 H. Samueli 的技术论文 7 中所描述的,相位累加器的操作在数学上是众所周知的。经过全面分析,提出了一个模型,将相位累加器视为离散相位样本置换发生器,从中可以预测频率杂散。

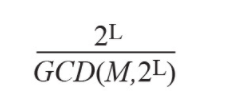

(其中 GCD 是最大公约数)由频率调谐字 M 的最右边位位置 L 确定,如图 4 所示。因此,L 的值定义了序列类别,每个类别共享自己的一组相位组件,但根据排列

比率。在时域中生成的这些截断相位样本序列用于通过 DFT 确定频域中每个杂散线的相应位置和幅度。这些序列还表明 M (FTW) 的奇数值表现出最低频率杂散的幅度,并建议对相位累加器进行简单修改,以满足这些最小条件,只需将 1 LSB 添加到 FTW。这样,无论 M 值和相位累加器的初始内容如何,相位累加器输出序列都被迫始终具有相同的 2N 个相位元素。然后,最差杂散音幅度的电平降低 3.922 dB,等于 SFDR_min (dBc) = 6.02 × W。 Nicholas 改进的相位累加器为 NCO 带来了几个好处,

图 5. FTW 最右边的非零位的位置设置了理论上的 SFDR 最坏情况水平。Nicholas 改进的相位累加器解决了任何 N 值的问题,并使 NCO 的 SFDR 最大化。

因此,对于 32 位的输出相位字 W,由于相位截断而导致的最大杂散幅度被限制为 –192 dBc!正弦样本值的有限量化也会导致另一组频率杂散,通常将其视为噪声,并通过众所周知的关系 SNRq(dB) = 6.02 × D + 1.76 进行估计。由于相位到正弦幅度转换算法阶段的近似误差,这必须添加到寄生元素中,但是,考虑到在选择相位到正弦近似算法和计算的精度。

这些结果表明,我们的软件正弦 NCO 的线性度和噪声都处于理论水平,远远超出了测试市场上大多数高精度 ADC 所需的阈值。仍然需要找到信号链中最后但也是最关键的元素:重建 DAC 及其互补模拟抗混叠滤波器和相关的驱动器电路,这些都可以满足预期的性能水平。

审核编辑:郭婷

-

请问ADS1263能做到多高精度?实现高精度应该注意什么?2025-01-01 549

-

如何在MSP430™上实现内置振荡器的高精度定时器2024-09-14 451

-

如何在激光雷达和接近检测中利用高速比较器提高精度2024-09-02 374

-

电磁流量计:在工业应用中实现高精度2023-11-23 460

-

如何在软件中实现高精度NCO2022-07-05 1755

-

如何在提高精度和延长运行时间的同时提高电池的安全性?2021-03-16 1488

-

如何在Cortex-M处理器上实现高精度关键词的识别2021-02-05 1954

-

GPS高精度的时钟的设计和实现2017-01-23 816

-

电磁流量计可在工业应用中实现高精度2016-01-07 700

-

基于FPGA的NCO设计方案2012-01-06 8107

-

在FPGA中实现高精度快速除法2010-07-17 736

-

基于CORDIC算法的NCO实现2009-12-15 809

-

高精度温度控制的实现2009-07-11 1035

全部0条评论

快来发表一下你的评论吧 !