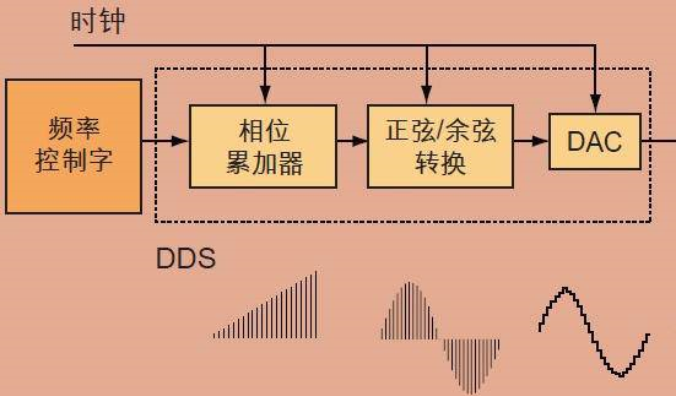

DDS直接数字式频率合成器的正弦波和余弦波

描述

一、功能描述

本工程实现DDS直接数字式频率合成器,利用正弦波相位线性增加的特点,产生正弦波和余弦波。本工程主要由3部分组成:相位累加器,相位幅度转换,数模转换器DAC(FPGA外部实现)。其中,相位累加器的高10比特用于ROM的索引地址。

二、波形调制说明

模块将一个正弦波采样1024个点,然后保存到内部一个8比特、1024深度的ROM当中,通过改变时序和相位控制字,即可生成不同频率的波形。 生成波形的公式是: FO=TCLK*FCW/655360 上面公式中,TCLK是指本模块的工作时间,FCW是相位控制字,FO即是生成的信号频率。

相位控制字FCW可以改变每次步进数M。如果FCW=128,则模块内部累加器每次加128,则经过M=16’hffff/128=512个时钟,就可以循环一个周期,也就是512个时钟完成一个正弦波输出。假如FCW为256,则代表1024/4=128个时钟周期就输出一个正弦波。

三、应用举例

设定是FCW=128,CLK=50M的时钟频率,由公式计算得出F0=10KHZ。实际测量出一个波形时间为10332000ps,最终波形的频率为10KHZ。 如果是FCW=128,CLK=5M的时钟频率,由公式计算得出F0=1KHZ。输出实际测量一个波形时间为51898054ps,最终波形的频率为1KHZ。

如果是FCW=128,CLK=100M的时钟频率,由公式计算得出F0=0.2MHZ。输出实际测量一个波形时间为5167188ps,最终波形的频率为0.2MHZ。 以此类推,通过对频率控制字的改变来控制波形频率。

四、平台效果图

五、实现过程

首先根据所需要的功能,工程顶层的输入输出信号列表。

我们可以把工程划分成三个模块,分别是Sin相位转波形模块和Cos相位转波形模块和相位累加器模块。

1. 相位累加器模块

本模块根据设置好的相位控制字FCW来进行相位累加,以此控制波形的相位,sum 《= sum + fcw;对相位不断累加,然后将累加的sum数据实时传到另外两个模块中去 以此本模块实现了相位累加,并将数据传输给其它模块的功能。

本模块信号列表如下:

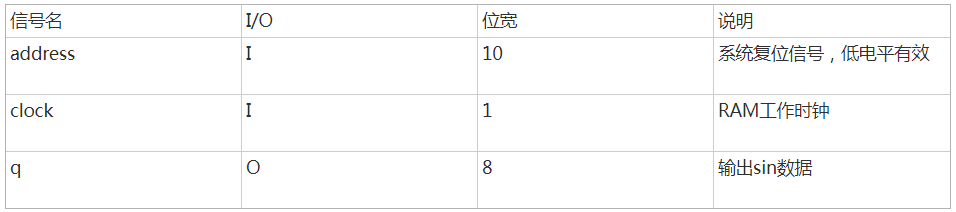

2.Sin相位转波形模块

本模块实际上是一个RAM,事先将相位和相应相位上的幅值关系写入,然后通过从相位累加模块传来的相位累加数据sum进行查表,得到对应的幅值,以此当一个sin波的相位全部转换一遍后即可得到一个完整的sin波形。

信号列表如下:

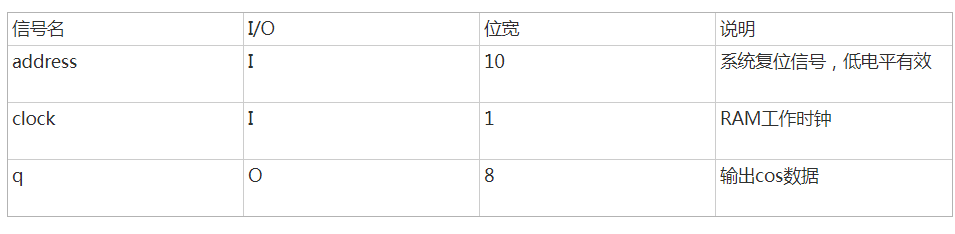

3. Cos相位转波形模块

本模块实际上是一个RAM,事先将相位和相应相位上的幅值关系写入,然后通过从相位累加模块传来的相位累加数据sum进行查表,得到对应的幅值,以此当一个cos波的相位全部转换一遍后即可得到一个完整的cos波形。

信号列表如下:

-

AD9954 400MSPS、14位、1.8V CMOS、直接数字频率合成器技术手册2025-05-06 945

-

Verilog实现DDS正弦波发生器2023-12-22 2409

-

DDS直接数字式频率合成器基本原理及性能特点2022-11-28 7955

-

什么是频率合成器2019-08-19 5672

-

基于DDS的频率合成器设计介绍2019-07-08 2908

-

一种基于DDS器件AD9951的射频正弦波信号发生器设计2019-06-19 2138

-

AD9914BCPZ直接数字频率合成器2019-04-29 1447

-

3.5 GSPS直接数字频率合成器AD9914的优势特性2018-10-15 2655

-

一文详解Vivado调用ROM IP core设计DDS2018-07-02 11150

-

合成器2017-12-06 3522

-

【Z-turn Board试用体验】+基于FPGA和DDS技术的三相正弦波的发生器设计2015-05-30 35358

-

时钟应用中的直接数字频率合成器2012-02-01 713

-

低相噪毫米波频率合成器设计2010-04-22 2979

全部0条评论

快来发表一下你的评论吧 !