存算一体技术路线如何选

存算一体技术路线如何选

描述

电子发烧友网报道(文/李弯弯)过去几年,越来越多企业加入到存算一体技术的研究中,如今,存算一体芯片已经逐渐走向商用。

从目前入局的企业来看,路线各异,包括采用不同类型的存储器,从中小算力入手,或是直接进行大算力存算一体芯片的研究,有的是采用模拟的存算技术,有的采用数字的存算技术。

那么如何选择合适的存储器类型,如何做大算力的存算一体芯片设计,采用模拟技术还是数字的方式?千芯科技董事长陈巍在接受电子发烧友采访的时候做了详细介绍。

如何选择存储器类型

千芯科技致力于大算力存算一体芯片技术的研究,在SRAM、MRAM、RRAM方面都有探索,目前基于SRAM存算一体产品样卡正在测试,公司也在与中科院、清华大学等机构一起优化基于RRAM、MRAM存算一体电路的设计。

该公司技术团队早期接触过各类存储器,陈巍博士10多年前就作为国家专项课题的技术负责人主持过当时国内最先进的NOR Flash芯片及Memory Compiler(存储器编译器)的设计研发,作为负责人创建国内首个3D NAND 闪存设计团队,SRAM、RRAM、MRAM等都接触了10年以上,有不少这些存储器的专利。

千芯科技也给这些存储器做了自己的分类,陈巍强调,在进行存算一体存储器选择的时候,重点还是要看客户和应用需求,根据实际应用场景来选择存储器比较合适。

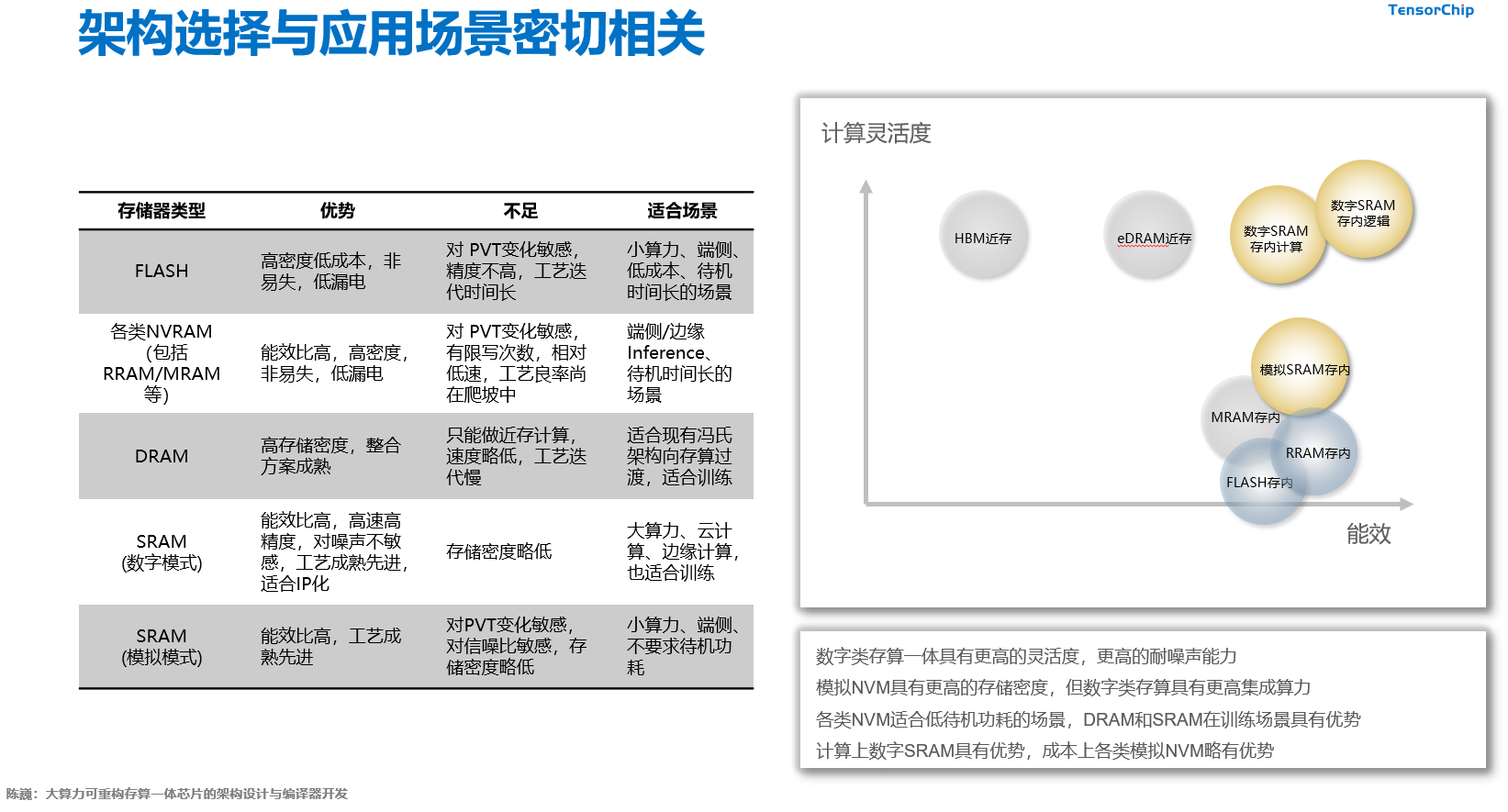

图:存储器类型,优势、不足和适用场景(来自千芯科技)

因为虽然都是存算一体,但是从应用来看,有些存算一体需要更偏向于存(Computing Memory),有些更偏向于算(Memory Computing),比如端侧一些语音识别、人像识别的场景,对功耗和成本要求比较高,把AI计算的部分和存的部分合成一个器件,能够有效降低成本。

比如在云计算领域,这个领域需要计算的模型非常大,同时训练场景下,需要不断更新数据,因此在这样的应用场景下,一些非易失存储器的读写速度,就不如SRAM、DRAM、RRAM好,这些场景更偏向于算,它目前会倾向于偏向计算能力的存储器。

也就是说,如果是偏向于低成本,同时希望待机功耗更好,可以选择非易失存储器,包括Flash、RRAM、MRAM等;如果偏向于大规模计算,多数情况下可以选择RRAM、SRAM和DRAM。另外具体来说选择哪种存储器,还和各家的专利布局绑定有关。

大算力存算一体芯片设计

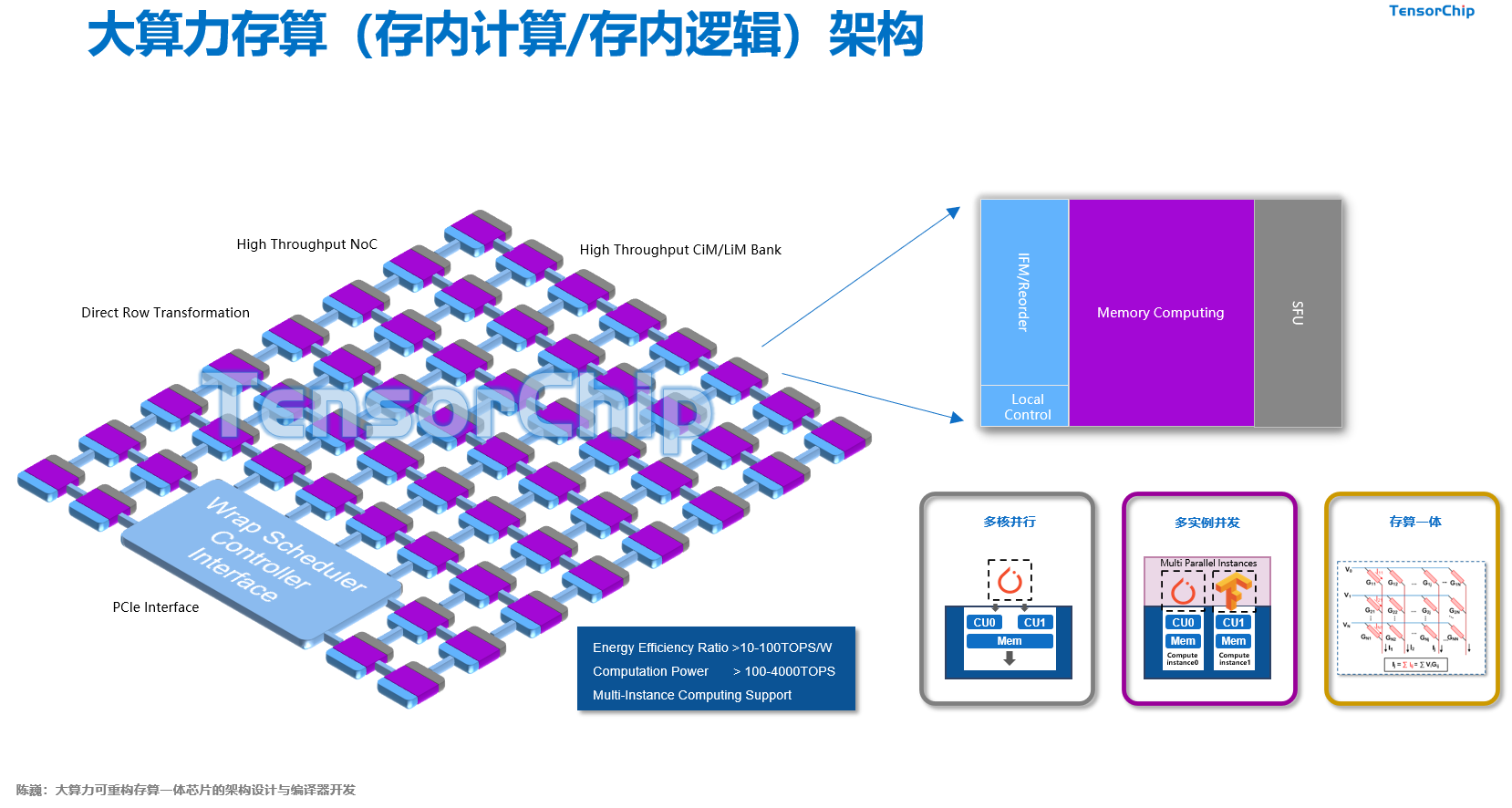

在自动驾驶、数据中心等领域,对大算力的需求比较明显,因此各家企业也在大算力存算一体芯片的研发和推广上投入精力。在陈巍看来,目前除了NOR闪存有些受容量限制,上述提到的各类存储器基本可以用来做大算力存算一体。

闪存存算方面,目前主要路线是基于NOR flash(不是目前优盘所用的闪存类型),多数情况下存储容量较小,这使得NOR flash单片算力达到1 TOPS以上器件代价较大,通常业内说大算力一般是20-100TOPS以上,因此不太好直接做大算力的存算一体。而其他的存储器,包括SRAM、RRAM等,现在已经看到,有实际产品证明可以是可以用来做到大算力的存算一体。

在设计上,大算力存算一体结构和小算力会有所不同,据陈巍介绍,这跟存算一体架构里面的计算架构有关,大算力计算架构和小算力计算架构不一样,一是大算力的计算核会有特别的外围电路设计,来使它的吞吐能力比小算力更强;二是在整体结构上,大算力有更多核心并联,相当于多个小算力整合成一个大算力,有点类似于GPU的整合方式,因为GPU也相当于是不同的小算力的核心,整合起来的架构。

虽然说都可以做大算力,而基于非易失存储器,目前做大算力存算一体,也会遇到一些工艺挑战,基本上循环读写次数在十的六到八次方之后,就可能出错,所以到目前为止,国际上直接用NVM做200Tops以上算力的还较少。

因为在大算力场景下,它有非常高频度的读写,这样会较早的面临失效的可能,而这个失效可能会导致计算错误,对于产品来说,这是必须要做优化的,特别是在自动驾驶领域,如果遇到这种失效将会导致车辆失控。

这个问题如何解决呢,陈巍表示,经过与业内专家合作分析,他们认为需要从两方面去做,一是器件的工艺水平需要优化,二是做冗余器件设计去解决这个问题,目前对于计算为主的场景,做冗余器件设计,它的性能可能就没有先进工艺下的SRAM强,做了冗余设计之后,它的面积也会进一步提升,这样成本的优势可能就会有一定的降低。

因此总结来看,选择何种存储器去做大算力存算一体,还是要看场景,看客户的需求,以及还和器件本身的工艺水平有很大关系。

模拟和数字存算一体技术的差别

可以看到,采用模拟还是数字的技术,也是企业常提到的一点,陈巍介绍,一般跟传感器连接密切的部分,推荐用模拟存算一体的方式,如果计算结构复杂,建议用数字的,因为用模拟结构去做复杂计算,代价比较大,而跟传感器进行结合的时候,模拟计算有它的天然优势。

所以其实更多的还是看场景,比如小算力需求,就是做一个声音识别,或者做一个小规模的图像识别,这时候用模拟比较合适,如果说要做云计算的大算力,计算结构又复杂,目前看采用数字方式的多些。

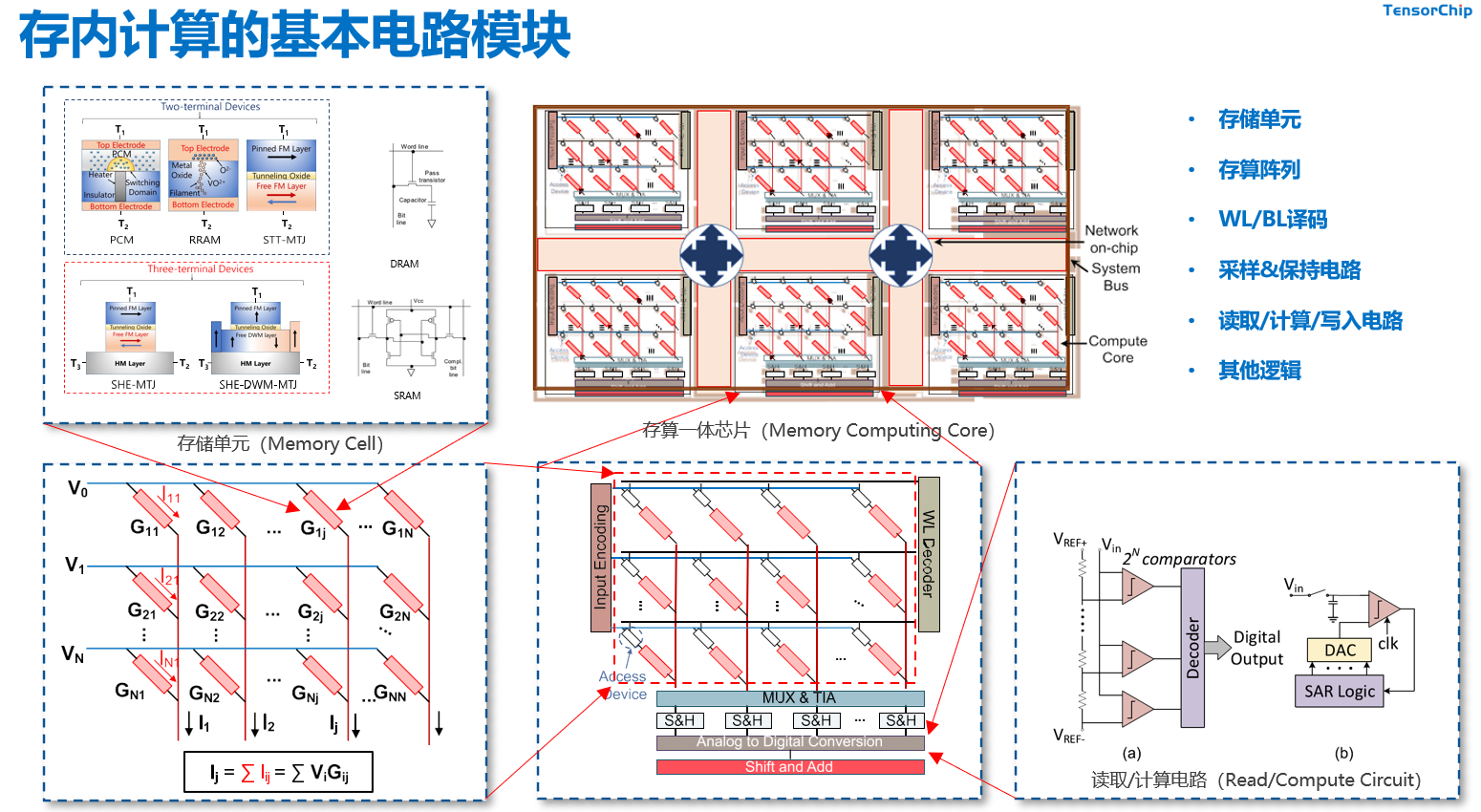

上图是一个存算一体的阵列,比如忆阻器,里面存入矩阵系数,或者叫权重,然后输入数据,也就是输入不同的电压,根据欧姆定律,就会产生不同的电流,每个电流汇聚在一起,即相当于是电流加和(基尔霍夫定理),就完成了一个乘积累加运算,这是模拟电路完成深度学习等各种计算的基本思路。

简单的理解,数字的方式就是把不同的模拟单元分离开,原来模拟电路,相当于是一个单元存一个模拟数值,可能是几位的,比如8位、或4位位宽,如果变成数字的方式,相当于一个单元存入一个数值,是一个位宽的。这样就很明显,模拟的好处是存储密度更高,但没法直接做复杂计算,数字电路离散性会更好,更灵活,可以直接做复杂运算。

存算一体技术的挑战和未来

目前而言,存算一体的发展还存在一些挑战,陈巍谈到两点:一是生态建设,尽管存算一体这个概念并不是特别新,但是真正进入实用阶段的时间还比较短,特别是通用的编译生态环境还没有完全成熟,这样它在落地上就会存在一些适配要求,因为客户对生态都是有要求的,因此急需建立存算一体的生态。

二是如何更好的满足客户的需求,这也是整个AI芯片落地需要解决的一个问题,企业需要更多从客户的需求角度去设计产品,对于客户来说,可能有很多计算场景,它其实不单是需要一个AI技术,还需要其他一些复合的计算类型,比如语音识别场景,它除了AI计算需求之后,还需要语音降噪的算法,这时候就需要根据客户的需求进行特定场景的优化。

存算一体就技术的未来会怎样?从两个阶段来看,陈巍认为,目前基本都处于一个市场开拓期,很多客户还没有完全意识到存算一体的优势和价值,不过如果市场能够出现一个很有影响力的厂商,来证明存算一体芯片,比传统冯诺伊曼架构AI芯片能力更强,那么很快就会有很大的突破,预计这样的突破在近期就会发生。

从远期来看,存算一体会和GPU、CPU技术有很好的结合,成为CPU、GPU、DPU,或者是其他各种AI芯片的计算核心,相当于现有的存算一体技术会给GPU或者CPU赋能,成为现有技术的计算核心。

从商用角度来看,目前国内存算一体芯片至少有两家量产,估计今年会有很多都可以开始商用,目前已落地的商用还主要是在端侧可穿戴设备等领域,一些语音识别,小的视觉模型场景集中。

在自动驾驶和云计算领域,云计算领域的商用预计快一点,估计明后年开始就有产品可以逐步进入中国互联网大厂,自动驾驶领域的商用时间会比较长,因为自动驾驶从架构设计到最后大批量装车,一般需要五年时间,如果前面两年已经完成了设计、流片,大约还要三年的适配和量产测试时间才能实现大批量落地应用。

-

存算一体技术发展现状和未来趋势电子发烧友网官方 2023-04-25

-

存算一体大算力AI芯片将逐渐走向落地应用2022-05-31 6591

-

比存算一体更进一步,“感存算一体化”前景如何?2022-06-08 7680

-

2PFLOPS,存算一体迎来新的卷王2022-08-29 4652

-

2023年存算一体是芯片设计的技术趋势2023-01-13 3381

-

关于存算一体,我们和ChatGPT聊了聊2023-02-09 2784

-

特斯拉的下一代AI芯片:存算一体2023-03-09 3487

-

浅谈存算一体技术的发展路线2023-06-20 3977

-

ChatGPT开启大模型“军备赛”,存算一体开启算力新篇章2023-07-06 844

-

如何选择存储器类型 存算一体芯片发展趋势2023-09-06 1857

-

存算一体芯片的技术壁垒2023-09-22 2681

-

苹芯亮相ESWEEK,探索存算一体技术新思路2023-09-23 1597

-

存算一体芯片新突破!清华大学研制出首颗存算一体芯片2023-10-11 2170

-

探索存内计算—基于 SRAM 的存内计算与基于 MRAM 的存算一体的探究2024-05-16 5616

-

一文看懂“存算一体”2025-08-18 1655

全部0条评论

快来发表一下你的评论吧 !