基于FPGA的信号发生器系统结构分析

描述

基于运用EDA技术,以FPGA器件为核心,用Verilog HDL硬件描述语言来设计各个功能模块,采用DDS直接数字频率合成技术设计信号发生器,通过CPU控制每个采样点的输出间隔来控制输出波形的频率,改变波形存储器中的波形数据来产生任意波形。

0 引言

信号发生器应用非常广泛,包括通信、测量、控制、雷达还有教学等邻域,是不可或缺的工具。随着科学技术的不断发展,信号发生器的设计方法越来越多,其设计技术也越来越先进。传统的信号源种类多样,但大多是采用专用芯片或单片机或模拟电路,不但具有成本高、控制方式不灵活、波形种类少等特点不能满足使用者的要求,而且其外围电路也过于复杂,应用起来效果不尽人意。

随着FPGA(Field Programmable Gate Array)技术的引入,微电子技术的突飞猛进,在信号发生的领地得到了极大的拓展,技术手段呈现快速发展的势头,应用更加广泛和灵活,特别是其在信号发生器上的良好运用得到了充分的体现,有效解决了传统信号发生器带来的模式单一、运行繁杂等一系列问题。

由于以上原因本设计提出以基于EDA技术的FPGA器件作为主控芯片,依据DDS直接数字频率合成技术,提出了一种比较简单的信号发生器设计方法。利用Quartus II软件结合VerilogHDL硬件描述语言进行系统编程,经过调试后下载到本设计中的FPGA器件EP1C3T100C8N中,通过实验验证表明,该信号发生器可以产生正弦波、方波、三角波,信号频率范围在0.02~1 MHz。

1信号发生器系统结构

1.1 系统总体结构

一个基于FPGA的DDS信号发生器,可以生成标准的正弦波、方波、三角波等常用波形。

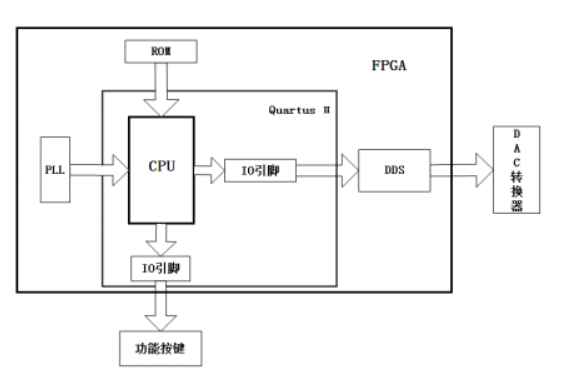

在FPGA完成DDS的功能,通过Quartus II实现按键控制,系统结构框图如图1-1所示。

图1-1 系统结构框图

图1-1所示的是整个系统的结构图,下面对图中所涉及的一些功能部分进行简要的说明。

a.PLL部分:此部分为系统锁相环,功能是为整个系统提供工作时钟,并且在后面控制输出波形的频率提供一个基准频率。

b.ROM部分:此部分是存储波形数据的查找表,是实现DDS信号发生器的必要工具,通过改变ROM查找表内的数据就能改变输出波形。

c.DDS部分:此部分是通过代码实现的,是本设计的关键所在,它的作用是输出数字信号给后面的DAC转换器,是实现设计要求的核心部分。

d.DAC转换器部分:此部分是将系统输出的数字量转换成模拟量并输出,把前面的DDS定义为本系统的软件核心,而DAC转换器则是本系统的硬件核心部分。

e.功能按键:这部分的作用是提供给用户所使用的,用以控制和改变输出波形的形式以及输出频率。

1.2 FPGA基本性能与结构

微电子技术在不断进步发展的同时,可编程逻辑器件得到了飞速的发展,相比于门阵列和其他ASIC(Application Specific Integrated Circuit),FPGA拥有灵活的体系结构和逻辑单元、同时还兼有集成度高和适用范围宽、研发单位时间短,成本低廉、选用的开发工具比较领先、能够实时在线检验等优点。

FPGA器件组成十分复杂,内部拥有大量逻辑宏单元。依靠FPGA器件完成不同的功能需要配置好内部的逻辑宏单元,将这些不同的逻辑宏单元合成不同的硬件结构,以此进一步地构成各种各样的电子系统。FPGA拥有无可比拟的一大优势便是其硬件重构具有很高的灵活性,借助这一优势设计者可以使用硬件描述语言(VHDL、Verilog等)在FPGA中实现所描述的电路。

本设计所使用的是Cyclone系列中的EP1C3T100C8N,Cyclone系列器件是ALTERA公司的一款成本低、高性价比的FPGA器件,它的结构和工作原理在FPGA器件中具有典型性。

Cyclone器件主要由逻辑阵列块LAB、嵌入式存储器块、I/O单元、嵌入式硬件乘法器和PLL等模块构成,在各个模块之间存在着丰富的互连线和时钟网络。Cyclone器件中所含的嵌入式存储器可以通过多种连线与可编程资源实现连接和大大增强了FPGA的性能,扩大了FPGA的应用范围。

1.3 DDS基本原理

DDS(Direct Digital Synthesizer),它具备了以往相关技术所不具备的许多特点,它的频率分辨率较高,这保证了它在运行过程中能够进行快速的频率转换,与此同时它还能保持住相位的稳定性和连续性,因此更加容易获得信号频率、相位变化以及震荡幅度调制的数字控制。下面以正弦波信号发生器为例说明。

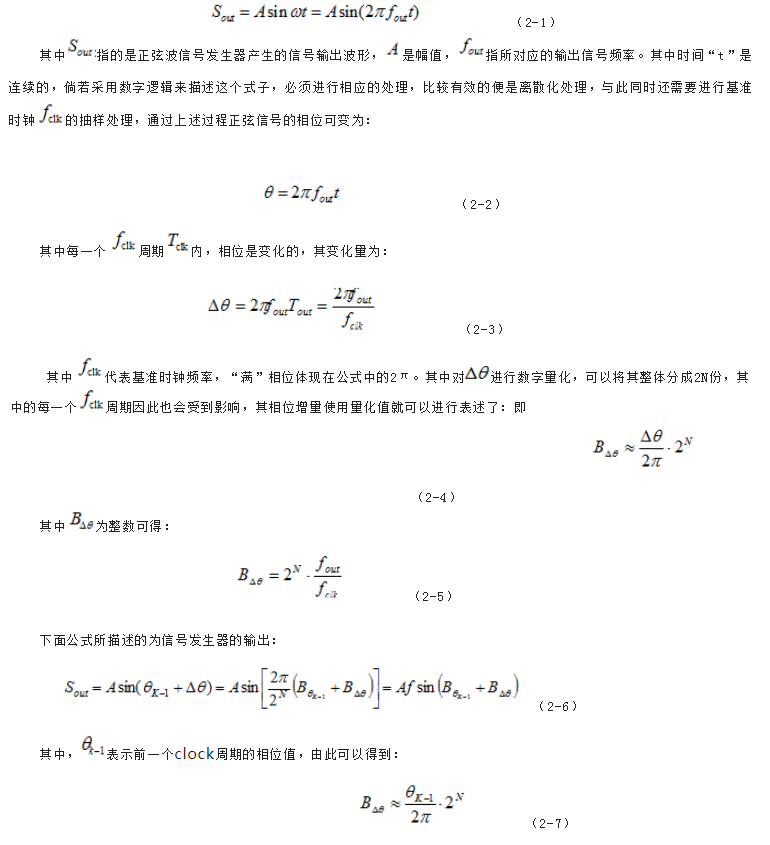

通过上面的步骤原理,可以借助于DDS直接数字合成技术设计并且实现所需要的数控频率合成器。DDS直接数字合成器是用数字控制方式生成所要求的信号频率、相位变化以及震荡幅度等等的正弦波,同时还可以对其进行有效地控制,典型的DDS直接数字频率合成器由许多不可或缺的部分组成,有相位调制器、相位累加器、ROM正弦查找表和D/A数模转换构成,其结构如图1-2所示。

2 系统硬件与软件的设计

2.1 锁相环设计

锁相环(phase locked loop),顾名思义,就是锁定相位的环路。锁相环(PLL)能提供先进的时钟管理能力,例如频率合成、可编程相移、可编程占空比、时钟倍频、分频等完整的时钟管理方案。在本设计中除了是给整个系统提供工作时钟信号,还有一个非常重要的作用,决定了本设计最终输出波形的频率大小,以及频率分辨率。

2.2 ROM设计

本设计的最终结果得到正弦、方波、三角波的输出信号,这个过程是通过将数字量通过DAC转换器不断的转换来完成。因此需要事先将这些波形的的数字量数据存在ROM模块中,以便系统读取波形数据。通过定制波形数据文件来设计出需要的正弦波ROM模块、方波ROM模块和三角波ROM模块。

2.3 D/A数模转换电路

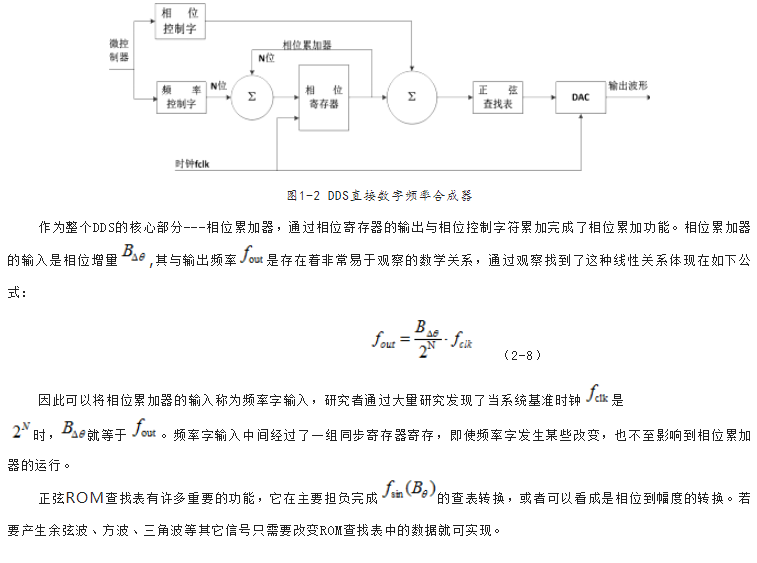

采用非常普遍的8位D/A转换器DAC0832作为数模转换芯片。其转换时间为1us,工作电压为+5V~+15V,基准电压为+15V。它主要由两个8位寄存器和一个8位D/A转换器组成。

图2-1 低速DAC0832数模转换电路

2.4 电源电路设计

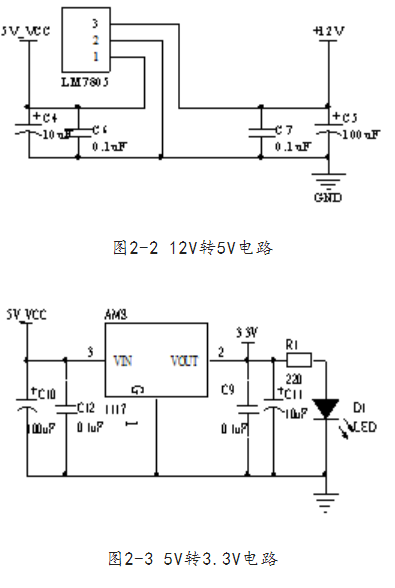

由于系统中各个模块用到的电压不同,所以就需要对电压进行转换。外接12V电源,通过转换电路来实现各个系统所需要的电压,转换电路如下图所示。

2.5软件设计

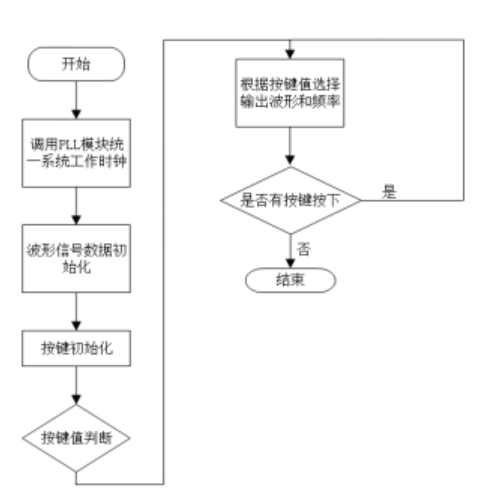

本设计通过Quartus II软件对FPGA主控进行编程配置,实现了用按键控制输出的波形和频率,程序流程图如图2-4所示。

图2-4 程序流程图

3 误差分析

3.1相位截断误差分析

本设计相位累加器设定为32位,正弦表数据为8位,因此在ROM查找表里的容量为232×8=34,359,738,368(bits),在理论上这可以获得精细的频率分辨率,但是这么大容量的数据却很难实现。所以,在本设计中的DDS中采用了相位截断法,只用了相位累加器输出的高10位作为地址对ROM查找表进行查表,其他低位的地址就简单的舍弃了。查表时相位值就会出现误差,使得最后输出波形的幅度值产生误差,就会有很多的杂散信号存在。

3.2电源噪声误差

由于电源部分存在多种电压值,相互间有一定的干扰,会造成输出波形一定的失真。因此对电源的稳定性有更高的要求,可以对数字地和模拟地隔开,降低对输出波形的影响。

3.3后级运放误差分析

数字量经数模转换器转换后信号经过集成运放放大后输出,会有一定的失真。因为集成运放自身会存在一些不可避免的因素,如:输入电压失调,输入电流失调、增益带宽积、上长速度限制。这会导致,当输入较高的频率时,产生相位失真。虽然这些误差是系统自身的,不可避免,但是只要通过给予合适的频率控制字,相位累加器位数、查找表地址位数以及控制好系统时钟频率和尽量使用高品质的电源,尽量提高滤波器的性能,输出的波形还是能够很好的满足使用者的需要。

4 结论

本设计提出了一种基于FPGA信号发生器的设计方法,以Quartus II为软件开发平台,以EP1C3T100C8N器件为硬件平台,采用Verilog HDL硬件描述语言进行编程,将DDS直接频率合成技术实现在FPGA器件上,通过数模转换电路,将系统输出的数字信号转换为模拟信号,实现信号频率范围在0.02~1MHz的正弦波、方波和三角波的产生,并且可以通过按键对正弦波、方波和三角波进行切换。

参考文献:

[1] 阮围.基于 FPGA 的 DDS 设计[D].成都:成都理工大学,2011.

[2] 陈科,叶建芳,马三涵.基于DDS+PLL技术频率合成器的设计与实现[J].研究与开发, 2010,29(4):43~47.

[3] 韩军功.基于 DDS 的任意波形发生器的研制[D].西安:西安电子科技大学,2002.

[4] 潘松,黄继业.EDA与VHDL语言[M].科学出版社,2005:57—68.

[5] 张志刚.FPGA与SOPC设计教程—DE2实践[M].西安电子科技大学出版社.2007:30~38.

-

羊羊羊嘤嘤嘤

2022-06-24

0 回复 举报请问有代码吗 收起回复

羊羊羊嘤嘤嘤

2022-06-24

0 回复 举报请问有代码吗 收起回复

-

如何利用FPGA设计DDS信号发生器?2021-04-09 1746

-

怎么实现基于FPGA+DDS的正弦信号发生器的设计?2021-05-11 1709

-

怎么实现信号发生器系统的FPGA设计?2021-09-30 2310

-

基于FPGA 的数字移相信号发生器设计2009-12-18 467

-

基于FPGA数字移相信号发生器设计2010-07-21 993

-

基于FPGA的信号发生器设计2011-09-26 9146

-

基于FPGA的正弦信号发生器2015-10-30 651

-

iBoard教程之(dds信号发生器)任意波发生器硬件电路分析2017-10-29 1406

-

FPGA和51单片机信号发生器设计2017-10-31 1090

-

基于FPGA和PWM的多路信号发生器设计2017-11-18 7540

-

基于FPGA的DDS信号发生器设计方案解析2017-12-04 2146

-

基于fpga实现信号发生器2018-04-20 1506

-

基于FPGA的信号发生器系统结构分析2023-04-14 1867

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 729

-

文氏桥信号发生器的工作原理和结构2024-09-25 2270

全部0条评论

快来发表一下你的评论吧 !