FPGA的虚拟时钟用于什么地方?

描述

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay 0.5 -clock clkA [get_ports A]

set_output_delay 1 -clock clkB [get_ports B]

其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

- 外部IO的参考时钟并不是设计中的时钟

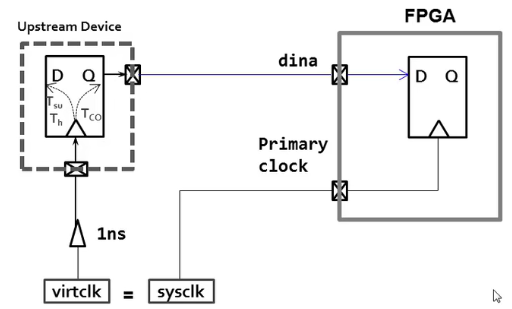

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virtclk -period 10

set_clock_latency -source 1 [get_clock virtclk]

set_input_delay -clock virtclk -max 4 [get_ports dina]

set_input_delay -clock virtclk -min 2 [get_ports dina]

- FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

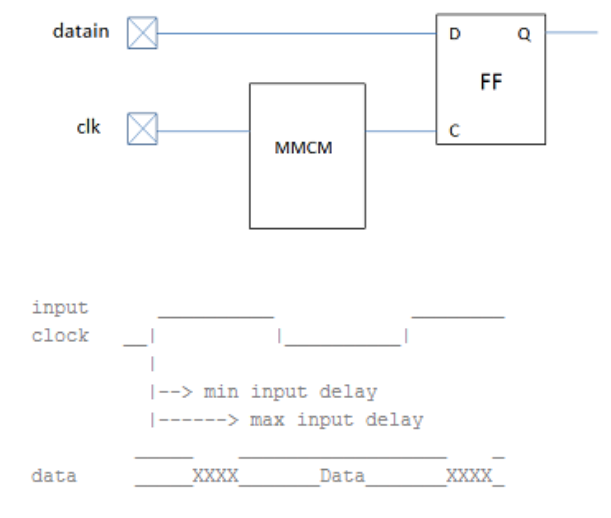

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

image-20211206203529124

image-20211206203529124a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock -period 100.000 -name clk [get_ports clk]

set_input_delay -clock clk -max 2.000 [get_ports datain]

set_input_delay -clock clk -min 1.000 [get_ports datain]

b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock -period 100.000 -name clk [get_ports clk]

create_clock -name clk_port_vclk -period 16.67

set_input_delay -clock clk_port_vclk -max 2 [get_ports datain]

set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]

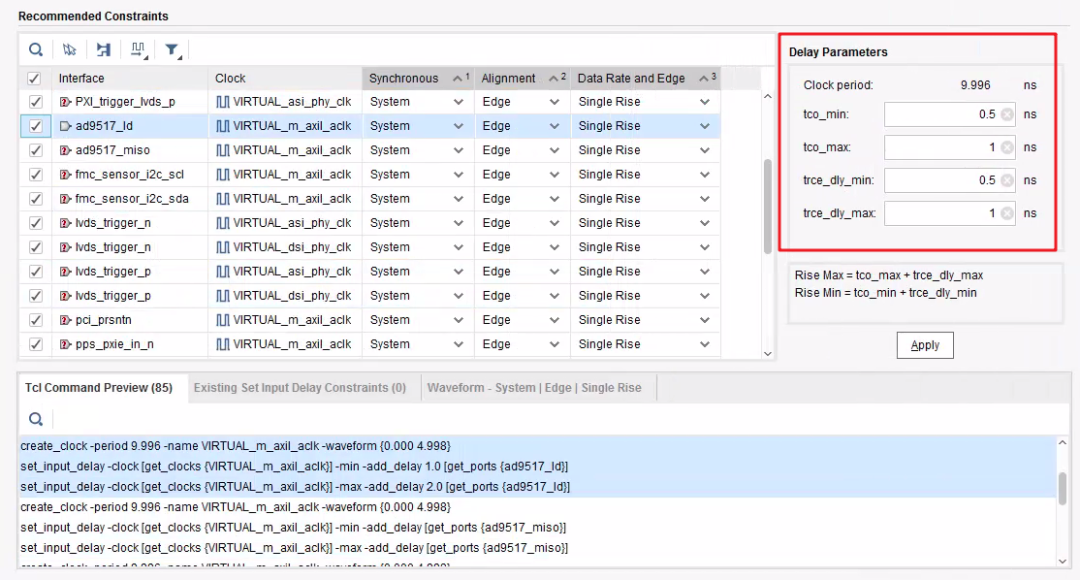

- 在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

这个需求我们可以在Constraints Wizards中指定,简单又方便

image-20211206212729797

image-20211206212729797

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

实时系统和FPGA 两种模式区别在哪里,各自用在什么地方比...?2012-05-14 3052

-

FPGA好学吗?该从什么地方开始着手学习2015-03-05 3915

-

这个控件在选板的什么地方?2016-11-02 3531

-

请问GPRS DTU模块一般用在什么地方?2018-11-27 4187

-

原理图从什么地方着手2019-10-08 2315

-

无线信号放大器是什么呢,它是应用于什么地方呢?2021-04-09 2061

-

请问参考时钟信号是用在什么地方2022-01-05 1682

-

什么是XLR接插件,它运用在什么地方?2009-11-16 1209

-

在Delphi2009中for in循环都能用在什么地方?2018-11-02 1211

-

特种电缆用在什么地方2018-12-17 6568

-

ARP是什么意思?ARP是什么协议?ARP协议用于什么地方2020-11-10 21227

-

芯片主要用在什么地方2021-12-22 15962

-

FPGA虚拟时钟的使用方法2022-02-16 4878

-

焊缝跟踪器可用于什么地方2022-09-21 1362

-

时钟Buffer芯片是什么?其作用是啥?它被用在什么地方?2024-01-16 7018

全部0条评论

快来发表一下你的评论吧 !